作為我們關(guān)于儀器發(fā)展的特色部分的一部分,這里有一個關(guān)于直接集成到電路中的芯片儀器的觀點(diǎn)。使用 PCIe 開關(guān)芯片和支持軟件中的集成儀器,確定 PCI Express(PCIe 鏈路是否正確啟動并快速診斷系統(tǒng)問題)現(xiàn)在變得容易得多。

任何從事電子系統(tǒng)業(yè)務(wù)相當(dāng)長的時間的人都已經(jīng)看到了系統(tǒng)設(shè)計(jì)、互連和調(diào)試方式的若干范式轉(zhuǎn)變。一個顯著的變化是并行總線消失,取而代之的是串行化、虛擬化和交換連接。

幾十年前,幾乎電路中的每個節(jié)點(diǎn)都可以用示波器輕松探測。僅在五年前,人們還可以指望一種可用邏輯或協(xié)議分析儀監(jiān)控的并行總線。今天,比單個片上系統(tǒng) (SoC) 更大的系統(tǒng)由多個類似 SoC 的組件組成,這些組件通過高速串行總線互連,可能通過數(shù)據(jù)包交換機(jī)。沒有隱藏在表面貼裝技術(shù)組件下或埋在內(nèi)部 PCB 層中的少數(shù)可見互連跡線無法觸摸,因?yàn)楹ε潞Iぁ?/p>

集成儀表的案例

如果要在幾分鐘到幾小時(而不是幾天到幾周)內(nèi)完全調(diào)試復(fù)雜的系統(tǒng)問題或解決更簡單問題的根本原因,系統(tǒng)互連交換機(jī)現(xiàn)在還必須充當(dāng)邏輯和協(xié)議分析器。交換機(jī)還應(yīng)該能夠評估物理層的信號完整性,以全線速運(yùn)行外部鏈路,并注入各種錯誤以評估系統(tǒng)檢測和從此類錯誤中恢復(fù)的能力。考慮到當(dāng)今系統(tǒng)封裝的高度集成和限制,這些措施是為這些目的連接外部測試設(shè)備所面臨的幾乎無法克服的挑戰(zhàn)所必需的。

PCIe Gen 2 的 5 Gbps 速度給組件開發(fā)人員及其客戶帶來了額外的挑戰(zhàn),而正在開發(fā)的 Gen 3 規(guī)范將加劇這些挑戰(zhàn)。較高的頻率總體上降低了時序和信號裕度,使物理層更容易受到現(xiàn)實(shí)世界傳輸線環(huán)境的非理想性的影響,甚至對微創(chuàng)探測也不利。

為了克服物理層損傷,SERDES 設(shè)計(jì)人員利用了接收均衡的概念。使用均衡,信號完整性眼圖張開僅在均衡器的輸出端才有意義地觀察到,隱藏在組件內(nèi)部。這只能在集成儀器的幫助下完成。

加速產(chǎn)品上線

經(jīng)驗(yàn)豐富且成功的設(shè)計(jì)團(tuán)隊(duì)長期以來實(shí)施的功能使他們能夠調(diào)試產(chǎn)品開發(fā)過程中出現(xiàn)的問題。借助當(dāng)今可用的晶體管密度,設(shè)計(jì)人員可以將邏輯分析功能與關(guān)鍵任務(wù)功能集成在一起,而且通常不會影響成本。即使是查看數(shù)百萬門 ASIC 中邏輯節(jié)點(diǎn)的一小部分的能力,對于快速找到組件或系統(tǒng)級錯誤的根本原因也具有不可估量的價值。

雖然這些高級功能曾經(jīng)僅供工廠使用,但現(xiàn)在通過提供高級界面的軟件向客戶開放。該接口使客戶無需了解電路實(shí)現(xiàn)的詳細(xì)知識以了解結(jié)果,同時保護(hù)制造商的知識產(chǎn)權(quán)。同時,集成分析工具的范圍正在從單個組件的焦點(diǎn)擴(kuò)展到系統(tǒng)范圍的問題。

雖然集成儀器在整個開發(fā)周期中都很有用,但在考慮初始電路板啟動所涉及的問題時,它的價值最容易被理解。當(dāng)一個系統(tǒng)或子系統(tǒng)由圍繞一個中央 PCIe 分組交換機(jī)的多個 SoC 組成時,該交換機(jī)是第一次上電后關(guān)注的焦點(diǎn)。鏈接出來了嗎?信號完整性是否符合預(yù)期和要求?枚舉和后續(xù)配置成功了嗎?數(shù)據(jù)包流模式是否標(biāo)稱?越早回答這些問題,團(tuán)隊(duì)就能越早將墨菲扔給他們的東西歸零,并朝著成功的產(chǎn)品發(fā)布邁進(jìn)。借助由供應(yīng)商提供的支持軟件支持的集成儀器,這些答案很容易獲得。

使用內(nèi)部邏輯分析儀

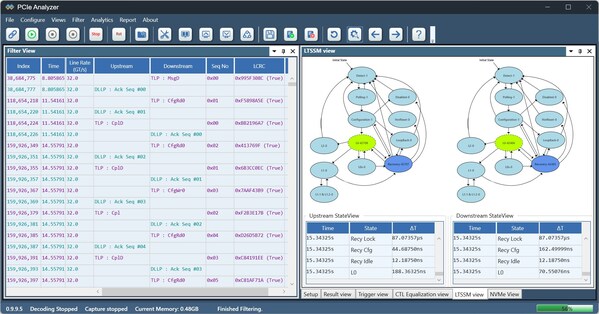

為新板供電時的首要任務(wù)是確定 PCIe 鏈路是否已啟動。PCIe 開關(guān)通常為每個端口提供鏈路狀態(tài)輸出,可控制 LED 以進(jìn)行視覺指示。如果鏈路沒有出現(xiàn),跟蹤 PCIe 規(guī)范中定義的鏈路訓(xùn)練和狀態(tài)狀態(tài)機(jī) (LTSSM) 的轉(zhuǎn)換非常有幫助。

甚至帶有簡單集成邏輯分析儀的交換機(jī)也可以配置為在鏈路訓(xùn)練周期中捕獲端口 LTSSM 到內(nèi)部跟蹤存儲器的每次轉(zhuǎn)換并為其加上時間戳。之后,可以通過 I2C 或 PCIe 讀取軌跡,并借助隨附的軟件進(jìn)行分析。這種跟蹤通常可以快速區(qū)分互操作性問題、制造問題和信號完整性問題。

如果跟蹤 LTSSM 無法確定答案,則可以首先將內(nèi)部邏輯分析儀指向 SERDES、串行到并行轉(zhuǎn)換器、彈性緩沖器、解擾器等的輸出,以嘗試查明故障。

雖然集成邏輯分析儀可以提供深入探究 ASIC 內(nèi)部的能力,但只有那些靠近外部接口或按照行業(yè)標(biāo)準(zhǔn)要求構(gòu)建的寄存器或狀態(tài)機(jī)對最終用戶才有意義。

優(yōu)化鏈路性能

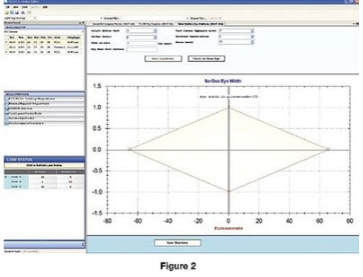

一旦每個鏈路建立起來,就有必要估計(jì)信號完整性的眼圖張開度并對其進(jìn)行優(yōu)化。高級 SERDES 允許借助內(nèi)置自測 (BIST) 功能測量眼圖張開的寬度。這是通過有時使用專利技術(shù)來完成的,該技術(shù)將采樣點(diǎn)從眼睛中心偏移,然后確定這是否會導(dǎo)致誤碼。鏈路處于環(huán)回模式,并使用內(nèi)部誤碼率測試邏輯測試誤碼率。調(diào)試處理器可以逐步設(shè)置 SERDES 均衡器和驅(qū)動強(qiáng)度選項(xiàng),報(bào)告效果最佳的選項(xiàng),甚至將它們燒錄到可選的串行電擦除可編程只讀存儲器 (EEPROM) 中,以便在下一個上電周期自動加載。

可以提供對該測量和參數(shù)優(yōu)化過程提供一定程度自動化的軟件(參見圖 2)。

圖 2

通過將調(diào)試處理器連接到交換機(jī)的 I2C 總線,工程師可以邊帶訪問所有交換機(jī)的內(nèi)部寄存器。開發(fā)人員可以在應(yīng)用程序運(yùn)行時手動查看和戳,以檢查其進(jìn)度或執(zhí)行腳本,將實(shí)際交換機(jī)配置狀態(tài)與預(yù)期狀態(tài)進(jìn)行比較。

調(diào)試處理器可以配置可用的性能監(jiān)視器,然后在應(yīng)用程序運(yùn)行時實(shí)時顯示收集的統(tǒng)計(jì)數(shù)據(jù),以實(shí)時指示其運(yùn)行狀況。純粹為了方便起見,可以通過調(diào)試端口提供對下游設(shè)備、控制和狀態(tài)寄存器的類似訪問。當(dāng)以這種方式使用時,調(diào)試處理器的作用類似于服務(wù)器中使用的管理或服務(wù)處理器,實(shí)際上,它們的功能可以組合起來。

經(jīng)過功能調(diào)試后,壓力測試和錯誤注入是產(chǎn)品開發(fā)的兩個必要環(huán)節(jié)。交換機(jī)的正常數(shù)據(jù)路徑很容易修改為鍛煉器。作為第一步,交換機(jī)留出一部分緩沖存儲器,允許軟件在其中構(gòu)建數(shù)據(jù)包,然后在選定的鏈路上傳輸數(shù)據(jù)包。更高級的實(shí)現(xiàn)包括計(jì)數(shù)、循環(huán)和分支機(jī)制,以支持更復(fù)雜的數(shù)據(jù)包流并將偽隨機(jī)元素添加到錯誤注入中。

將交換機(jī)的某些部分作為練習(xí)器操作時,所涉及的端口不再充當(dāng)交換機(jī)。因此,此功能不像 PCIe 交換機(jī)中的其他開發(fā)加速功能那樣不顯眼。盡管如此,可以執(zhí)行錯誤注入并在高達(dá) x16 Gen 2 鏈路上生成全線速數(shù)據(jù)包流的組件的簡單可用性對產(chǎn)品驗(yàn)證社區(qū)來說是一個巨大的福音。

實(shí)施嵌入式儀器

在 PLX Technology,將這些功能集成到 PCIe 芯片中是出于降低制造成本和促進(jìn)內(nèi)部調(diào)試和驗(yàn)證工作的自私愿望。很快就很明顯,這些功能可能對客戶更有價值,因?yàn)樗梢约铀偎麄兊漠a(chǎn)品開發(fā)過程。由于技術(shù)正在向更高的互連速度發(fā)展,PLX 認(rèn)為集成儀器正迅速變得必不可少,尤其是對于 PCIe 開關(guān)。

實(shí)施 SERDES 眼圖測量功能需要與 SERDES 和 SERDES BIST 知識產(chǎn)權(quán)供應(yīng)商密切合作,然后設(shè)計(jì)團(tuán)隊(duì)努力利用所提供的功能。

實(shí)現(xiàn)片上邏輯分析的設(shè)計(jì)方法需要寄存器傳輸級 (RTL) 工程師提供來自每個主要模塊的關(guān)鍵狀態(tài)的可選探針輸出,其方式與插入驗(yàn)證斷言所需的方式大致相同。這種內(nèi)部標(biāo)準(zhǔn)化允許腳本開發(fā)部分自動化將饋入觸發(fā)邏輯和跟蹤存儲器的探針總線添加到 RTL 層次結(jié)構(gòu)中。標(biāo)準(zhǔn)化還減少了利用這些數(shù)據(jù)并將其中的至少一部分塑造成對最終用戶有用的形式所需的軟件工作量。

隨著技術(shù)的發(fā)展,集成的儀器儀表和支持軟件工具顯示出巨大的潛力并變得更加用戶友好。對于 PCIe 開關(guān)供應(yīng)商和客戶來說,這代表了一個新的和有希望的方向,一個可以消除系統(tǒng)開發(fā)過程中主要的痛苦和延遲來源。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19882瀏覽量

234940 -

嵌入式

+關(guān)注

關(guān)注

5149文章

19651瀏覽量

317181 -

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124321

發(fā)布評論請先 登錄

【沁恒CH585開發(fā)板免費(fèi)試用體驗(yàn)】+品讀老朋友的新產(chǎn)品

PCIe插槽秒變M.2存儲倉!免拆機(jī)維護(hù)神器M.2 NVMe轉(zhuǎn)PCIe 4.0 x4 硬盤抽取盒!#pcie

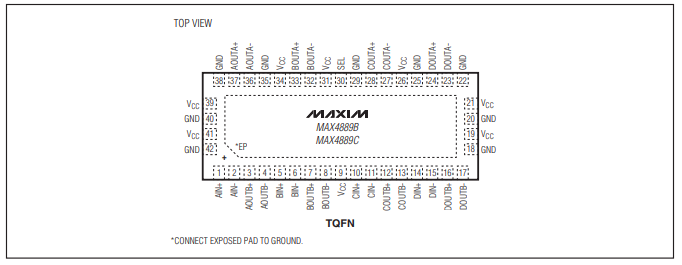

MAX4889B/MAX4889C 2.5/5.0/8.0Gbps PCIe無源開關(guān)技術(shù)手冊

nvme IP開發(fā)之PCIe下

nvme IP開發(fā)之PCIe上

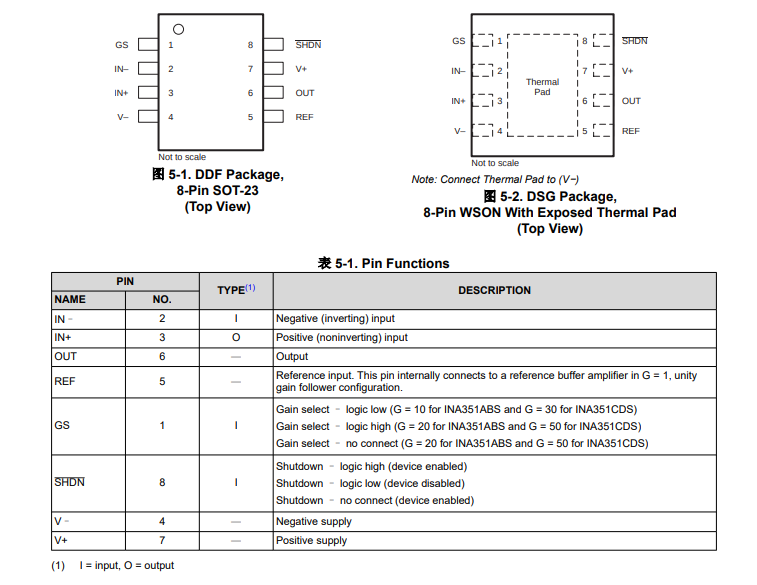

INA351 具有集成基準(zhǔn)緩沖器的微型 、低功耗、儀表放大器技術(shù)手冊

【高清視頻案例分享】CameraLink接口的PCIe采集卡 ,基于FPGA開發(fā)平臺

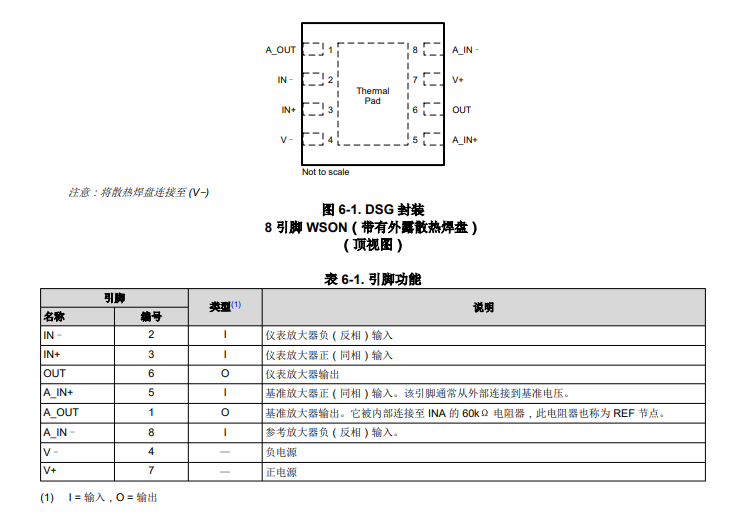

INA351A 具有集成基準(zhǔn)放大器的低功耗儀表放大器技術(shù)手冊

SiP藍(lán)牙芯片在項(xiàng)目開發(fā)及應(yīng)用中具有什么優(yōu)勢?

慧榮正在開發(fā)4nm PCIe 6.0 SSD主控芯片

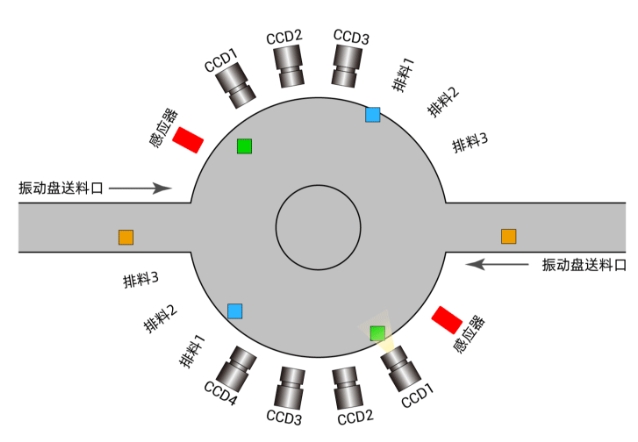

PCIe實(shí)時運(yùn)動控制卡的雙盤視覺篩選機(jī)上位機(jī)開發(fā)應(yīng)用

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

AM625SIP處理器如何通過集成LPDDR4加快開發(fā)

Prodigy Technovations推出功能強(qiáng)大的PCIe Gen5協(xié)議分析儀

具有集成儀表的PCIe開關(guān)可加快產(chǎn)品開發(fā)

具有集成儀表的PCIe開關(guān)可加快產(chǎn)品開發(fā)

評論