可重構性——在系統部署后改變系統功能的能力——不僅可以幫助設計人員對最后一刻的設計變更做出反應,還可以讓他們在實施之前對想法進行原型設計,并在現場升級設計。在當今瞬息萬變的環境中,這種能力提供了巨大的競爭優勢,并且通常每瓦系統功率可以完成更多的計算。Tom 探討了 FPGA 設計的當前趨勢如何提供更大的靈活性并滿足即使是最苛刻的應用程序的要求。

隨著應用程序變得越來越復雜,可重構計算必須不斷發展,以滿足行業不斷變化的需求。靈活性對于滿足不斷變化的客戶需求變得越來越重要,并且要求系統比以往任何時候都更強大。例如,信號處理應用程序必須繼續跟蹤和解釋來自更遠距離的信號,并合并來自多種類型傳感器(如紅外線和紫外線)的數據。

這些應用程序將需要不斷提高的圖像壓縮水平和計算能力以及用于評估數據的增強智能。當然,天氣建模和計算化學等傳統性能計算應用也需要更多的計算能力。而且,隨著電源和冷卻問題越來越受到關注,圖形處理單元 (GPU) 所需的 100 W 或更多功率在傳統計算中心可能會出現問題,而在包括衛星和無人駕駛飛機在內的其他應用中可能會令人望而卻步。

FPGA 通過提供可與新興標準保持同步的靈活平臺,直接滿足可重新配置的計算需求。知識產權 (IP) 功能和可配置處理器加快了開發速度,而強大的新軟件工具可減少延遲、增加帶寬并減少門的使用。FPGA 實現了所有這一切,在低功耗運行和散熱方面比其替代品具有顯著優勢。

提升性能的 IP 內核

今天,實現可重構計算的最簡單途徑之一是使用 IP 內核,例如可配置處理器,它可以提供可調整的緩存大小、乘法器、除法器、硬邏輯和自定義指令。一些可配置處理器還支持可自動轉換為硬件的加速器,從而提高生產力并顯著提高嵌入式軟件性能。設計人員可以簡單地添加外圍設備或處理器來創建適合他們需求的精確設計。

這些處理器具有過時證明的額外好處;即使設備過時,設計也可以移植到新的芯片上,從而保護設計人員對軟件的投資。然而,這些可配置的處理器從來都不是用來處理大量計算的。它們通常作為控制器為可重構計算應用程序增加價值,協調具有專用計算功能的專用塊之間的交互。

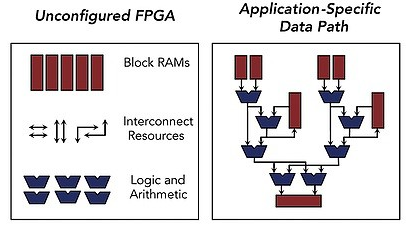

其他 IP 的開發正在進行中,例如可擴展、可配置處理和高性能計算架構,可滿足定制數據路徑、協議處理、數字信號處理和圖像處理的需求(參見圖 1)。這些功能允許工程師用定制的管道和并行數據路徑代替順序計算,以獲得更高的性能和效率。軟向量處理器目前也在開發中。

圖1

通過并行加速

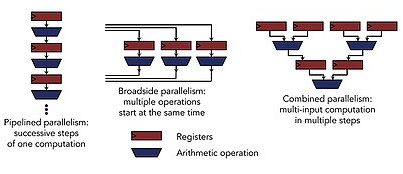

此外,與其他解決方案相比,FPGA 現在提供了更多的計算能力,而功耗卻大大降低。可重構計算的關鍵是從傳統的計算算法模型轉變為在可配置計算結構中空間分布算法。速度不是來自快速連續執行許多操作,而是來自使用流水線、寬邊并行或兩者的組合并行執行操作(參見圖 2)。FPGA 還允許設計人員定制流水線和內存訪問模型,這些功能是 GPU 所不具備的。較高的帶寬是通信應用中流數據的理想選擇。

圖 2

FPGA 加速器中的應用程序通常運行在 100 MHz 附近,但通過更多的設計工作可以達到更高的時鐘速度。通過優化,FPGA 可以為利用其優勢的應用實現令人印象深刻的加速,包括:

1000多個獨立的硬件乘法器和算術單元的細粒度并行,所有這些都可以并發運行

低計算開銷,索引和提取可以流水線化,操作數可以存儲在獨立的內存庫中,終止測試可以與算術函數并行進行

具有 1,000 多個獨立可尋址 RAM 緩沖區的內存并發性

快速、細粒度的通信以及以全芯片速度運行的片上通信,通常只有幾個周期的延遲

浮點編譯器提高效率

除了硬件,新工具現在解決了在設計中使用可編程邏輯的一些挑戰。FPGA 始終在數據流架構中提供幾乎無限的靈活性,因此提供了一種理想的方法來實現算術功能或通過卸載無法在處理器中最佳實現的數據路徑來加速系統。然而,FPGA 以前在實現浮點運算的復雜性和精度方面遇到了困難,特別是對于雙精度應用。

已開發出一種新的浮點編譯器,可有效地將浮點數據路徑映射到通用 FPGA 架構。這種浮點編譯器通過將數據路徑的大子部分融合在一起、對類似操作進行聚類以及優化連續運算符集群之間的接口來提高效率。

這允許多個精度(整數、單精度和雙精度)存在于單個數據路徑中,從而使通用 FPGA 與簡單的基于組件的系統相比具有顯著的效率優勢。通用 FPGA 可在邏輯利用率上節省 50% 的典型邏輯,并類似地減少延遲,因此可以輕松支持浮點功能,并靈活地實現更廣泛的運算符混合(例如加法器/減法器與乘法器的更大比例) ,同時保持處理能力以支持使用數據路徑的應用程序。

可重構的優勢

在當今技術和客戶需求瞬息萬變的世界中,在現場部署設計后增強功能的能力至關重要。借助最新的技術進步,包括更高的計算能力、更高的帶寬、更低的延遲和更少的門使用,加上持續的雙精度 GFLOPS/W,目前最高可達 1.5,可重新配置使用 FPGA 進行計算可以在競爭之前進入市場,并最終確保產品的成功。

審核編輯:郭婷

-

傳感器

+關注

關注

2565文章

52935瀏覽量

766911 -

處理器

+關注

關注

68文章

19882瀏覽量

234964 -

FPGA

+關注

關注

1645文章

22034瀏覽量

618004

發布評論請先 登錄

FPGA設計滿足可重新配置的計算需求

FPGA設計滿足可重新配置的計算需求

評論