本文將介紹一些在設計 DC-DC 降壓轉換器時可以使用的一般技巧。

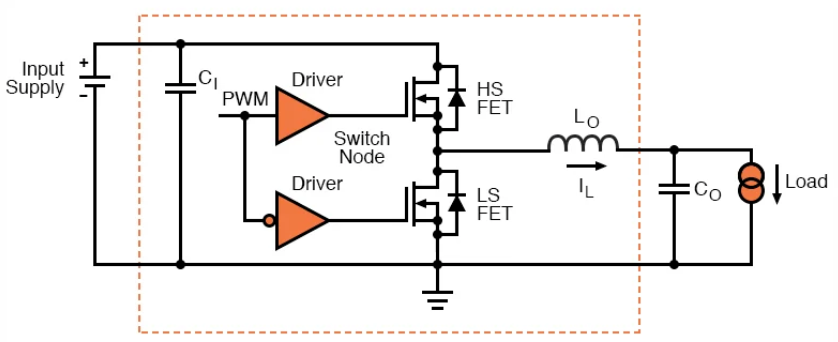

基本 DC-DC 降壓轉換器電路在開始之前,讓我們回顧一下 DC-DC 降壓轉換器的電路:

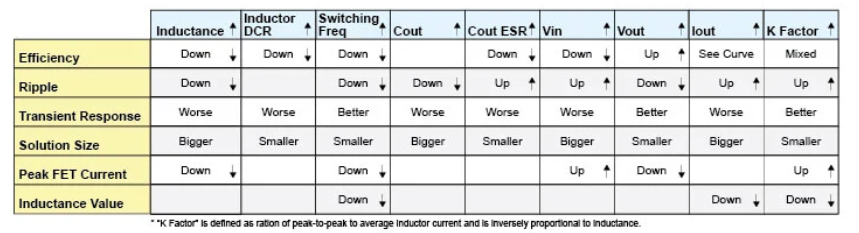

降壓轉換器中的組件權衡

了解您面臨的設計權衡非常重要。

為了幫助你,我開發了一個降壓設計中“什么影響什么”的矩陣:

喬治·比納(George Biner)的“什么影響什么”。

主要的權衡是選擇電感(與 k 因子成反比,即峰峰值與平均電感電流之比)、輸出電容和開關頻率,以實現足夠的紋波和瞬態響應。

設計人員絕對應該利用穩壓器 IC 制造商的設計工具來確定元件值并進行電路仿真。

了解您的電容器

確保電容器在工作頻率下具有電容,并知道它們的自諧振頻率在哪里。

陶瓷在寬頻率范圍內性能良好,但電容相對較低。通常,一種電容類型不能覆蓋整個頻率范圍,必須并聯使用兩種類型(例如陶瓷和電解),陶瓷更靠近電路。

電容器也會因施加偏置電壓而損失大量額定電容。

信任但驗證:芯片和組件

在第三方制造的帶有微小、未標記組件的 PCB 上,您必須相信安裝了正確組件的電路板填充器。確保您的信任沒有放錯地方。

如果您已將芯片發送給制造商進行故障分析,請不要等待結果。這些天的芯片質量水平非常高,芯片不太可能對您不利。這種分析也需要一些時間。同時,您可能會發現真正的問題。

如果您使用的是數字芯片,請驗證您更改的設置是否已實際寫入芯片,而不僅僅是 GUI。

考慮測試和測量

未經示波器驗證,請勿假設直流電壓穩定。

測量紋波的過程有很多——執行它的適當設備很昂貴。雖然最好使用花哨的差分探頭,但您也可以使用單端探頭——只要確保地線非常短并且連接在V out旁邊即可。

使用 1x 探針(您可以自己構建)。10x 探頭不會有您需要的靈敏度。

高頻尖峰通過電感器的寄生電容耦合到輸出端。您可能需要減慢上部 MOSFET 的開啟速度,以減少底部 MOSFET 的振鈴或dv/dt雜散開啟,盡管這會降低效率。

分析您的輸入電容

輸入電容比輸出電容了解得少,但可能需要它來滿足輸入噪聲要求并確保您的電路不會缺電流。

輸入電容器具有較大的紋波電流,其峰值在 50% 占空比時會產生熱量并縮短電容器的使用壽命。確保電流在他們的規格范圍內。當您添加更多并行C in時,有一個基本的權衡,因為越來越低的 ESR 將導致更高的紋波電流和更多的熱量。要真正降低輸入紋波電流,您可能需要一個串聯電感。

隨著占空比越高,從C in汲取的電流也越高,從而導致芯片上更多的V in下降——如果V in已經很低,因為你更接近于運行到更低的V in限制,這將變得很重要——你可能需要在這些情況下添加C。

提前考慮 PCB 布局

了解電流路徑的基礎知識和大電流回路的最小化。學校教了很多關于正向電路路徑的知識,但沒有關于返回路徑,它們顯示為完美的接地符號!進行布局,使返回電流可以遵循其自然路徑(最小化環路)。

保持低電源路徑電感。通過它們的脈沖電流會產生電壓尖峰和輻射 EMI。大功率過孔是可以的,但應該了解它們的特性。

了解電路節點的阻抗水平并相應地保護它們。例如,誤差放大器的求和節點具有高阻抗且對噪聲敏感——將其隔離并使其變小。

尊重模擬地、數字地和電源地之間的劃分,并提供自然的返回路徑。星形接地可避免通過與敏感的低電平電路共享的接地路徑運行大的脈沖電流。

了解(并尊重)你的極限

確保遵守熱降額曲線——在高溫下,最大電流和功耗總是從“標題”值降低。

確保引腳電壓永遠不會超出操作規范,無論是引腳對地還是引腳對引腳。例如,在其引腳對地規范內激勵一個引腳,但違反其引腳對引腳規范到另一個引腳可能會燒毀芯片。

請注意控制器芯片的最小/最大可控開啟和關閉時間,并確保您沒有將其操作得太接近其限制。

-

電容器

+關注

關注

64文章

6709瀏覽量

102890 -

pcb

+關注

關注

4368文章

23489瀏覽量

409617 -

DC-DC

+關注

關注

30文章

2280瀏覽量

83911 -

降壓轉換器

+關注

關注

7文章

1898瀏覽量

87371

發布評論請先 登錄

DC-DC轉換器電路圖 Boost升壓型DC-DC轉換器的工作原理

DC-DC降壓轉換器中的組件權衡

DC-DC降壓轉換器中的組件權衡

評論