明德揚整理了的同學們提出的問題,本帖將所有問題進行一個匯總,大家可以從這里找到您想要學習或疑惑的問題,然后進入對應的匯總貼進行學習。為方便您隨時找到答案,敬請您收藏本網址!MDY專題課產品交流【匯總貼】_FPGA-明德揚/專業FPGA解決方案專家 (mdy-edu.com)如果同學們的問題我們帖子里面沒有的請第一時間聯系我:易老師,我們對新問題進行補充!

十一、就業班項目-精密儀器項目(JESD204B)

【問題11.1】JESD204B專題課有交流群嗎?

答:購買此課后,均加入MDY的專題課交流群。

【問題11.2】交流群會解答哪方面的內容?

答: 購買此課程的同學,需要有一定的FPGA基礎,如一定的設計能力、驗證能力和調試能力。

本課程的交流群,將不會詳細解答基礎問題,例如VERILOG語法;自己修改的代碼,如果出錯,請自行定位。對于協議、架構等,如有問題,MDY都會詳細解答。

【問題11.3】FPGA的JESD204B參考文檔是PG066嗎?

答:是的。

【問題11.4】 AD9144的同步信號已經拉高了,這說明已經配置成功了?

答:要使用AD9144成功,可以依次檢查以下AD9144的幾個寄存器。

地址OX470:該寄存器用于表示LANE有沒有檢測到K28.5同步字。如果說FPGA管腳配置錯誤、時鐘有問題、LANE速率有問題 (例如雙方配置的LANE速率不同,一端為2G,另一端為2.5G;或者信號質量不高,傳輸有誤碼等),則讀到的值將不正確。

地址OX471:檢查是否所有的LANE都已經同步。如果地址0X470正確,本寄存器不正確,則可能是速率、時鐘有問題。

地址OX472:檢查checksum,即校驗和是否正確。如果說FPGA和AD9144的參數不同,或者是傳遞有錯誤,則此寄存器值不正確。

地址OX473: 檢查ILAS。如果說此正確,基本上都正確了。

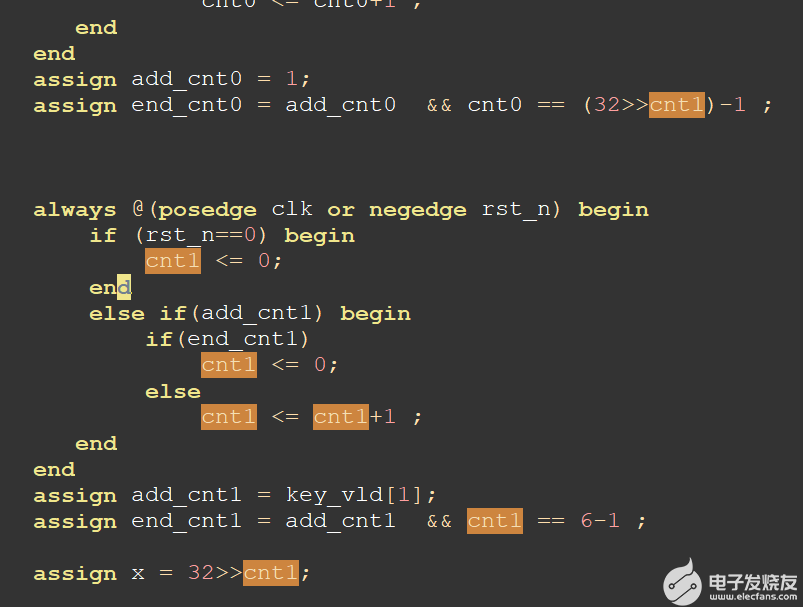

【問題11.5】頂層模塊jest204b_test中,下面的代碼是什么含義?

答: 本工程有一個功能,通過按下按鍵,可以改變信號的頻率。工程一共支持6種頻率,cnt1值為0~5,分別用來表示6種頻率。 上面代碼中的cnt0控制頻率的,其是通過控制同一值重復的次數來達到控制頻率的目的,例如假設某信號值為01234為100M信號頻率, 讓每個點重復一次,即0011223344,信號頻率就變為50M。 cnt0的值根據cnt1來改變,例如當cnt1為0時,cnt0的值為0~31,當cnt1為1時,cnt0的值為0~15,當cnt2為2時,cnt0的值為0~7。

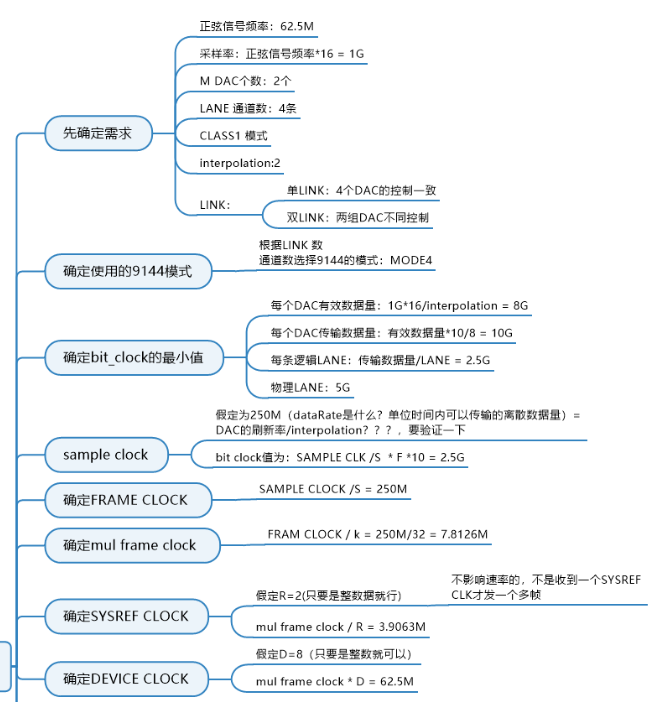

【問題11.6】如果要實現與工程中不同的分辨率和不同的采樣率(即輸出波形的頻率不同、分辨率不同),要怎么做?

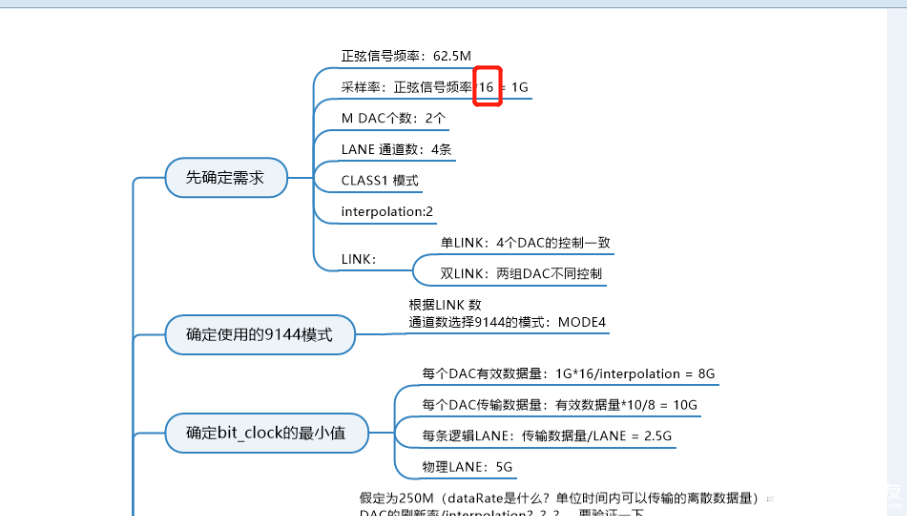

答: 如果要改變波形的頻率,需要涉及到整個系統不同參數的調整,包括用于通信的lane的個數、時鐘頻率、IP核的寄存器配置和AD9144的寄存器配置等等。 具體可以參考視頻中,具體應該按下圖的步驟來分析:

上圖中,依次是確定需求,即您希望的信號頻率、采樣率DAC個數分別是多少,然后據此確定需要多少條LANE;進而確定AD9144的配置;lane的速率;sample時鐘等等。本課程有對應的視頻講解,可以詳細理解。請理解視頻中介紹的思想,從而應用到您自己的項目中。實用建議:建議您在我們提供的案例基礎上,每次改動一點點,看到正確效果后,再做下一下,最終完成最終的目標。

【問題11.7】案例中,插值為2的意義?為什么要插值?

答:插值,顧名思義,就是在兩個數據中間自動插入數據。例如要產生一個波形012345,不插值的情況下,FPGA必須要發送數據012345這幾個數據給AD9144;而在插值為2時,FPGA只需要發送0246數據,然后AD9144自動補充135。本案例中,為什么要使用插值為2,是假設的一種需求情況。

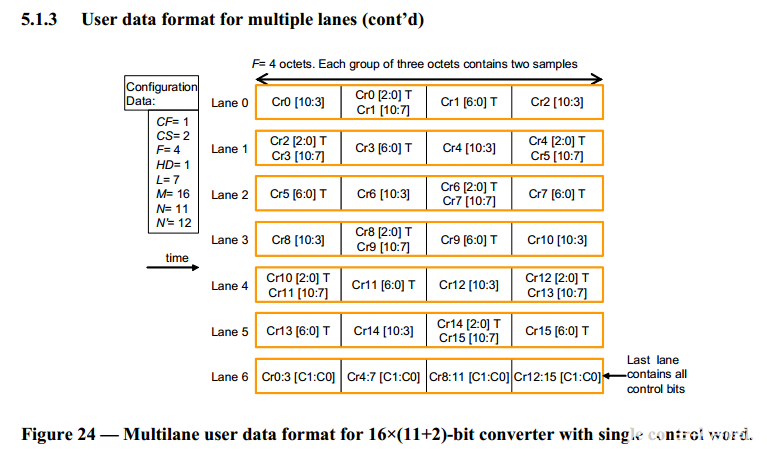

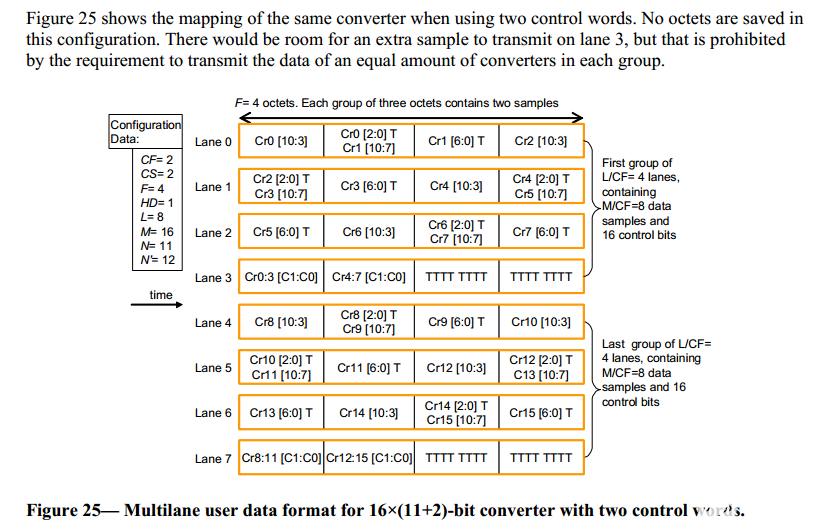

【問題11.8】在文檔《JESD204B協議》中,第52頁的下面兩個圖,為什么這兩者的CF不一致?CS又是什么?

答:CS是指一個SAMPLE中的控制位比特數,上面兩種情況,每個SAMPLE都加了2位的控制比特,即圖中的C1和C0。注意,圖中的“Cr0:3[C1:C0]”,是指Cr0的[C1:C0]+Cr1的[C1:C0]+Cr2的[C1:C0]+Cr3的[C1:C0]。CF是指一個FRAME CLK中的控制字個數,單位為字節。注意,這里的CF的限定條件是一個“FRAME CLK”。一個FRAME CLK,即上圖中的一列數據。從第一個圖可以看出,第一列控制字是Cr0:3[C1:C0],共8比特,所以為CF=1。從第二個圖可以看出,第一列控制字是Cr0:3[C1:C0]和Cr8:11[C1:C0],一列共有16比特,所以CF=2

【問題11.9】在講解需求時,下面的16是什么含義?

答:這里的16,是我們假設一個正弦波由16個采樣點組成,所以由信號頻率*16=采樣頻率。 當然,這里的16假設值,當您的正弦波是由32或者64,或者更大數組成時,當然就不同。我們這里是先確定需求。

【問題11.10】204b配置完了才正常工作還是不配置也能工作,配置完之后會改變工作方式?

答:都是需要配置完才能正常工作的。

【問題11.11】是否應該補充IP核的配置,為什么要那樣配?

答:1. 關于各個參數,如CS F M N等參數,在講解確定需求的視頻中,已經逐個分析出來。總的來說,是看AD9144文檔,看MODE后, 根據MODE所 推薦的參數來配置。

2. 得到上面參數后,請閱讀一下FPGA IP核的寄存器手冊,很簡單的,基本上是各個參數配上去就行了。

3. 配置代碼,可以看代碼解釋視頻,后面補充了。

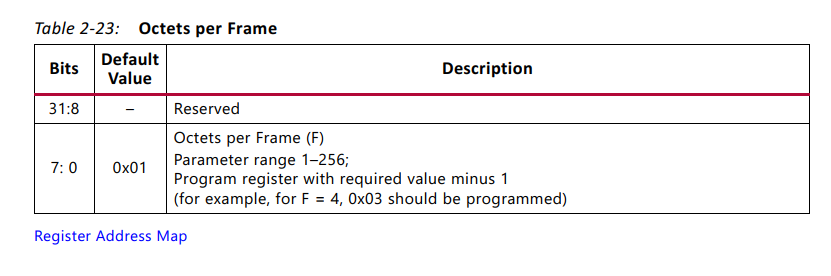

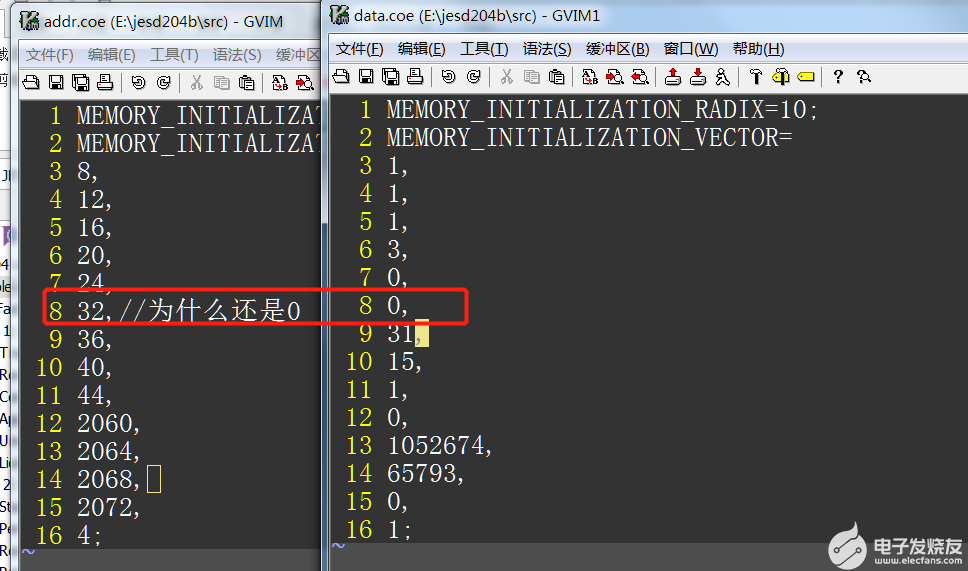

【問題11.12】204b配置文件里面有一個寄存器有疑惑,手冊里面寫的最小是1,但coe配置成0 。

答:寄存器中,“parameter range 1-256”,是指F這個參數的范圍是1-256。但后面有描述,此寄存值的值 = F-1,所以才填為0。

這里描述有些歧義,但可以用這種方法排除:假設寄存器是1-256,那該寄存器是8位的,無法表示256,矛盾。

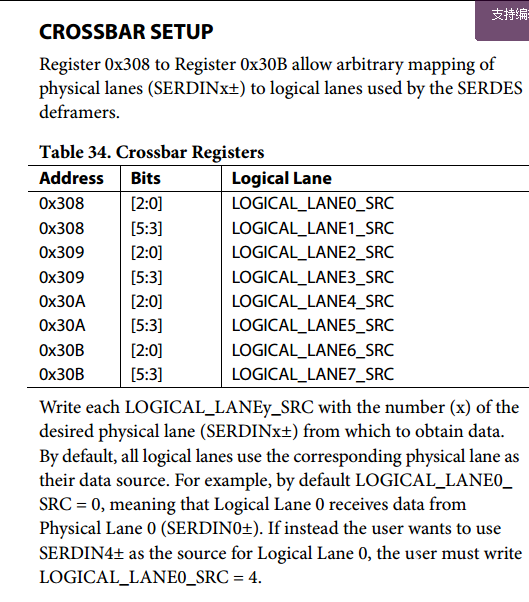

【問題11.13】在AD9144的0X308~0X30B這幾個寄存器,是用來選擇serdin和lan的關系的,這是如何對應的?

答:下面是這幾個寄存器的相關描述。

首先,明確概念,SERDIN0~7指的是AD9144芯片上定義的管腳,是物理的,可以去看管腳圖。LANE0~7,是指內部表示的LANE編號。估計是為了靈活性,LANE0~7不是與SDRDIN0~7不是一個一個對應的,其對應關系是可以配置的,上面幾個寄存器就是起這種作用。例如,LANE0可以與SERDIN0對應,這個時候的0X308[2:0]=0,也可以和SERDIN4對應起來,這個時候0X308[2:0]=4。其次,理解了上面關系后。你可以根據實際情況來配置,例如,本案例中的AD9144子板,它的SERDIN0~3是沒有用的,只使用了SERDIN4~7,這是固定死的。然后內部的配置,您可以使用LANE4~7來對應SERDIN4~7,也可以使用LANE0~3來對應SERDIN4~7,這由您來決定,都是可以實現的。最后,再強調一下工程思維:芯片提供了很多功能,您用也可以,不用也可以,您會怎么做?你就選擇最簡單的來做,甚至就是忽視它存在,也就是使用默認值。

【問題11.14】JESD204B課程里包括AD和DA嗎?還是只是其中一個?

答:本課程只包括AD部分,并且是以AD9144為例來說明。注意不同AD和DA芯片,其使用方法都是不同的。本課程只講述一般思路,需要學員舉一反三使用。

【問題11.15】要得到16個點,插2,所以實際傳8個點;學習筆記里面生成的正弦波,由于插2了,實際是32個點,這么理解對么?

答:在DA輸出端如果16個點組成一個正弦波,插值為2的情況下,FPGA只需要傳輸8個點/正弦波。 如果FPGA傳輸16個點/正弦波,插值為2的情況下,DA輸出端實際是32個點/正弦波。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22036瀏覽量

618116 -

精密儀器

+關注

關注

1文章

132瀏覽量

13211

發布評論請先 登錄

【斯丹麥德電子】常見問題解答:干簧繼電器在測試與測量中的應用

BQ2404x、BQ2405x和BQ2409x常見問題解答

精密儀器APS高級排產軟件解決方案

OMAPL138/C6748 ROM引導加載程序資源和常見問題解答

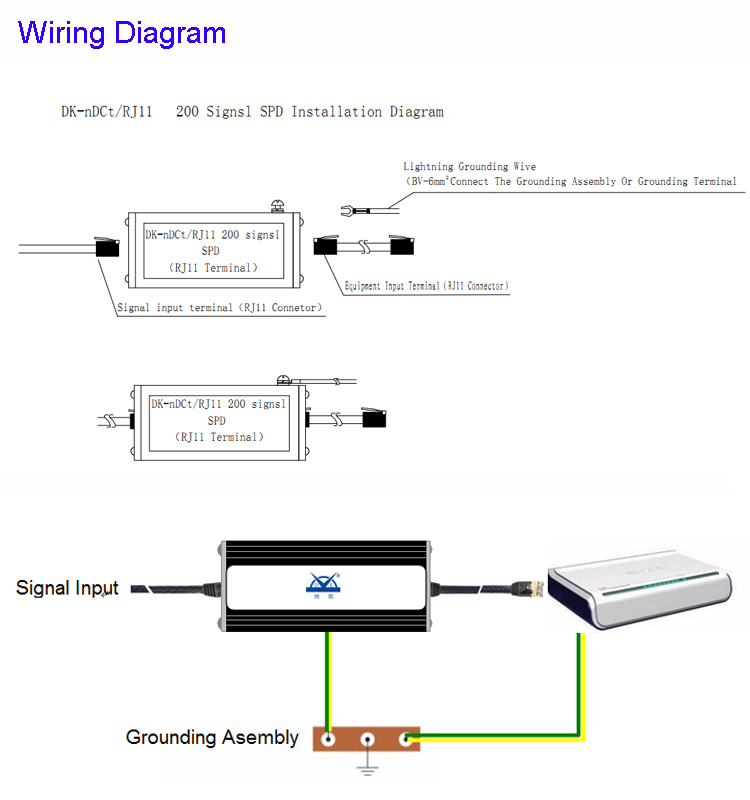

實驗室精密儀器防雷安全方案

關于精密儀器項目的問題解答

關于精密儀器項目的問題解答

評論