使用 AI 模型對(duì)計(jì)算資源的要求可能很高——處理能力越強(qiáng),功率要求也越高。為了解決這個(gè)問(wèn)題,Ceremorphic 開(kāi)發(fā)了 ThreadArch 多線(xiàn)程處理器技術(shù)。

Ceremorphic 開(kāi)發(fā)的一種新穎的架構(gòu)來(lái)支持下一代應(yīng)用程序,例如 AI 模型訓(xùn)練、HPC、藥物發(fā)現(xiàn)、元界處理等。其架構(gòu)基于 5 nm 處理器設(shè)計(jì),并針對(duì)現(xiàn)代硅幾何結(jié)構(gòu)進(jìn)行了調(diào)整,可大規(guī)模滿(mǎn)足可靠性、安全性和功耗方面的高性能計(jì)算需求。

為了服務(wù)于對(duì)性能要求高的市場(chǎng)領(lǐng)域,該芯片架構(gòu)旨在滿(mǎn)足當(dāng)今在可靠性、安全性和能耗方面的高性能計(jì)算問(wèn)題。

芯片的核心是位于數(shù)字電路下方的模擬電路。分層學(xué)習(xí)處理器 (HLP) 的主要功能包括定制的 2GHz 機(jī)器學(xué)習(xí)處理器 (MLP) 和定制的 2GHz FPU。ThreadArch 是獲得專(zhuān)利的多線(xiàn)程處理宏架構(gòu),基于 RISC-V 處理器進(jìn)行代理處理,運(yùn)行頻率為 1GHz。它還包括用于 Metaverse 處理的定制 1GHz 視頻引擎,以及用于低功耗和高效性能的 M55 v1 ARM 內(nèi)核,并具有定制設(shè)計(jì)的 X16 PCle6.0/CXL 3.0 連接接口。Ceremorphic 聲稱(chēng)該技術(shù)的軟錯(cuò)誤率為 100,000-1。

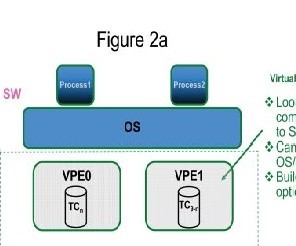

根據(jù) Ceremorphic 的計(jì)劃,芯片將利用主機(jī)系統(tǒng)的 CPU 能力提供計(jì)算能力,然后 Ceremorphic 將加速程序的訓(xùn)練部分。該架構(gòu)將提供對(duì)啟用量子的系統(tǒng)攻擊的防御。

Ceremorphic HLP 多線(xiàn)程芯片具有這樣的規(guī)格和 100 多項(xiàng)專(zhuān)利技術(shù),具有超強(qiáng)計(jì)算能力,同時(shí)功耗相當(dāng)?shù)汀LP 通過(guò)使用適當(dāng)?shù)奶幚硐到y(tǒng)來(lái)確保最佳的能源效率,以獲得最佳的功率性能。該技術(shù)尚未經(jīng)過(guò)測(cè)試,但專(zhuān)利技術(shù)可以保證理論性能的目標(biāo)。

以超低功耗提供超級(jí)計(jì)算能力

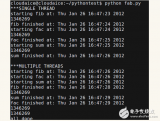

ThreadArch 多線(xiàn)程處理器提供高性能芯片的所有優(yōu)點(diǎn),同時(shí)功耗低。它還通過(guò)優(yōu)化的編譯器和應(yīng)用程序庫(kù)提供 OpenAI 框架軟件支持。雖然目前還沒(méi)有實(shí)際測(cè)試來(lái)驗(yàn)證性能,但 Ceremorphic 確信性能達(dá)到標(biāo)準(zhǔn)。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19896瀏覽量

235227 -

芯片

+關(guān)注

關(guān)注

460文章

52520瀏覽量

440942 -

cpu

+關(guān)注

關(guān)注

68文章

11080瀏覽量

217093

發(fā)布評(píng)論請(qǐng)先 登錄

什么是并行多線(xiàn)程實(shí)時(shí)處理器?MC3172開(kāi)發(fā)環(huán)境開(kāi)發(fā)實(shí)踐

基于MIPS多線(xiàn)程處理器的SOC設(shè)計(jì)

Multi-Threaded多線(xiàn)程編程

低功耗DRP-AI動(dòng)態(tài)可配置處理器有哪些關(guān)鍵特性呢

LabVIEW中使用多線(xiàn)程運(yùn)行速度是否會(huì)更快

基于多核多線(xiàn)程處理器的網(wǎng)絡(luò)設(shè)備設(shè)計(jì)

SHARC 2147x系列處理器具有低功耗與浮點(diǎn)處理精度

利用MIPS多線(xiàn)程處理器優(yōu)化SoC設(shè)計(jì)

linux多線(xiàn)程編程課件

同時(shí)多線(xiàn)程處理器的指令調(diào)度器設(shè)計(jì)

關(guān)于多線(xiàn)程編程教程及經(jīng)典應(yīng)用案例的匯總分析

多核與多線(xiàn)程技術(shù)的區(qū)別

關(guān)于python不能真正多線(xiàn)程問(wèn)題解析

多線(xiàn)程啟動(dòng)停止暫停繼續(xù)

多線(xiàn)程AI處理器具有低功耗超級(jí)計(jì)算

多線(xiàn)程AI處理器具有低功耗超級(jí)計(jì)算

評(píng)論