圖像的邊緣包含了圖像大量的信息,圖像邊緣檢測(cè)作為圖像處理領(lǐng)域中的重要內(nèi)容,在實(shí)際應(yīng)用中也具有重要意義。例如在工業(yè)生產(chǎn)線、車輛檢測(cè)、車牌識(shí)別等實(shí)時(shí)應(yīng)用中,通過邊緣檢測(cè)能夠有效簡(jiǎn)化對(duì)圖像的分析。由于實(shí)時(shí)數(shù)字圖像處理系統(tǒng)具有數(shù)據(jù)量大、處理速度快、重復(fù)度高等特點(diǎn),傳統(tǒng)的軟件方法顯然無法滿足。而由于FPGA具有豐富的邏輯資源和存儲(chǔ)資源,能夠?qū)崿F(xiàn)并行和流水線處理,因此,使用FPGA來實(shí)現(xiàn)需要大量計(jì)算的數(shù)字圖像處理算法,能夠大大提高圖像處理的效率。

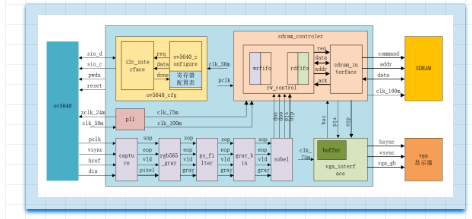

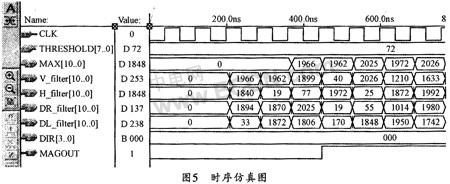

本文介紹了一個(gè)基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)。本篇重點(diǎn)介紹灰度轉(zhuǎn)換、高斯濾波、Sobel邊緣檢測(cè)等經(jīng)典數(shù)字圖像處理算法的原理;分析了OV5640攝像頭的時(shí)序;SDRAM芯片的工作原理及乒乓緩存原理。下篇主要介紹圖像處理算法的實(shí)現(xiàn);OV5640攝像頭驅(qū)動(dòng)模塊的設(shè)計(jì);SDRAM控制器的設(shè)計(jì);相關(guān)模塊的仿真和板級(jí)驗(yàn)證。

一。 數(shù)字圖像處理算法原理

01

灰度轉(zhuǎn)換

RGB顏色模型是由紅(Red)、綠(Green)、藍(lán)(Blue)三種基色以不同的比例疊加而成;而且每個(gè)像素分量(R、G、B)的值分布在0—255范圍內(nèi),三種基色以不同的比例混合,能夠顯示出2563種顏色。

以RGB888格式的真彩色圖像為例,表示1個(gè)像素點(diǎn)需要24bit二進(jìn)制數(shù)據(jù),在后續(xù)做Sobel運(yùn)算時(shí),計(jì)算量較大,所以為了簡(jiǎn)化后續(xù)計(jì)算,將攝像頭采集的RGB565格式的彩色圖像轉(zhuǎn)化為1bit表示的二值圖像,而后通過Sobel算子檢測(cè)圖像像素的梯度提取出圖像的邊緣點(diǎn)。對(duì)于彩色圖像的二值化一般分為兩個(gè)步驟:先將彩色圖像進(jìn)行灰度化得到灰度圖像,然后對(duì)灰度圖像進(jìn)行二值化得到二值圖像。

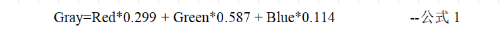

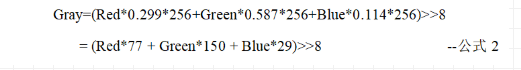

對(duì)于彩色圖像轉(zhuǎn)化為灰度圖像,有一個(gè)著名的色彩心理學(xué)公式,即:

實(shí)際上,上述公式是一個(gè)加權(quán)求和的過程。但是在實(shí)際應(yīng)用時(shí),由于FPGA希望避免復(fù)雜的浮點(diǎn)運(yùn)算,所以這里我們采用整數(shù)運(yùn)算。將R、G、B三個(gè)分量對(duì)應(yīng)的系數(shù)放大256倍得到整數(shù)結(jié)果:

在灰度轉(zhuǎn)換過程中,可能會(huì)因?yàn)槿≌僮饕朐肼暎越酉聛硎褂酶咚篂V波算法來去除灰度轉(zhuǎn)化過程中引入的噪聲。

02

高斯濾波

在對(duì)圖像進(jìn)行誤差評(píng)估時(shí),往往認(rèn)為傳感器引入的噪聲、灰度化處理引入的噪聲都是服從正態(tài)分布(高斯白噪聲),這時(shí)使用高斯濾波器就可以很好地消除高斯噪聲。高斯濾波本質(zhì)上是一種線性平滑濾波,即對(duì)整幅圖像進(jìn)行加權(quán)平均的過程,每一個(gè)像素點(diǎn)的值都是由其本身和鄰域內(nèi)的其他像素點(diǎn)加權(quán)平均后得到的。

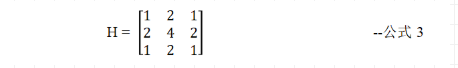

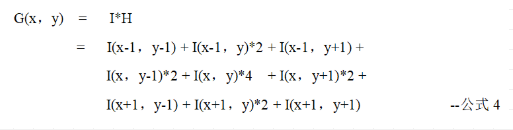

高斯濾波的具體操作是使用一個(gè)N*N卷積模板對(duì)整幅圖像掃描,用模板確定的鄰域內(nèi)的像素加權(quán)平均值代替模板中心像素點(diǎn)的值。本文使用的3*3卷積模板如下:

高斯濾波可以表達(dá)為:

其中,I(x,y)表示原圖像中坐標(biāo)為(x,y)的像素值;G(x,y)表示高斯濾波之后的值。這里為了計(jì)算方便,選取的模板H的權(quán)重系數(shù)都是2的系數(shù)。模板中心的權(quán)值最大,這樣有利于克服邊界效應(yīng),避免經(jīng)過高斯濾波之后圖像模糊。

03

二值化處理

在圖像處理中,二值化的作用是把灰度圖像的像素值設(shè)置為0或者255,即純黑或者純白。通過二值圖像,能更好地分析物體的形狀和輪廓,有利于后續(xù)使用Sobel算子檢測(cè)圖像的邊緣。二值化有多種方法,其中最常用的就是采用閾值法進(jìn)行二值化,根據(jù)閾值選取方式不同,又可以分為全局閾值法與局部閾值法。本文選用全局閾值法,即人為設(shè)定一個(gè)固定的閾值。

04

Sobel邊緣檢測(cè)

Sobel算子主要用于檢測(cè)圖像邊緣,在物體的邊緣通常都有像素的變化,反映了物體與背景之間的差異,或者兩個(gè)物體之間的差異。它是一個(gè)離散差分算子,用來計(jì)算像素點(diǎn)上下、左右領(lǐng)域內(nèi)像素點(diǎn)的加權(quán)差,根據(jù)在邊緣處達(dá)到極值來檢測(cè)邊緣。另外,Sobel算子對(duì)噪聲也有一定的平滑作用,檢測(cè)出精確的邊緣信息,但是邊緣定位精度不高。

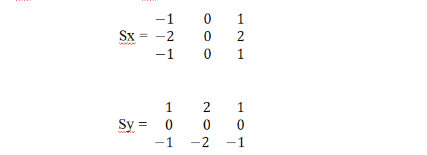

Sobel算子在水平方向和垂直方向各采用一個(gè)模板,檢測(cè)各方向上的邊緣,其優(yōu)點(diǎn)是計(jì)算簡(jiǎn)單,速度快;但是對(duì)于紋理較為復(fù)雜的圖像,檢測(cè)效果不理想。水平方向模板Sx和垂直方向模板Sy如下:

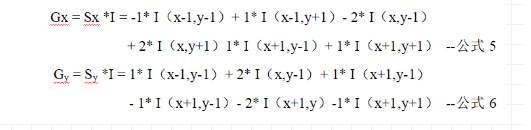

將兩個(gè)算子與圖像做平面卷積,即可得到水平方向與垂直方向的梯度值;若以I表示圖像矩陣,Gx表示水平方向圖像梯度值,Gy表示垂直方向的梯度值,則Gx與Gy可以表示如下:

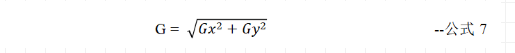

其中,I(x,y)表示模板掩蓋的3*3圖像中心的像素點(diǎn)。最終,圖像中每個(gè)像素點(diǎn)對(duì)應(yīng)的梯度值按照以下公式計(jì)算:

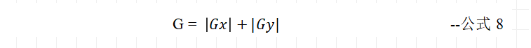

通常為了簡(jiǎn)化計(jì)算,會(huì)使用以下公式近似:

二。 OV5640攝像頭介紹

攝像頭按輸出信號(hào)的類型可以分為數(shù)字?jǐn)z像頭和模擬攝像頭,按照攝像頭圖像傳感器材料構(gòu)成可以分為CCD和CMOS。現(xiàn)在智能手機(jī)的攝像頭絕大部分都是CMOS類型的數(shù)字?jǐn)z像頭。

OV564是一款CMOS類型數(shù)字圖像傳感器,該傳感器支持輸出最大為500萬像素的圖像 (2592x1944分辨率),支持使用VGA時(shí)序輸出圖像數(shù)據(jù),輸出圖像的數(shù)據(jù)格式支持YUV(422/420)、YCbCr422、RGB565以及JPEG格式。它還可以對(duì)采集得的圖像進(jìn)行補(bǔ)償,支持伽瑪曲線、白平衡、飽和度、色度等基礎(chǔ)處理。根據(jù)不同的分辨率配置,傳感器輸出圖像數(shù)據(jù)的幀率從15-60幀可調(diào)。其內(nèi)部有許多寄存器,用來配置攝像頭的工作方式、圖像格式等等;在實(shí)際應(yīng)用時(shí)需要先使用SCCB協(xié)議或者是I2C協(xié)議配置寄存器,使攝像頭按照常見的VGA時(shí)序輸出圖像數(shù)據(jù)。這里不對(duì)SCCB和VGA協(xié)議詳細(xì)介紹。在本次設(shè)計(jì)中,使用I2C協(xié)議配置攝像頭,并將OV5640分辨率配置為720P、數(shù)據(jù)格式為RGB565輸出。

三。 SDRAM介紹

在圖像處理系統(tǒng)中,需要對(duì)圖像視頻數(shù)據(jù)進(jìn)行緩存,所以需要大容量存儲(chǔ)器。SDRAM(Synchronous Dynamic Random Access Memory,即同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)有價(jià)格優(yōu)廉、容量大等優(yōu)點(diǎn),常作為FPGA的外掛存儲(chǔ)器。同步是指其工作需要同步時(shí)鐘,命令的發(fā)送與數(shù)據(jù)的傳輸都以時(shí)鐘為基準(zhǔn);動(dòng)態(tài)是指存儲(chǔ)陣列需要不斷的刷新來保證電容存儲(chǔ)體中的數(shù)據(jù)不丟失;隨機(jī)是指數(shù)據(jù)可以自由指定地址進(jìn)行數(shù)據(jù)讀寫。本次設(shè)計(jì)中,使用的SDRAM芯片型號(hào)為:HY57V2562GTR,容量為256Mbit,數(shù)據(jù)位寬為16bit,最大工作頻率為133MHz。

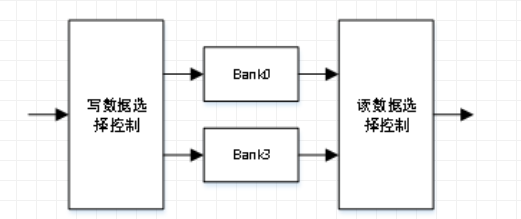

乒乓緩存是一種常用的雙緩存機(jī)制,尤其是在圖像處理中進(jìn)行大量數(shù)據(jù)處理時(shí),為了保證系統(tǒng)的吞吐量,使用兩個(gè)緩存來存儲(chǔ)數(shù)據(jù);一個(gè)緩存用來保存舊的數(shù)據(jù)供圖像處理模塊讀取,與此同時(shí),另一個(gè)緩存保存圖像采集模塊產(chǎn)生的新數(shù)據(jù);同時(shí)以包文的格式對(duì)數(shù)據(jù)進(jìn)行緩存,有利于保證視頻圖像數(shù)據(jù)幀的完整性。

本次設(shè)計(jì)使用SDRAM的兩個(gè)Bank來實(shí)現(xiàn)乒乓緩存,當(dāng)向Bank0緩存數(shù)據(jù)時(shí),從Bank3讀數(shù)據(jù),直到向Bank0寫完一幀數(shù)據(jù),且從Bank3讀完一幀數(shù)據(jù)時(shí),才切換Bank;當(dāng)向Bank3緩存數(shù)據(jù)時(shí),從Bank0讀數(shù)據(jù),直到向Bank3寫完一幀數(shù)據(jù),且從Bank0讀完一幀數(shù)據(jù)時(shí),才切換Bank。通過兩個(gè)Bank循環(huán)讀寫即可實(shí)現(xiàn)數(shù)據(jù)的無縫緩沖與處理。在實(shí)際設(shè)計(jì)中對(duì)數(shù)據(jù)進(jìn)行了丟幀處理,如果在不允許丟幀的情況下,可以對(duì)每個(gè)Bank緩存多幀數(shù)據(jù)。

乒乓緩存示意圖

至此,本文主要對(duì)圖像處理中的幾種經(jīng)典算法的原理進(jìn)行了簡(jiǎn)要介紹,并介紹了我們使用的圖像采集傳感器OV5640攝像頭、SDRAM存儲(chǔ)器的一些特性。下一篇文章我們將繼續(xù)講述:幾種算法的Verilog實(shí)現(xiàn)方案、攝像頭傳感器的配置與數(shù)據(jù)采集模塊的設(shè)計(jì)方案、SDRAM芯片的控制器設(shè)計(jì)方案。

-

傳感器

+關(guān)注

關(guān)注

2562文章

52450瀏覽量

762983 -

FPGA

+關(guān)注

關(guān)注

1643文章

21944瀏覽量

613369 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7625瀏覽量

166239 -

邊緣檢測(cè)

+關(guān)注

關(guān)注

0文章

94瀏覽量

18366

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的實(shí)時(shí)邊緣檢測(cè)系統(tǒng)設(shè)計(jì),Sobel圖像邊緣檢測(cè),FPGA圖像處理

基于FPGA的嵌入式圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì)

基于FPGA的數(shù)字圖像處理中的邊緣檢測(cè)系統(tǒng)

基于FPGA的邊緣檢測(cè)和Sobel算法

基于FPGA的視頻實(shí)時(shí)邊緣檢測(cè)系統(tǒng)該怎么設(shè)計(jì)?

怎樣去設(shè)計(jì)基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)

怎樣去設(shè)計(jì)一種基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)

基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì)(附代碼)

實(shí)時(shí)圖像邊緣檢測(cè)的設(shè)計(jì)及FPGA實(shí)現(xiàn)

數(shù)字圖像邊緣檢測(cè)的FPGA實(shí)現(xiàn)

基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì)

FPGA設(shè)計(jì)中 Verilog HDL實(shí)現(xiàn)基本的圖像濾波處理仿真

基于FPGA實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)的實(shí)現(xiàn)

基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)

基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)

評(píng)論