我們已經討論了制造商購買正確的模數轉換器 (ADC) 的想法,分辨率是決定的重要組成部分。大多數應用程序不需要 32 位精度;但高清音頻、測試儀器和數字縮放等應用程序可以。想知道 32 位 ADC 的那些位是做什么的嗎?下面簡要概述了制造商需要了解的有關使這些部件在系統(tǒng)中按預期工作的知識。

首先,讓我們看看精密 ADC 的內部結構。閃存和流水線 ADC 架構專注于速度,但在大約 16 位分辨率時會遇到限制。逐次逼近寄存器 (SAR) 以速度換取更好的分辨率。SAR 的工作原理是收斂 DAC,直到 A/D 輸入電平匹配。SAR ADC 通常擴展到 24 位,少數推到 32 位,但它們往往會消耗功率。

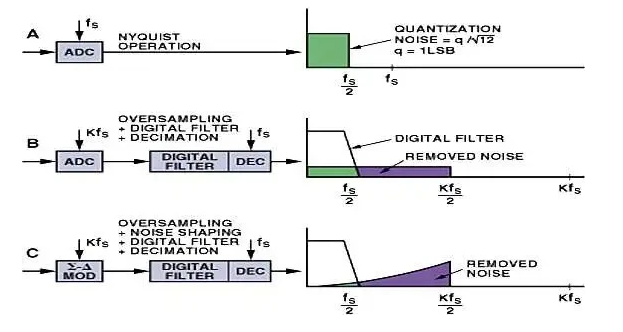

其他一些架構特性帶有 delta-sigma 部分。在轉換之前注意增益階段,以增加動態(tài)范圍并保持低噪聲。此外,樣本之間的信號變化量必須保持較小。最小化增量的首選方法是大規(guī)模過采樣,比奈奎斯特速率高數百甚至數千倍。過濾和抽取使讀數恢復到所需的采樣率,但會增加較大的延遲。通常,減去過采樣延遲的輔助轉換通道會提供較低的分辨率,例如 22 位或 24 位。先進的噪聲整形技術可以進一步降低本底噪聲。

以下是過采樣和噪聲整形在數據轉換中的工作原理。

即使在美好的一天,它也不是真正的 32 位

毫不奇怪,即使數據表說 32 位,這并不是一個得到多少位。平心而論,在大多數從 16 位及更高分辨率開始的轉換器中,動態(tài)范圍和噪聲損失了幾位是一種現象。對于 32 位轉換器,理論動態(tài)范圍約為 194 dB。沒有物理傳感器或模擬前端能提供這么多;實際設備以大約 130 dB 結束。噪音排在首位。正如之前的博客中所討論的,高斯噪聲可以通過過采樣和平均來消除,這通常內置在 32 位 delta-sigma 部分中。

翻閱一些數據表可以看出,最先進的 32 位 delta-sigma ADC 可以以個位數的采樣率提供多達 27 位,并帶有大量的過采樣和濾波。隨著采樣率的增加,有效位會下降一些,這可能是系統(tǒng)設計中的一個重要考慮因素。盡管如此,32 位部件可能比 24 位 ADC 在類似噪聲條件下可以提供的有效分辨率有所改進。

真正的問題是,隨著 ADC 的分辨率提高,最終用戶的感知體驗是否會更好。為了使更多位有用,必須端到端保留分辨率和動態(tài)范圍。例如,以 32 位數字化音頻并以低于該值的速度播放它就無法理解這一點。Rick Rubin 為貧血的 MP3 播放器和耳塞壓縮錄音范圍而發(fā)了財。只有發(fā)燒友才注意到聲音的差異。

然而,32 位隨之而來

我將在 MP3 格式上另辟蹊徑。假設一個人可以負擔得起 32 位 ADC,并且更有效的分辨率適合應用中的體驗。采樣后有 32 位進行數字處理。帶有 Arm 或 RISC-V 內核的快速 32 位微控制器現在很常見,這是一件好事。

對于在 32 位數據上運行的任何算法,例如相關或估計濾波器,整數數學成為一個問題。定點溢出和削波會破壞有效分辨率并增加數字失真。浮點是要走的路,許多 32 位 MCU 都具有硬件浮點能力。不過要小心;具有 23 位尾數的單精度浮點可能仍會裁剪結果。雙精度 64 位浮點解決了這個問題。結合硬件中的 64 位內存提取和 C 或 Python 中的高級數學庫支持,即使是復雜的算法也可以快速運行。

許多 32 位 delta-sigma 轉換器可以運行到音頻采樣率范圍。因為 delta-sigma 部件具有模擬內存和大延遲,所以以更快的采樣率多路復用輸入會變得混亂。32 位 delta-sigma 部件的最佳應用場景可能是非常低的采樣率和激進的過采樣。還有一個論點是不是薄弱環(huán)節(jié)——數字化更多位可能有助于算法將許多樣本混合成更精確的結果。從 32 位 ADC 獲取這些位的增量成本可能值得關注細節(jié)。

在通用動力公司從事導彈制導系統(tǒng)工作十年后,Don Dingee成為摩托羅拉 VMEbus 和單板計算機技術的傳道者。他為 Planet Analog 撰寫有關傳感器、ADC/DAC 和信號處理的文章。

-

adc

+關注

關注

99文章

6628瀏覽量

548162 -

模數轉換器

+關注

關注

26文章

3286瀏覽量

127927

發(fā)布評論請先 登錄

TI AD轉換器增加精度和分辨率時使用的PCB布線技巧

18位分辨率自校正A/D轉換器MCP3421

如何從你的24位轉換器獲得23位有效的分辨率

基于高分辨率A/D轉換器和DL技術實現時鐘穩(wěn)定電路的設計

AD2S1210: 分辨率可變、10位至16位R/D轉換器,內置參考振蕩器

AN-241:AD7710高分辨率(24位)∑-Delta A/D轉換器評估板

32 位 A/D 轉換器分辨率的真相

32 位 A/D 轉換器分辨率的真相

評論