手機、電腦等電子設備與我們的生活密不可分,它們的使用頻率高,更換周期快。消費者在購買產(chǎn)品時,除了考慮基本的品牌、型號和價格之外,還會評估到包括性能在內(nèi)的因素,其中消費者最重視的性能之一就是“速度”。

在影響電子設備速度的因素中,RAM(Random Access Memory,隨機存取存儲器)的性能至關重要。

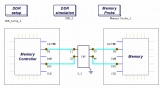

RAM可以隨機讀取信息,是一種讀寫速度較快的存儲器。在各類RAM中,目前使用最多的是DRAM(Dynamic Random Access Memory,動態(tài)隨機存取存儲器),它結(jié)構簡單、容量大、速度快,因此在電腦或移動設備中,可作為幫助中央處理器運算的高速存儲器使用。

高速存儲技術的進化:DDR和LDPPR

在講述內(nèi)存的工作原理之前,我們先來了解一下表示計算機性能的CPU(Center Processing Unit,中央處理器)時鐘頻率的概念。時鐘頻率是由0和1組成的數(shù)字信號的波長。例如,1 GHz(千兆赫)是每秒10億次的時鐘頻率。包括 CPU 在內(nèi)的PC(Personal Computer,個人計算機)組件會根據(jù)此時鐘頻率讀取和寫入數(shù)據(jù)。 在有關內(nèi)存新技術的新聞或PC配置的描述中,我們可以經(jīng)常看到“DDR DRAM”一詞。DDR(Double Data Rate)代表雙倍數(shù)據(jù)速率,是國際標準化組織聯(lián)合電子設備工程委員會 (JEDEC:Joint Electron Device Engineering Council) 在90年代后期開始采用的高速存儲技術。 早期的DRAM根據(jù)計算機的運行節(jié)奏,每個時鐘發(fā)送或接收一次數(shù)據(jù)。但是,隨著CPU的速度飛速增長,需要與之相應的高速存儲器。并且隨著移動設備的增加,低功耗變得更加重要。在一個時鐘信號內(nèi),以低功耗傳輸兩次數(shù)據(jù)的DDR DRAM由此誕生。

在DDR DRAM之后,出現(xiàn)了傳輸速度逐步提高的DDR2、DDR3、DDR4、DDR5等迭代產(chǎn)品。所有DDR DRAM產(chǎn)品都是使用一次信號處理兩次數(shù)據(jù)。通過提高時鐘頻率而不是每時鐘的傳輸量來提高運行速度。DDR的最大數(shù)據(jù)傳輸速度為400Mbps,DDR2為800Mbps,DDR3為1600Mbps,DDR4為3200Mbps,DDR5為 4800Mbps,最大傳輸速率增加兩倍。

此外,還有用于智能手機和平板電腦等移動設備的低功耗內(nèi)存LPDDR(低功耗雙倍數(shù)據(jù)速率)。移動DRAM也分為MDDR、LPDDR2、LPDDR3、LPDDR4、LPDDR4X、LPDDR5和LPDDR5X,和DDR一樣,數(shù)據(jù)處理速度和節(jié)能性隨著代數(shù)的增加而提高。 三星憑借差異化的技術競爭力,正在書寫DRAM新歷史,加速“超級差距”戰(zhàn)略。

基于14納米的下一代移動DRAM——LPDDR5X

今年,三星成功開發(fā)出了14納米LPDDR5X DRAM。LPDDR5X在“速度、容量和省電”特性方面大幅提升,針對5G、AI、元宇宙等爆發(fā)式增長的未來尖端產(chǎn)業(yè)提供優(yōu)秀的解決方案。

LPDDR5X的運行速度在三星現(xiàn)有的移動DRAM中最快,最高可達8.5Gbps,相比上一代產(chǎn)品LPDDR5的運行速度6.4Gbps約快1.3倍。與LPDDR5相比,LPDDR5X的耗電率可減少約20%。

未來,LPDDR5X將擴大高性能低功耗內(nèi)存的使用范圍,除移動通信市場外,還將在服務器、汽車市場創(chuàng)造更多的市場需求。

原文標題:三星半導體|從DDR到LPDDR!DRAM演化歷程探索

文章出處:【微信公眾號:三星半導體和顯示官方】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

半導體

+關注

關注

335文章

28686瀏覽量

233754 -

存儲器

+關注

關注

38文章

7637瀏覽量

166590 -

cpu

+關注

關注

68文章

11051瀏覽量

216211

原文標題:三星半導體|從DDR到LPDDR!DRAM演化歷程探索

文章出處:【微信號:sdschina_2021,微信公眾號:三星半導體和顯示官方】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

DDR3、DDR4、DDR5的性能對比

DDR內(nèi)存的工作原理 DDR內(nèi)存的常見故障及解決辦法

DDR5內(nèi)存與DDR4內(nèi)存性能差異

DDR內(nèi)存與SDRAM的區(qū)別 DDR4內(nèi)存與DDR3內(nèi)存哪個好

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

什么是高密度DDR芯片

高速緩沖存儲器有什么作用

DDR4的結(jié)構和尋址方式

DDR4的基本概念和特性

DDR SDRAM的工作模式和特點

0706線下活動 I DDR4/DDR5內(nèi)存技術高速信號專題設計技術交流活動

高速存儲技術的進化:DDR和LDPPR

高速存儲技術的進化:DDR和LDPPR

評論