以特斯拉Model 3為代表的眾多電動汽車量產車型成功應用SiC MOSFET芯片,表明SiC MOSFET在性能、可靠性和綜合成本層面已得到產業(yè)界的認可。基于大量的設計優(yōu)化和可靠性驗證工作,瑞能半導體于2021年推出SiC MOSFET產品,不僅一如既往的追求高可靠性,同時也擁有業(yè)內領先的高性能和競爭力。

作者:瑞能半導體科技股份有限公司 崔京京

引言

近年內,碳化硅功率器件已逐漸成為高壓、高頻及高效率應用場合需求的首選。性能、可靠性和成本是決定功率器件商業(yè)化進程的三個重要維度,此三者一般互為矛盾關系。但回顧SiC MOSFET器件的技術發(fā)展歷程可以發(fā)現(xiàn),通過優(yōu)化制造工藝和器件設計,不僅帶來性能和可靠性的提升,也降低了單顆芯片成本,技術發(fā)展成為推動SiC MOSFET商業(yè)化進程的重要源動力。

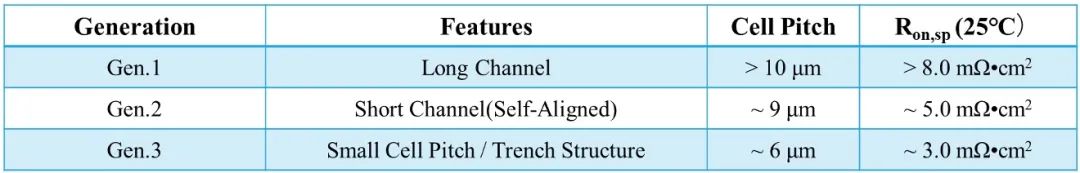

自2011年商業(yè)化產品推出以來,SiC MOSFET目前已完成三次技術迭代,圖1為三代SiC MOSFET的主要技術特點。圖中的比導通電阻值(Ron,sp)是評價單極型功率器件性能的重要指標,其物理意義為器件導通電阻乘以芯片有源區(qū)(有效導通區(qū)域)面積,數值越小表示技術水平越高,即相同導通電阻值產品所需的芯片面積越小。可以看到,基于工藝的進步和設計的優(yōu)化,SiC MOSFET性能逐代提升,單位導通電阻值需要的芯片面積越來越小。

圖1:三代SiC MOSFET產品主要技術特點

新制造工藝開發(fā)

1. 柵氧氮化工藝

相比同為第三代半導體的GaN材料,SiC具有和Si一樣能與O2反應生成理想介質層SiO2的天然優(yōu)勢,但是SiC中C原子的存在使得其MOS結構的柵氧界面(SiO2/SiC)比傳統(tǒng)的Si基柵氧界面(SiO2/Si)高近三個數量級的界面態(tài)密度,導致SiC MOS結構的溝道遷移率遠遠低于Si MOS結構,溝道電阻成為SiC MOSFET的主要電阻。

經過多年研究,通過在氧化工藝后加入氮化工藝(NO或N2O退火工藝),溝道遷移率由10cm2/(V·s)以下增加到20cm2/(V·s)左右,溝道電阻減少50%以上,界面陷阱引起的閾值電壓漂移問題也得到改善。SiC柵氧氮化工藝的成功開發(fā)同時顯著提升了SiC MOSFET的器件性能和產品可靠性,是SiC MOSFET產品走向成熟商業(yè)化的基礎。

2.溝道自對準工藝

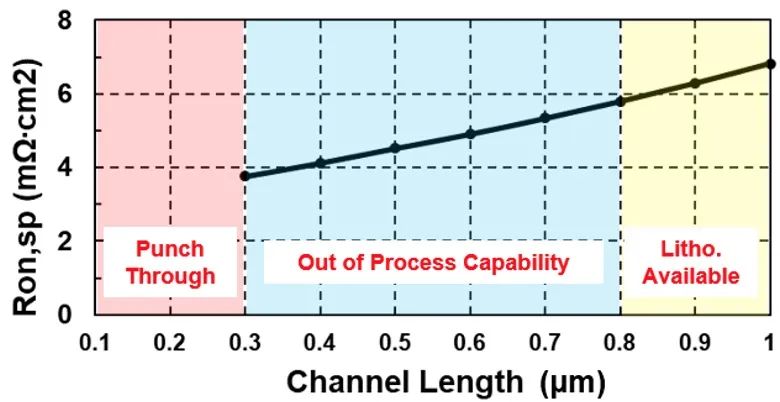

即使經過氮化工藝,進一步減少SiC MOSFET溝道電阻仍然是設計者的工作目標,減少溝道長度是實現(xiàn)此目標的重要手段。但由于無法像傳統(tǒng)Si MOS結構一樣通過雙重擴散工藝形成溝道,SiC MOS結構只能通過***的二次套刻形成溝道,因此溝道長度受制于***的套刻精度以及偏差的控制,根據當前功率半導體產線的實際工藝能力,這意味著溝道長度往往大于0.8微米。圖2展現(xiàn)了不同溝道長度對1200V SiC MOSFET導通性能的影響,0.4微米是理想的溝道長度設計,但是當溝道長度等于0.8微米時,器件導通電阻將增加約50%。

圖2:1200V SiC MOSFET溝道長度 vs. 比導通電阻值

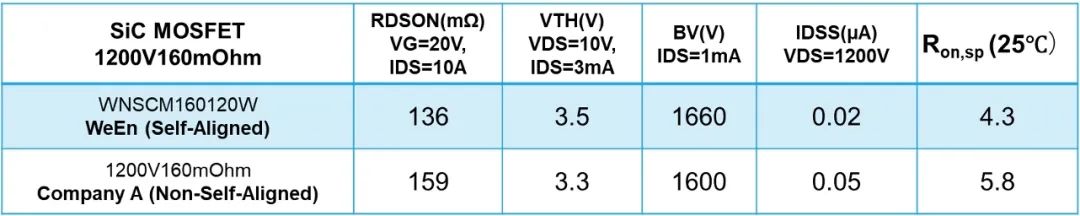

經過大量試驗摸索,幾種針對碳化硅的溝道自對準工藝開發(fā)完成,即使在現(xiàn)有的***能力下也可實現(xiàn)0.8微米以下的溝道長度,SiC MOSFET比導通電阻值因此得到進一步顯著降低。圖3說明了瑞能SiC MOSFET由于采用溝道自對準工藝帶來的性能優(yōu)勢。與柵氧界面氮化工藝一樣,碳化硅溝道自對準工藝的應用并未明顯增加工藝制造成本,但都顯著改善了器件的性能,極大提高了SiC MOSFET產品的競爭力。

圖3:采用溝道自對準工藝(Self-Aligned)與非自對準工藝(Non-Self-Aligned)產品性能對比

芯片設計優(yōu)化

1.元胞尺寸縮小

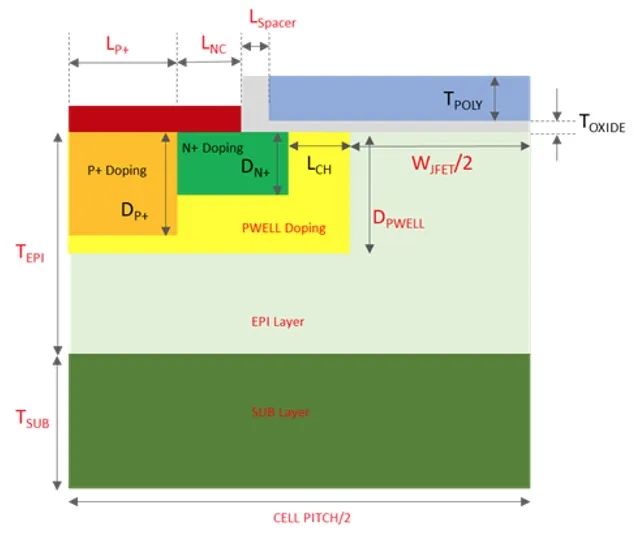

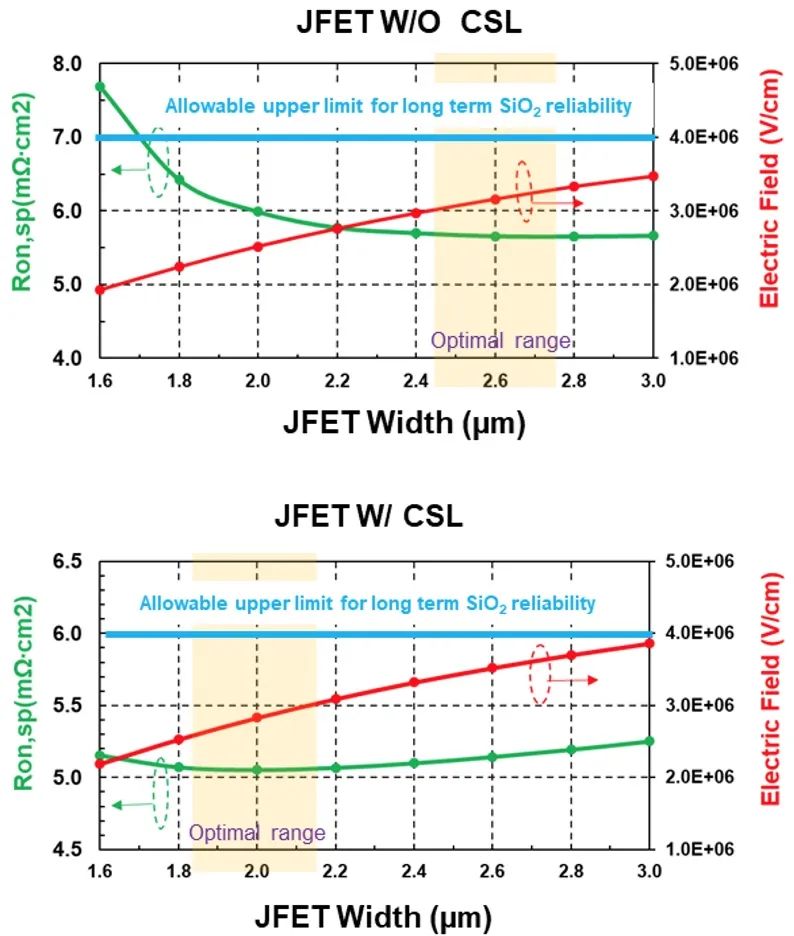

對于平面型SiC MOSFET,減小元胞尺寸(Cell Pitch)是提升器件導通能力的主要方法。圖4為平面柵MOSFET結構的關鍵設計參數,其中JFET區(qū)寬度(WJFET)和源極接觸區(qū)寬度(LP++LNC)是主要的設計優(yōu)化對象。JFET區(qū)寬度越大,該區(qū)域“夾斷”電流的JFET電阻越小,但中間位置柵極氧化層承受的電場強度越大。所以從減小元胞尺寸和提升氧化層可靠性兩個方面來考量,都需要盡量減小JFET區(qū)寬度。然而JFET區(qū)寬度減小會增加JFET電阻,當JFET區(qū)寬度小于臨界值時,JFET電阻以及總導通電阻會顯著增加。

圖4:平面柵MOSFET結構關鍵設計參數(半元胞)

如圖5所示,通過設計額外的JFET區(qū)N型離子注入工藝或高濃度外延工藝形成電流擴展層(CSL),JFET區(qū)寬度可進一步減小20%以上,器件比導通電阻值降低了15%,同時還可減小JFET區(qū)中間位置柵極氧化層承受的電場強度,電流擴展層成為縮小元胞尺寸并提升SiC MOSFET性能的關鍵設計。

圖5:JFET區(qū)寬度與器件性能及可靠性的關系. (a) 無CSL設計, (b) 有CSL設計

源極區(qū)寬度(LP++LNC)的設計主要取決于N+區(qū)和P+區(qū)的歐姆接觸電阻率,即意味著芯片設計需要基于實際的工藝能力。如只有當N型歐姆接觸電阻率低于1E-4mOhm·cm2時,才可以設計低于0.6微米的N+源極區(qū)接觸寬度而不增加器件導通電阻。

2.溝槽柵結構

對于Si IGBT或者Si MOSFET,溝槽柵結構的設計相比于平面柵結構具有明顯的性能優(yōu)勢,但是對于SiC MOSFET來說,目前這種優(yōu)勢不再顯著。根據高斯定理,SiC MOSFET中柵極SiO2表面承受的電場強度約是其對應的SiC表面電場強度的2.5倍,由于碳化硅材料以高臨界擊穿電場強度著稱(約為硅材料的10倍),所以SiC MOSFET中柵極SiO2承受的電場強度極高,比Si MOSFET/IGBT中柵極SiO2承受的電場強度高一個數量級。因此,SiC MOSFET 柵極氧化層的可靠性面臨嚴重的挑戰(zhàn)。溝槽柵SiC MOSFET設計中的柵氧可靠性問題更加嚴重,因為接近90°的溝槽柵拐角進一步加劇了電力線的集中,此處的柵氧層極易被擊穿。

解決柵極氧化層可靠性問題是目前所有的溝槽柵SiC MOSFET結構設計必須首先解決的問題,已有技術路線是設計額外的JFET區(qū),通過其耗盡區(qū)的“夾斷”來屏蔽保護中間的柵極氧化層,減少溝槽柵拐角位置氧化層承受的電應力,但這同時也引入了很大的JFET電阻,導通電阻因此顯著增加。

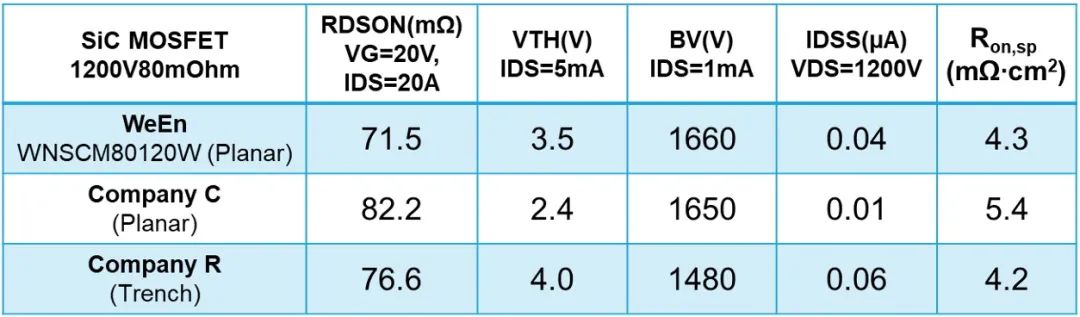

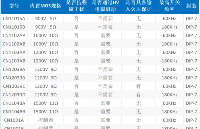

圖6比較了瑞能平面型SiC MOSFET以及兩款市場上主流的平面型和溝槽型SiC MOSFET的主要性能,通過比較可以發(fā)現(xiàn),現(xiàn)階段的溝槽型SiC MOSFET與高性能的平面型SiC MOSFET相比,性能優(yōu)勢并不明顯。反而平面型SiC MOSFET由于具備天然的可靠性優(yōu)勢,更容易被市場認可。當然,如果未來柵極介質層的可靠性問題得到徹底解決,更緊湊的溝槽型SiC MOSFET仍然具有巨大的發(fā)展?jié)摿Α?/p>

圖6:市場主流平面型&溝槽型1200V SiC MOSFET性能對比(25℃)SiC MOSFET

可靠性優(yōu)化

可靠性問題一直是業(yè)內關注的焦點,但隨著柵氧工藝的日益成熟,時間相關的介電擊穿、閾值電壓漂移等問題都得到了顯著改善,SiC MOSFET可靠性也早已達到車規(guī)級應用標準,自2017年Model 3量產以來,SiC MOSFET已在幾十萬輛電動汽車主驅上安全使用了4年時間。

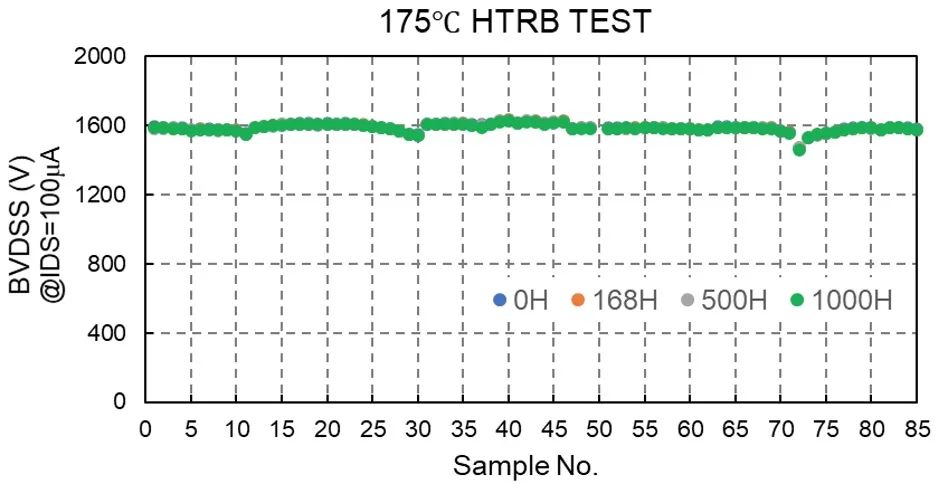

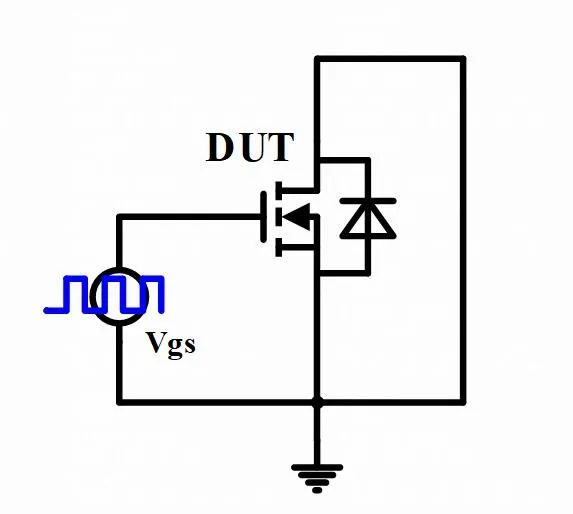

瑞能在產品設計之初就將可靠性放在首位,最新推出的碳化硅MOSFET系列產品,通過采用平面柵結構、高閾值電壓、高阻斷電壓以及高柵氧層耐壓能力的設計,確保了器件在長期的動靜態(tài)工況中具有更強的魯棒性。圖7為瑞能SiC MOSFET WNSCM80120R產品在HTRB(175℃)各個試驗階段的BVDSS數據,其BV數據在1000H試驗中未發(fā)生任何漂移。得益于大量的工藝和設計優(yōu)化工作,使得器件性能上有足夠多的設計裕量,確保產品高可靠性的同時仍然擁有高性能表現(xiàn)。

圖7:瑞能1200V SiC MOSFET產品可靠性表現(xiàn)

驅動優(yōu)化

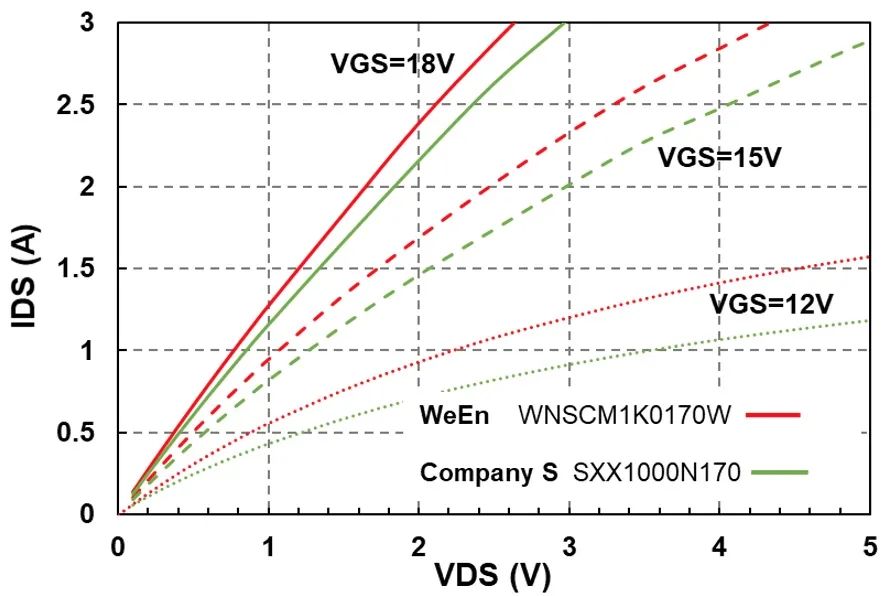

現(xiàn)階段SiC MOSFET的主要替代對象是Si IGBT和Si MOSFET器件,傳統(tǒng)驅動電壓一般為+15V或+12V左右。如前文所述,由于SiC MOSFET的溝道遷移率相對較低,需要通過增加柵極驅動電壓來增強溝道的通流能力,因此目前市場上大部分SiC MOSFET產品一般需要+20V的驅動工作電壓。瑞能1200V SiC MOSFET可以在+18V驅動電壓下高效工作,而即將推出的瑞能1700V1000mOhm SiC MOSFET則可以使用+15V作為驅動工作電壓,實現(xiàn)與傳統(tǒng)驅動電路的完美兼容。

圖8:瑞能1700V1000mOhm SiC MOSFET輸出特性

小結

SiC MOSFET技術的不斷發(fā)展,不僅帶來產品性能和可靠性的提升,也促進了芯片成本的降低,市場規(guī)模因此而快速增加。瑞能半導體始終堅持技術推動產品競爭力,為客戶提供高性能高可靠性的SiC MOSFET產品。

原文標題:高性能高可靠性SiC MOSFET的關鍵設計與優(yōu)化

文章出處:【微信公眾號:瑞能半導體】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52089瀏覽量

435244 -

MOSFET

+關注

關注

149文章

8185瀏覽量

218100 -

SiC

+關注

關注

31文章

3141瀏覽量

64331

原文標題:高性能高可靠性SiC MOSFET的關鍵設計與優(yōu)化

文章出處:【微信號:weensemi,微信公眾號:瑞能半導體】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

SiC-SBD關于可靠性試驗

SiC-MOSFET的可靠性

【PCB】什么是高可靠性?

什么是高可靠性?

為什么華秋要做高可靠性?

SiC MOSFET FIT率和柵極氧化物可靠性的關系

碳化硅SiC MOSFET:低導通電阻和高可靠性的肖特基勢壘二極管

英飛凌推出1200V SiC MOSFET 將提高可靠性和降低系統(tǒng)成本

ROHM SiC-MOSFET的可靠性試驗

SiC-MOSFET的可靠性

高可靠性SiC MOSFET芯片優(yōu)化設計

高可靠性SiC MOSFET芯片優(yōu)化設計

評論