使用Jtag Master調(diào)試FPGA程序時(shí)用到tcl語言,通過編寫tcl腳本,可以實(shí)現(xiàn)對(duì)FPGA的讀寫,為調(diào)試FPGA程序帶來極大的便利,下面對(duì)FPGA調(diào)試過程中常用的tcl語法進(jìn)行介紹,并通過tcl讀FIFO的例子,說明tcl在實(shí)際工程中的應(yīng)用。

TCL語法

目錄

D盤下tcl目錄下文件test.tcl,在TCL中這樣表示:

D:/tcl/test.tcl

cd D:/tcl/test.tcl ;#切換目錄

pwd ;#顯示當(dāng)前路徑

置換

set x 10 ;# 10

set y x+100 ;# x+100

set y $x+100 ;# 10+100

set y [expr $x+100] ;#110

數(shù)據(jù)寫入文件

set f [open new.txt w+] ;# 讀寫方式打開文件,如文件存在則清空文件內(nèi)容,否則創(chuàng)建新的空文件

set a 10

set b 100

puts $f "$a,$b" ;#將a、b寫入文件

close $f ;#關(guān)閉文件

從文件中讀取數(shù)據(jù)

proc read_file { } {

set f [open ./test.txt r] ;#打開文件

while { [gets $f line] >= 0 } { ;#獲取文件每行數(shù)據(jù)

puts $line ;#將數(shù)據(jù)輸出

}

}

獲取文件中的內(nèi)容

proc read_txt {} {

set f [open ./test.txt r]

gets $f line

puts $line

set num [split $line \t] ;#分割數(shù)據(jù)

puts [lindex $num 0] ;#輸出分割后數(shù)據(jù)

puts [lindex $num 1]

}

TCL語句讀FIFO

使用Verilog代碼編寫代碼將數(shù)據(jù)寫入FIFO,當(dāng)寫入一定量數(shù)據(jù)后,使用tcl腳本通過JTAG Master讀取FIFO中的數(shù)據(jù)并存儲(chǔ)到txt文件中,觀察FIFO中數(shù)據(jù)是否正確,tcl腳本中讀FIFO代碼如下。

proc read_fifo { file } {

set num [jtag_read 0x000000dd] ;#讀取FIFO中數(shù)據(jù)個(gè)數(shù)

set f [open $file w+]

for {set i 0} {$i jtag_write 0x000000aa 1 ;#將FIFO讀使能置1

jtag_write 0x000000aa 0 ;#將FIFO讀使能置0,Verilog中使用該信號(hào)上升沿

set result [jtag_read 0x000000bb] ;#讀取FIFO輸出數(shù)據(jù)

set data "$i\t$result" ;#data為編號(hào)與輸出數(shù)據(jù)

puts $f $data ;#保存數(shù)據(jù)到文件中

}

close $f

}

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21944瀏覽量

613453 -

調(diào)試

+關(guān)注

關(guān)注

7文章

603瀏覽量

34487 -

TCL

+關(guān)注

關(guān)注

11文章

1775瀏覽量

89600

發(fā)布評(píng)論請(qǐng)先 登錄

電子電路設(shè)計(jì)中常用的接地方式詳解

FPGA是什么?應(yīng)用領(lǐng)域、差分晶振作用及常用頻率全面解析

FPGA設(shè)計(jì)調(diào)試流程

低壓配電柜中常用的電表有哪些?

單片機(jī)Debug工具性能對(duì)比 單片機(jī)調(diào)試常用命令

工業(yè)自動(dòng)化中常用的傳感器類型

如何在服務(wù)器上調(diào)試本地FPGA板卡

嵌入式常用總線有哪些

labview中常用的程序結(jié)構(gòu)有哪幾種

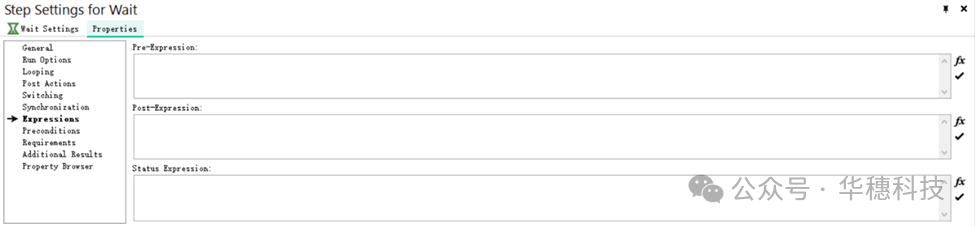

TestStand表達(dá)式中常用的語法規(guī)則和運(yùn)算符使用

FPGA調(diào)試中常用的TCL語法簡介

FPGA調(diào)試中常用的TCL語法簡介

評(píng)論