理解GTX的必備姿勢,學起來!

一、什么是GTX?

GT :Gigabit Transceiver千兆比特收發器;

GTX :Xilinx 7系列FPGA的高速串行收發器,硬核

xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH、GTZ四種串行高速收發器,可以支持多種協議如PCI Express,SATA,JESD204B等。

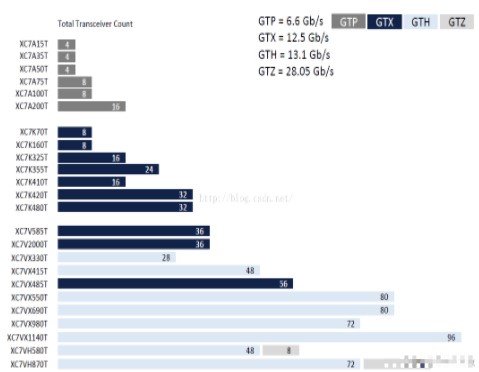

四種收發器主要區別是支持的線速率不同,下圖可以說明在7系列里面器件類型和支持的收發器類型以及最大的收發器數量。

如我們常用的芯片 : 7K325TFFG900-2 ,集成了16個GTX。

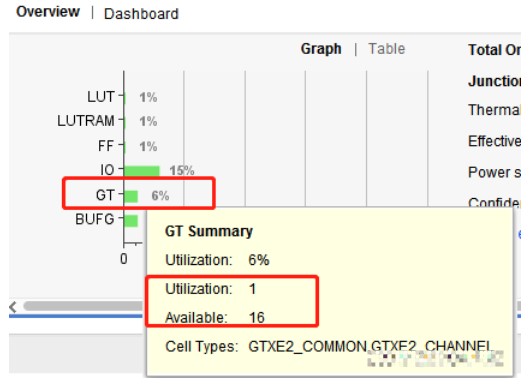

如下圖,我的測試工程使用了1個GTX,可使用16個。

另外,下面還可以看到Cell Types:GTXE2_COMMON與GTXE2_CHANNEL,這個先混個眼熟,后面會繼續談到。

二、Quad/Channel

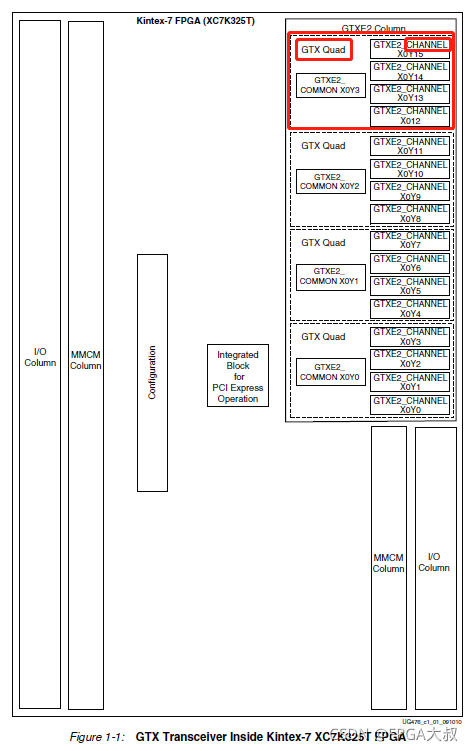

我們先看一張GTX的結構圖:(以7K325T為例)

Quad:4個GTX位1組,稱為Quad,也就是圖中標記的大紅框。

從圖中可以看到,7K325T芯片共有4個Quad,也就是16個GTX。

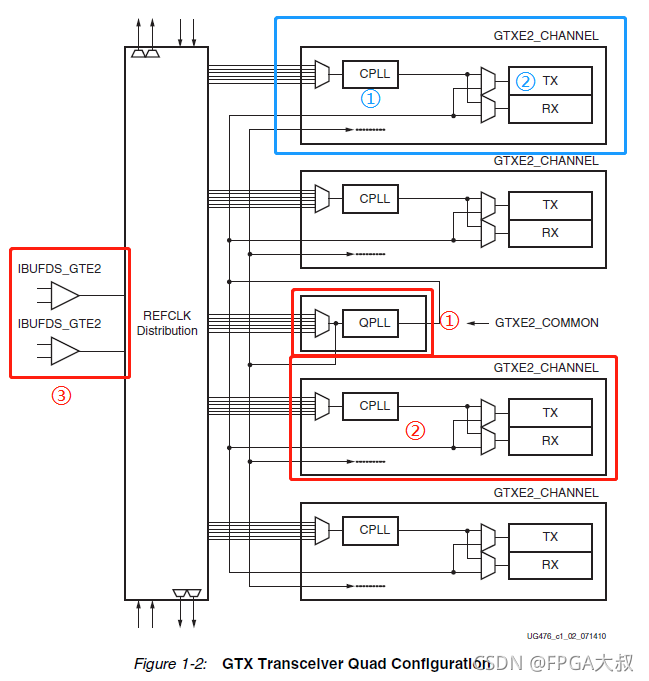

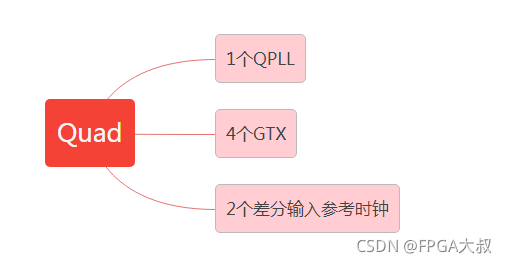

我們繼續來看Quad的布局圖:

簡單總結下:

Quad:

包含4個Channel(每個channel包含一個GTX),1個QPLL,2個差分輸入參考時鐘;

QPLL :

也就是一個Quad共用的PLL,屬于GTXE2_COMMON;

Channel:每個channel就是一個GTX,包含一個CPLL和一對收發器;

CPLL : 每個Channel獨有的PLL,屬于GTXE2_CHANNEL;

注:

CPLL最高支持線速6.x G,而QPLL則可超過10G;在通道線速較大(超過6.xGbps)時,IP會自動使用QPLL。

GTXE2_COMMON、GTXE2_CHANNEL :是Xilinx的器件原語(primitive),原語是Xilinx針對其器件特征開發的一系列常用模塊的名字,用戶可以將其看成Xilinx公司為用戶提供的庫函數;原語類似最底層的描述方法,使用好處多多~

三、PMA與PCS

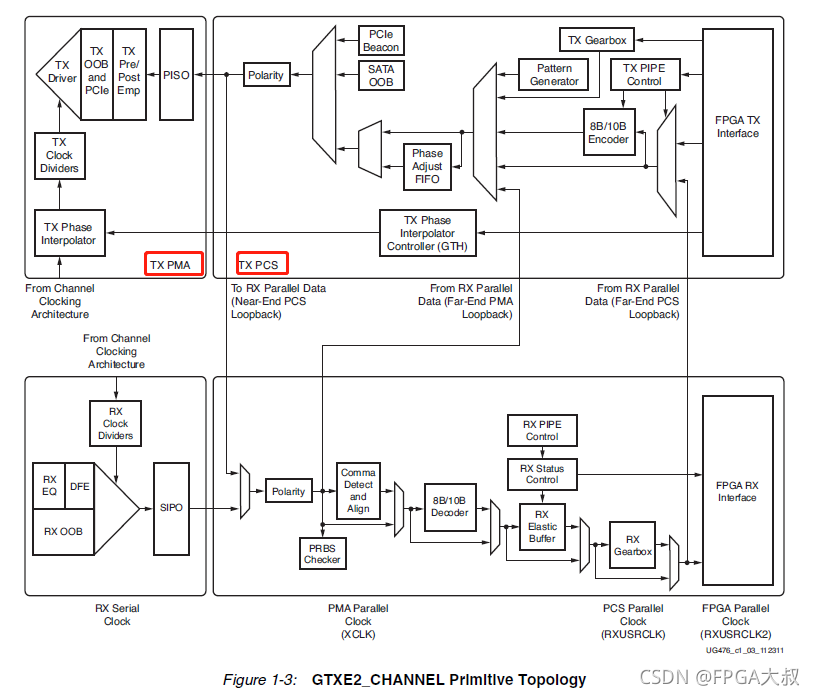

接上一節,我們繼續看Channel的拓撲結構:

看圖說話,發送端(TX)和接收端(RX)功能獨立,均由PMA和PCS兩個子層組成。

PMA:(Physical Media Attachment,物理媒介適配層)

PCS:(Physical Coding Sublayer,物理編碼子層)

其中PMA子層包含高速串并轉換(PISO)、預/后加重、接收均衡、時鐘發生器及時鐘恢復等電路。PCS子層包含8B/10B編解碼、緩沖區、通道綁定和時鐘修正等電路。這么來說,PMA是最基本的單位,負責模擬部分,而PCS主要負責并行的數字電路處理,理論上來說PCS完全可以由邏輯設計完成;但是硬核專用電路實現肯定功能更強大更穩定!

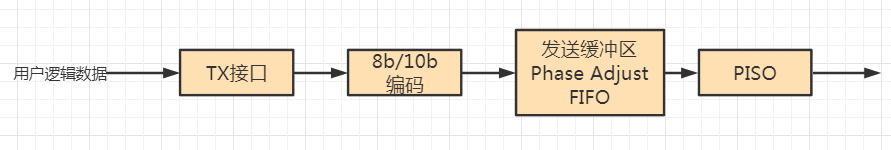

四、GTX收發處理流程

GTX發送端處理流程:首先用戶邏輯數據經過8B/10B編碼后,進入一個發送緩存區Phase Adjust FIFO,該緩沖區主要是PMA子層和PCS子層兩個時鐘域的時鐘隔離,解決兩者時鐘速率匹配和相位差異的問題,最后經過高速Serdes進行并串轉換(PISO parallel-in serial-out),有必要的話,可以進行預加重、后加重(Pre/Post Emp)。值得一提的是,如果在PCB設計時不慎將TXP和TXN差分引腳交叉連接,則可以通過極性控制來彌補這個設計錯誤。

接收端和發送端過程相反,相似點較多,這里就不贅述了,需要注意的是RX接收端的彈性緩沖區(RX Elastic Buffer),其具有時鐘糾正和通道綁定功能。

五、其他內容

介紹一些專用名詞和使用的技術。

1. PRBS :偽隨機序列碼,在一定程度的隨機數,使用PRBS這種偽隨機碼進行高速串行通道的測試,主要是測試誤碼率的情況。

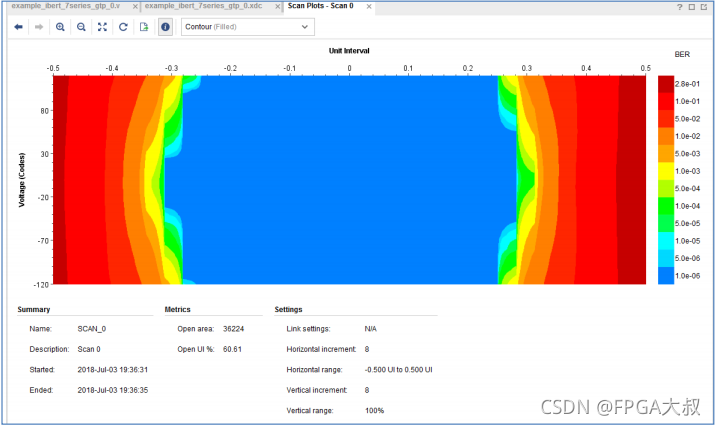

2. ibert:GTX輔助IP核,集成式比特誤碼率測試儀,是Xilinx專門用于具有高速串行接口的 FPGA 芯片的調試和交互式配置工具。放一張測試眼圖吧:(1.25Gbps)

眼圖中顏色越藍的地方,BER 值越小,說明這個區域誤碼率越低,或者幾乎沒有誤碼率。顏色越紅,表示這個區域誤碼率越高。一般來講,這個眼圖的眼睛張的越開,說明數據傳輸信號越好。Link 的速度越低,對應的眼圖也會更好,Link 的速度越高,對應的眼圖會下降。

3. 8b/10b

8b/10b編碼主要是為了解決直流平衡。也就是0/1數量的平衡。

優點:具備錯誤檢測;

缺點:效率不高,具有20%開銷;因此出現了64b/66b編碼。

K28.5 :8b/10b編碼中常用k28.5來做K碼,對應過來就是0xBC,主要用于接收數據對齊。

注:上述介紹均為簡單說明,可能不夠精確,有個概念就好。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21940瀏覽量

613254 -

收發器

+關注

關注

10文章

3588瀏覽量

107243 -

Xilinx

+關注

關注

73文章

2181瀏覽量

124161

發布評論請先 登錄

gtx是光纖嗎

詳解Xilinx的10G PCS PMA IP

【米爾-Xilinx XC7A100T FPGA開發板試用】Key-test

Verilog 測試平臺設計方法 Verilog FPGA開發指南

基于Xilinx ZYNQ7000 FPGA嵌入式開發實戰指南

【米爾-Xilinx XC7A100T FPGA開發板試用】測試一

將ADC32RF42 EVM與xilinx ZC706開發板直接相連,JESD204B時鐘無法建鏈成功,為什么?

采用Xilinx FPGA的AFE79xx SPI啟動指南

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx FPGA平臺GTX簡易使用教程(一)

Xilinx FPGA平臺GTX簡易使用教程(一)

評論