時(shí)鐘就是脈搏,能否工作全靠它!

話(huà)不多說(shuō),直接上干貨!

文中全部使用GTX代指GT Transceiver,同樣適用于GTH。

一、參考時(shí)鐘

1.1 收發(fā)測(cè)試能跑起來(lái)的基本參考時(shí)鐘設(shè)置

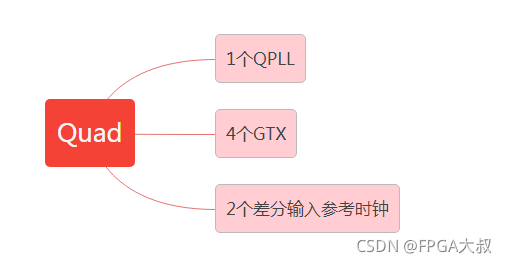

我們先回顧下上一節(jié)的基礎(chǔ)知識(shí):Quad、QPLL、CPLL、Channel、Common;基礎(chǔ)知識(shí)理解了有利于后面內(nèi)容的了解。

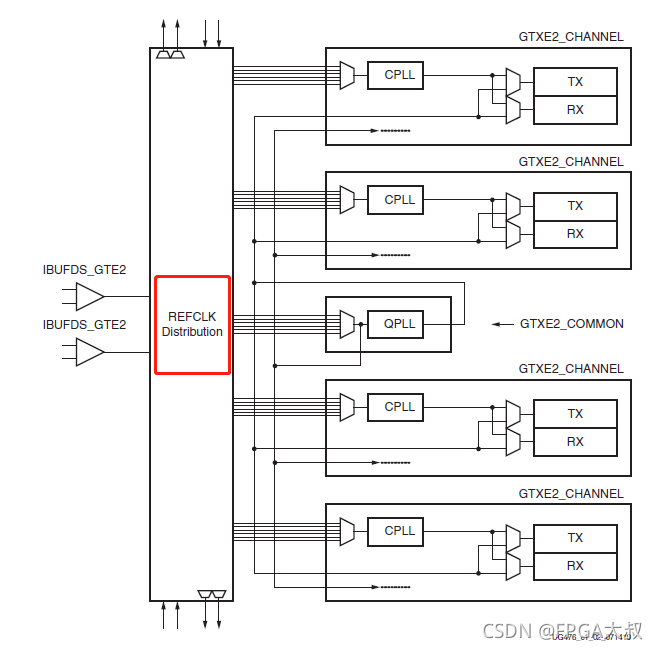

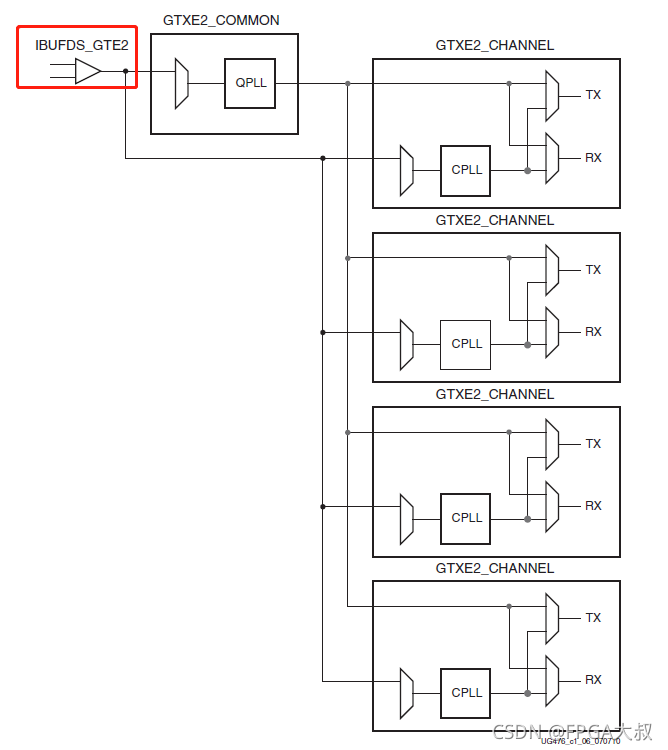

每一個(gè)GTX獨(dú)有的CPLL,4個(gè)GTX共有的一個(gè)QPLL,2個(gè)外部參考時(shí)鐘輸入,和專(zhuān)用參考時(shí)鐘布線(xiàn)(REFCLK Distribution)。

在Quad中,GTXE2_CHANNEL原語(yǔ)以及GTXE2_COMMON原語(yǔ)都必須例化,需要注意的是不管使用還是不使用QPLL,GT_COMMON都是要例化的,這是工具自動(dòng)操作的。

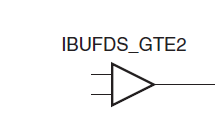

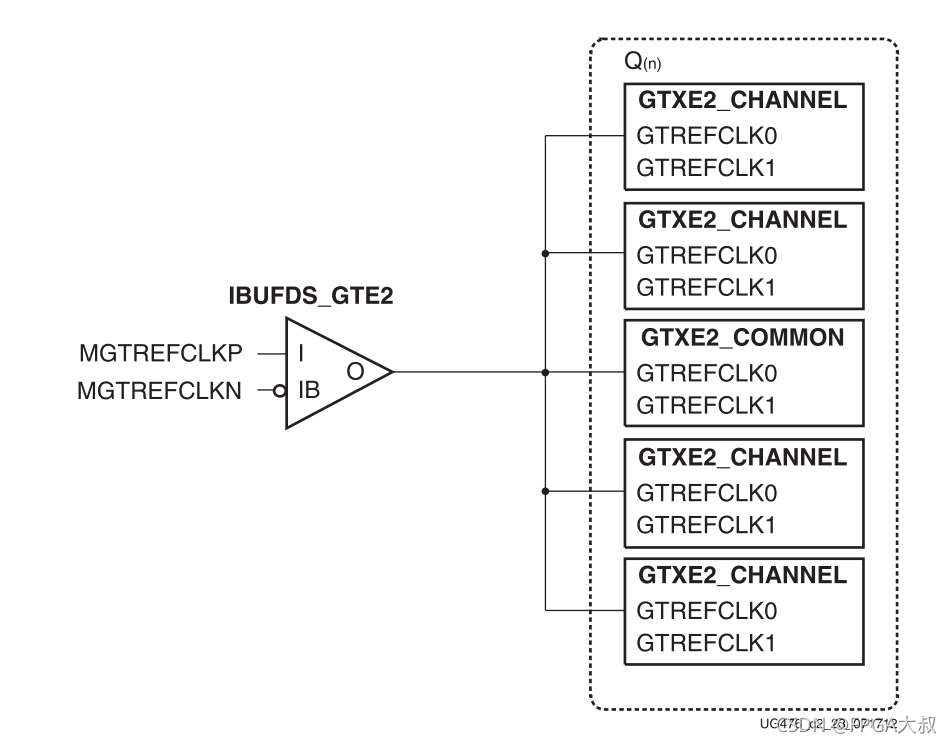

外部參考差分時(shí)鐘輸入經(jīng)過(guò) IBUFDS_GTE2原語(yǔ)轉(zhuǎn)為單端時(shí)鐘后,就是GTX的參考時(shí)鐘輸入端口:

IBUFDS IBUFDS_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

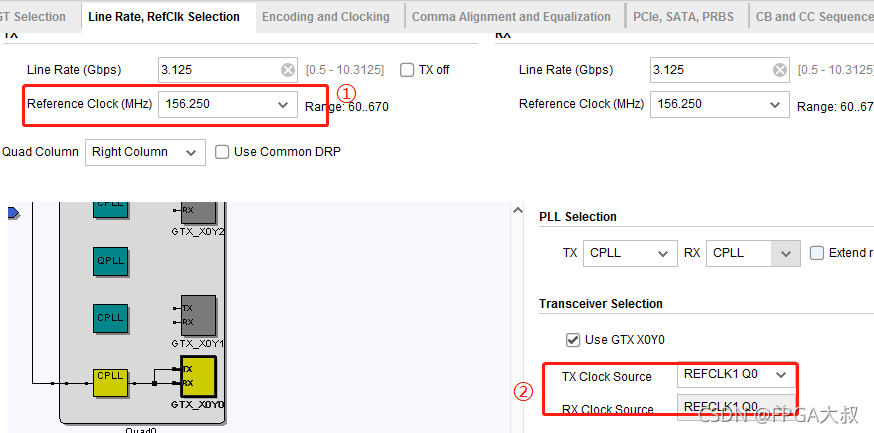

前文已說(shuō)過(guò),1個(gè)Quad有2個(gè)參考時(shí)鐘,我們稱(chēng)之為REFCLK0,REFCLK1,具體用哪一個(gè),看你外部板卡設(shè)計(jì)時(shí),實(shí)際給了哪一路。然后在IP配置時(shí)候,選擇使用對(duì)應(yīng)的參考時(shí)鐘:

總結(jié)如下:

①參考時(shí)鐘根據(jù)板子實(shí)際時(shí)鐘來(lái)選擇頻率;

②參考時(shí)鐘給到REFCLK0 還是REFCLK1也由板子設(shè)計(jì)決定。

但是對(duì)于我們學(xué)習(xí)做仿真而言,暫時(shí)不用管它;如果按照上圖配置來(lái)例化IP;那么對(duì)應(yīng)到程序中就是:

(根據(jù)IP配置)差分輸入?yún)⒖紩r(shí)鐘頻率為156.25Mhz,然后經(jīng)過(guò)IBUFDS原語(yǔ)后轉(zhuǎn)為單端時(shí)鐘并給到參考時(shí)鐘REFCLK1;而REFCLK0由于沒(méi)有使用,直接給0 。

1.2 繼續(xù)了解時(shí)鐘,走著

如果只是測(cè)試收發(fā),跑跑仿真,那么到這里,我們就可以不用繼續(xù)研究了。直接跳到第二章--系統(tǒng)時(shí)鐘。但是GTX的時(shí)鐘遠(yuǎn)不止如此;要知道K7325T有16個(gè)GTX ,V7系列更多;當(dāng)GTX數(shù)量多了的時(shí)候,時(shí)鐘又如何設(shè)定?

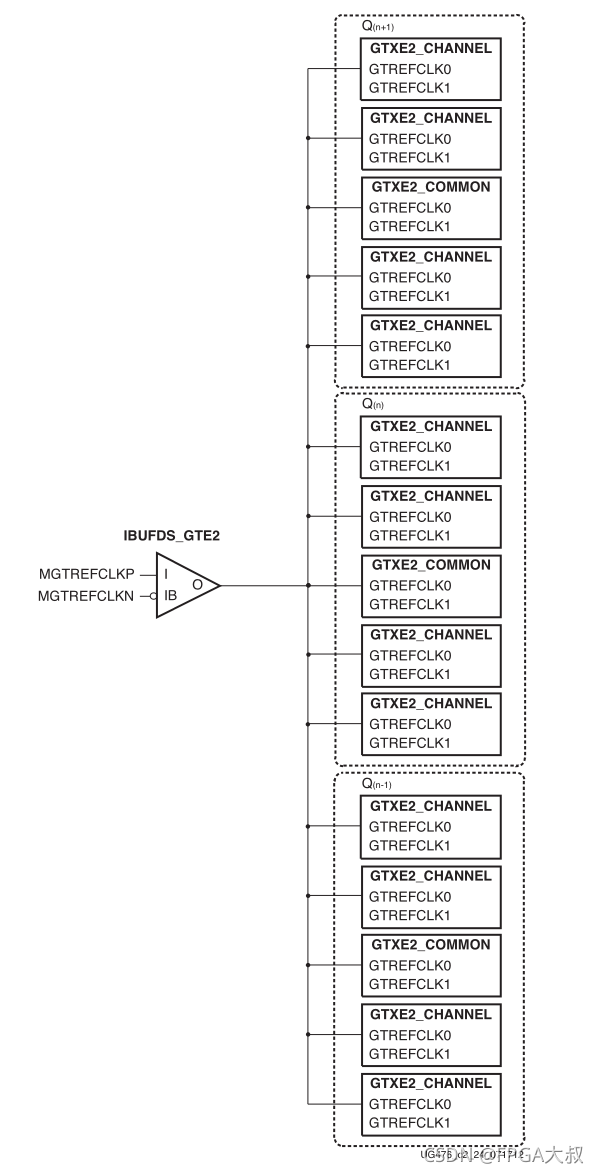

繼續(xù)上圖:

注意到紅框的REFCLK Distribution了嗎?專(zhuān)用參考時(shí)鐘布線(xiàn)。

REFCLK Distribution的上下參考時(shí)鐘引腳分別為南北時(shí)鐘輸入引腳。用于Quad之間共享參考時(shí)鐘;也就是說(shuō),并不一定每一個(gè)Quad都需要外部參考時(shí)鐘,有的Quad可以和其他Quad共享參考時(shí)鐘,而共享的來(lái)源就是南北時(shí)鐘輸入引腳。Quad的南北參考時(shí)鐘稱(chēng)為GTSOUTHREFCLK以及GTNORTHREFCLK。

我們?cè)倮^續(xù)看來(lái)自QPLL參考時(shí)鐘的4通道結(jié)構(gòu)圖:

又總結(jié)一下:

每個(gè)Quad中的GTX通道有6個(gè)可用的參考時(shí)鐘輸入:

兩個(gè)外部輸入?yún)⒖疾罘謺r(shí)鐘,經(jīng)過(guò)IBUFDS后就是GTREFCLK0和GTREFCLK1;

來(lái)自于Quad上面的兩個(gè)參考時(shí)鐘引腳對(duì),GTSOUTHREFCLK0和GTSOUTHREFCLK1;

來(lái)自于Quad下面的兩個(gè)參考時(shí)鐘引腳對(duì),GTNORTHREFCLK0和GTNORTHREFCLK1;

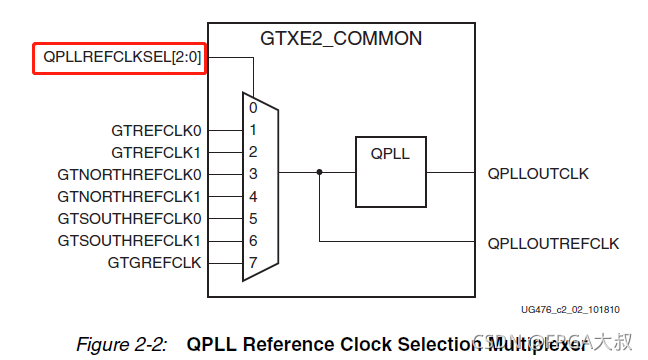

好家伙,一下子來(lái)這么多參考時(shí)鐘,GTX都蒙了,用哪個(gè)呢?

時(shí)鐘多路選擇器安排唄。

下圖是QPLL參考時(shí)鐘多路選擇器:

注意:多了一個(gè)GTGREFCLK,這個(gè)時(shí)鐘是由內(nèi)部邏輯產(chǎn)生的參考時(shí)鐘。貌似只用于內(nèi)部測(cè)試。

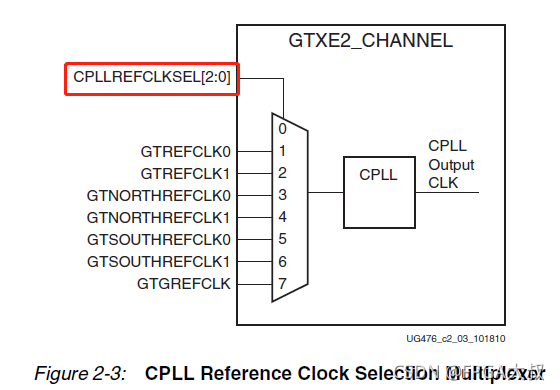

CPLL同理,就不啰嗦了,直接上圖:

1.3 單個(gè)外部參考時(shí)鐘使用情形

(1)單個(gè)外部參考時(shí)鐘驅(qū)動(dòng)單個(gè)Quad中的多個(gè)GTX

這種情況很簡(jiǎn)單,也很常見(jiàn),一個(gè)Quad共用一個(gè)外部參考時(shí)鐘,直接看圖:

用戶(hù)設(shè)計(jì)直接將外部參考時(shí)鐘經(jīng)過(guò)IBUFDS_GTE2輸出REFCLK連接到GTX 的COMMON 、CHANNEL 原語(yǔ)。

(2)單個(gè)外部參考時(shí)鐘驅(qū)動(dòng)多個(gè)Quad中的多個(gè)GTX

單個(gè)外部參考時(shí)鐘也可以驅(qū)動(dòng)多個(gè)Quad中的多個(gè)GTX,例如:

但是,須得遵守一定的規(guī)則:

源Quad上方的Quad數(shù)量不能超過(guò)1個(gè);

源Quad下方的Quad數(shù)量不能超過(guò)1個(gè);

源Quad,指的是直接連接到外部參考時(shí)鐘的Quad。

即是說(shuō): 1個(gè)外部參考時(shí)鐘所驅(qū)動(dòng)的Quad總數(shù)不超過(guò)3個(gè),或驅(qū)動(dòng)的Transceiver不超過(guò)12個(gè)。

1.4 多個(gè)外部參考時(shí)鐘使用情形

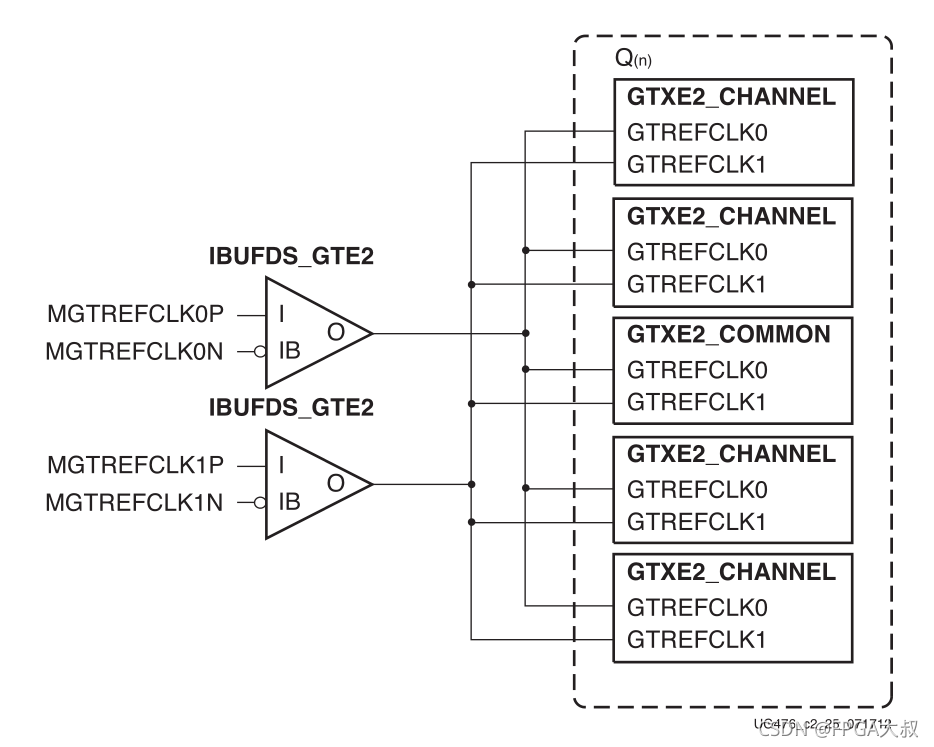

(1)同一個(gè)QUAD中,多個(gè)GTX Transceiver使用多個(gè)參考時(shí)鐘

每個(gè)Quad有兩個(gè)專(zhuān)用的差分時(shí)鐘輸入引腳(MGTREFCLK0[P/N]或 MGTREFCLK1[P/N]) ,可以連接到外部時(shí)鐘源。 每個(gè)專(zhuān)用的參考時(shí)鐘引腳對(duì)輸入進(jìn)來(lái)后必須例化IBUFDS_GTE2,再給到GTX使用。

說(shuō)再多也不如一張圖看的直接:

看圖說(shuō)話(huà):MGTREFCLK0[P/N]連接到GTREFCLK0,將MGTREFCLK1[P/N]連接到GTREFCLK1管腳。

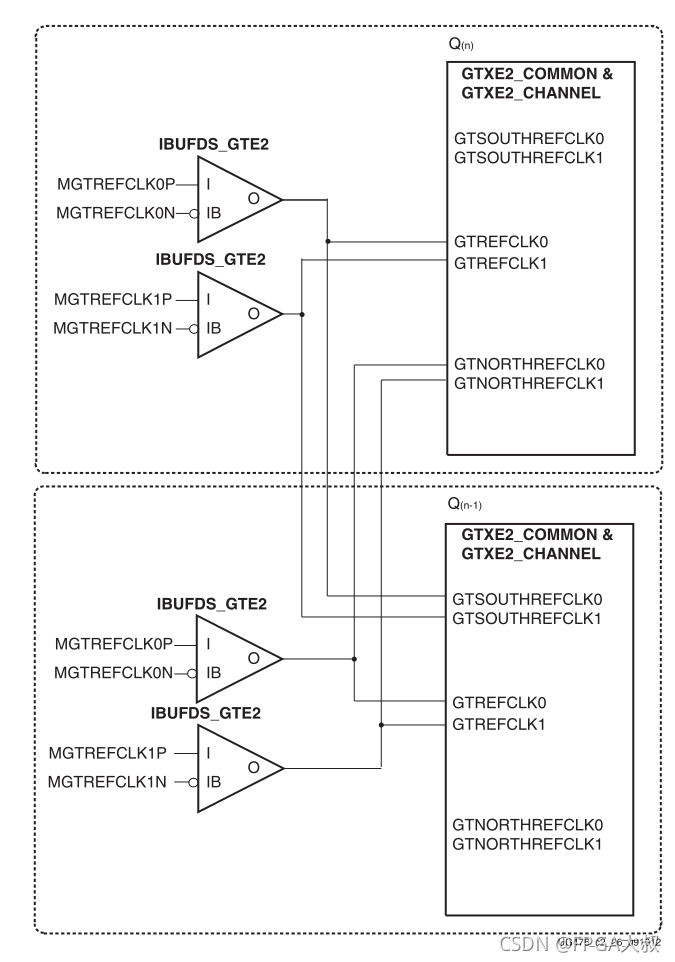

(2)不同QUAD中,多個(gè)GTX Transceiver 使用多個(gè)參考時(shí)鐘

參考時(shí)鐘選擇結(jié)構(gòu)的靈活性允許Quad中的每個(gè)Transceiver都可以訪問(wèn)上下Quad中的專(zhuān)用參考時(shí)鐘。

不啰嗦,上圖上圖:

在每個(gè)GTX有多個(gè)參考時(shí)鐘選項(xiàng)的情況下,設(shè)計(jì)的時(shí)候根據(jù)需求設(shè)置 QPLLREFCLKSEL[2:0]和CPLLREFCLKSEL[2:0]。該遵守的規(guī)則還是要遵守的:1個(gè)外部參考時(shí)鐘所驅(qū)動(dòng)的Quad總數(shù)不超過(guò)3個(gè),或驅(qū)動(dòng)的Transceiver不超過(guò)12個(gè)。

1.5 QPLL/CPLL工作原理

算了, 略過(guò)吧,有興趣具體查閱手冊(cè)《UG476》。

二、系統(tǒng)時(shí)鐘

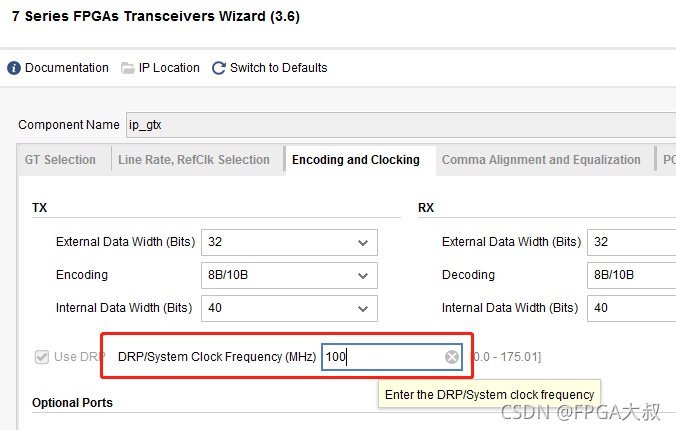

對(duì)應(yīng)IP設(shè)置的第三頁(yè),我們所設(shè)置的時(shí)鐘頻率,也是DRP CLOCK;跟板子提供的時(shí)鐘對(duì)應(yīng);

對(duì)應(yīng)到代碼:

input wire DRP_CLK_IN_P,

input wire DRP_CLK_IN_N,

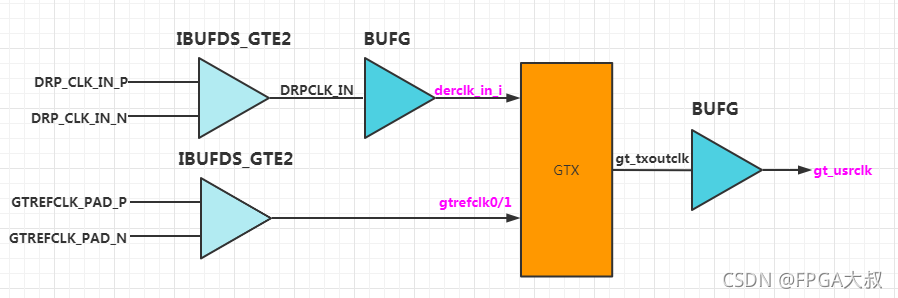

我們參照Example Design中對(duì)該時(shí)鐘的處理:

先經(jīng)過(guò)IBUFDS轉(zhuǎn)為單端時(shí)鐘,然后經(jīng)過(guò)BUFG,再給到GTX核。

IBUFDS IBUFDS_DRP_CLK (

.I (DRP_CLK_IN_P),

.IB (DRP_CLK_IN_N),

.O (DRPCLK_IN)

);

BUFG DRP_CLK_BUFG(

.I (DRPCLK_IN),

.O (drpclk_in_i)

);

這里,有個(gè)有意思的事情:

筆者使用50Mhz / 100Mhz 輸入,最終GTX輸出都是OK的,什么原因呢?

三、邏輯使用的時(shí)鐘

TXUSRCLK 和 TXUSRCLK2 生成:

(以下內(nèi)容為UG476翻譯)

FPGA發(fā)送端包含兩個(gè)并行時(shí)鐘:TXUSRCLK 和 TXUSRCLK2,

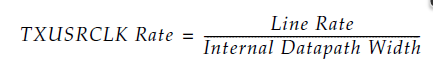

TXUSRCLK是GTX中PCS邏輯的內(nèi)部時(shí)鐘。它的頻率由TX端的Line Rate和內(nèi)部數(shù)據(jù)總線(xiàn)寬度共同決定:

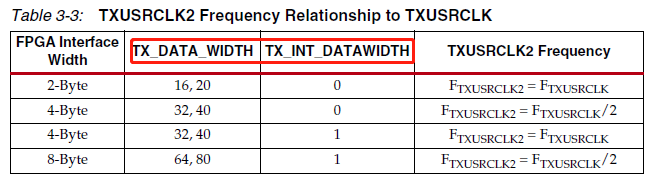

TXUSRCLK2是GTX的TX端信號(hào)的主要同步時(shí)鐘。 GTX發(fā)送的大多數(shù)信號(hào)都是在TXUSRCLK2的上升沿進(jìn)行采樣。TXUSRCLK2和TXUSRCLK之間有一個(gè)固定比率關(guān)系,由TX_DATA_WIDTH 和TX_INT_DATAWIDTH決定,見(jiàn)下圖:

回想一下,我們要通過(guò)某個(gè)IP核進(jìn)行發(fā)送數(shù)據(jù),那么發(fā)送數(shù)據(jù)模塊所使用的時(shí)鐘必然是該IP核出來(lái)的同步時(shí)鐘。

對(duì)于GTX而言,我們發(fā)送數(shù)據(jù)所在的時(shí)鐘域,就是由核輸出的gt0_txoutclk_i。

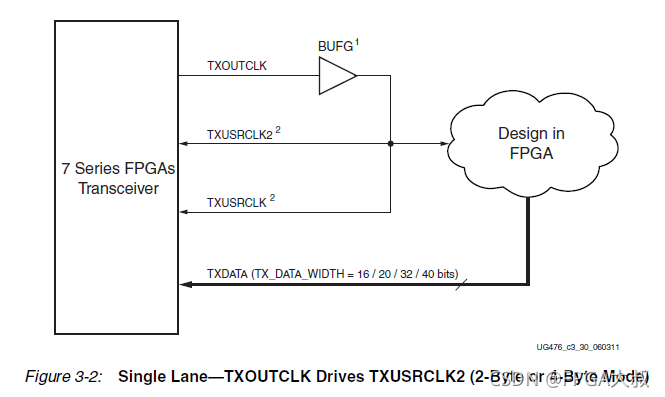

再來(lái)看兩種情況:

(1)單通道——TXOUTCLK 驅(qū)動(dòng)TXUSRCLK2 (2-Byte 或者4-Byte 模式)

(2)多通道——TXOUTCLK 驅(qū)動(dòng)TXUSRCLK2 (2-Byte or 4-Byte 模式)

四、時(shí)鐘篇小結(jié)

前面解釋的很詳細(xì)了,最后放張圖吧。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22036瀏覽量

618120 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

125260

發(fā)布評(píng)論請(qǐng)先 登錄

XILINX XCZU67DR FPGA完整原理圖

gtx是光纖嗎

詳解Xilinx的10G PCS PMA IP

xilinx FPGA IOB約束使用以及注意事項(xiàng)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】Key-test

Verilog 測(cè)試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開(kāi)發(fā)指南

基于Xilinx ZYNQ7000 FPGA嵌入式開(kāi)發(fā)實(shí)戰(zhàn)指南

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】測(cè)試一

將ADC32RF42 EVM與xilinx ZC706開(kāi)發(fā)板直接相連,JESD204B時(shí)鐘無(wú)法建鏈成功,為什么?

采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+04.SFP之Aurora測(cè)試(zmj)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+01.開(kāi)箱(zmj)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

如何申請(qǐng)xilinx IP核的license

Xilinx FPGA平臺(tái)GTX簡(jiǎn)易使用教程(二)

Xilinx FPGA平臺(tái)GTX簡(jiǎn)易使用教程(二)

評(píng)論