電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費資金,占用空間,而且,在遇到交付瓶頸的時候還會難以獲得。所以,如何最大限度減小輸出電容的數量和尺寸,這個問題反復被提及。

輸出電容造成的影響

論及此問題,輸出電容的兩種影響至關重要:對輸出電壓紋波的影響,以及在負載瞬變后對輸出電壓的影響。

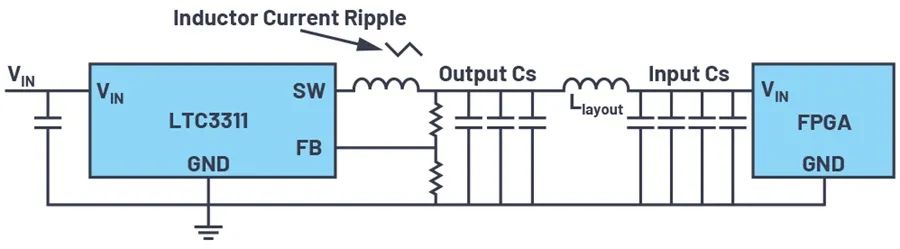

首先,我們來看一看輸出電容這個詞。這些電容一般安裝在電源的輸出端。但是,許多電力負載(電力消耗對象),例如FPGA,都需要使用一定數量的輸入電容。圖1顯示的是一種典型的包含負載和FPGA的電源設計。如果在電路板上,電壓生成電路和耗電電路之間的距離非常短,那么電源輸出電容和負載輸入電容之間的界限就會變得非常模糊。

圖1. LTC3311 開關穩壓器,包含所連接的FPGA對應的輸出電容和輸入電容。

通常需要利用某種物理分隔方法來加以區分,而這會導致產生大量寄生電感(Llayout)。

電源輸出端的電容形成決定了降壓型(降壓)開關穩壓器的電壓紋波。此時,經驗法則適用:輸出紋波電壓等于電感紋波電流 X 輸出電容的電阻。

這個電阻ZCout由電容的大小和數量,以及等效串聯電阻(ESR)和等效串聯電感(ESL)組成。如果電源輸出端只有一個電容,此公式高度適用。如果是更為復雜的情況(參見圖1),其中包含多個并聯電容,且因為布局(Llayout)的原因產生了串聯電感,那么計算不會如此簡單。

在這種情況下,非常適合使用LTspice這樣的模擬工具。圖2所示為針對圖1提到的情況快速創建的電路圖。可以將不同值(包括ESR和ESL)設置給單個電容。也可以考慮板布局(例如Llayout)可能產生的影響。然后,會仿真開關穩壓器輸出端和負載輸入端的電壓紋波。

圖2. 使用LTspice評估系統電源輸出端的不同電容。

輸出電容也會影響負載瞬變后的輸出電壓失調。我們也可以使用LTspice仿真這一影響。此時,特別需要注意的是,在某些限制范圍內,電源控制環路的控制速度和輸出電容的電感是相互關聯的。電源控制環路的速度如果更快,那么在負載瞬變之后,只需要更少數量的輸出電容即可保持在特定的輸出控制窗口之內。

最后但同樣重要的一點是,vvv具有自適應電壓定位(AVP)。AVP可以利用輸入誤差電壓預算并減少輸出電容器的數量,此外,設計人員還可以通過增加環路帶寬來實現減少輸出電容的數量。

AVP在低負載條件下稍微增大輸出電壓,在高負載條件下稍微降低輸出電壓。然后,如果發生負載瞬變,則更多動態輸出電壓偏差都發生在允許的輸出電壓范圍內。

建議使用ADI公司的LTpowerCAD來找出哪些控制環路可以優化,以及可以減少多少個輸出電容。圖3所示為計算控制速度的屏幕截圖。其中顯示了在負載瞬變后計算得出的電壓過沖。可以通過改變輸出電容、調節開關穩壓器控制環路的速度來進行優化。

確定正確的參數后,即可減少電源中輸出電容的數量,如此可以節省資金和板空間,我們建議大家使用這個開發步驟。

責任編輯:haq

-

電源

+關注

關注

185文章

18255瀏覽量

254898 -

電容

+關注

關注

100文章

6227瀏覽量

153150

原文標題:如何最大限度減小電源設計中輸出電容的數量和尺寸?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智能電機控制裝置如何最大限度地提高恢復能力和正常運行時間

AN101-最大限度地減少線性穩壓器輸出中的開關穩壓器殘留

TAS5630如何才能最大限度地減少電壓失調,或者調節為0?

最大限度地減少TRF7964A和TRF7970A省電模式下的電流消耗

最大限度地減少TPS53355和TPS53353系列器件的開關振鈴

最大限度地提高GSPS ADC中的SFDR性能:雜散源和Mitigat方法

皮秒激光器優化碳化硅劃刻

如何最大限度減小輸出電容的數量和尺寸

如何最大限度減小輸出電容的數量和尺寸

評論