西電劉艷團(tuán)隊于IEEE EDL四月刊發(fā)布了基于靜電摻雜的鐵電晶體管器件,相比化學(xué)摻雜工藝,其具有非揮發(fā)、可重構(gòu)、輕摻雜漏極、高源漏摻雜濃度、低源漏電阻等優(yōu)良特性,對于先進(jìn)集成電路工藝微縮和后摩爾新型器件提供了更多的解決路徑。

研究背景

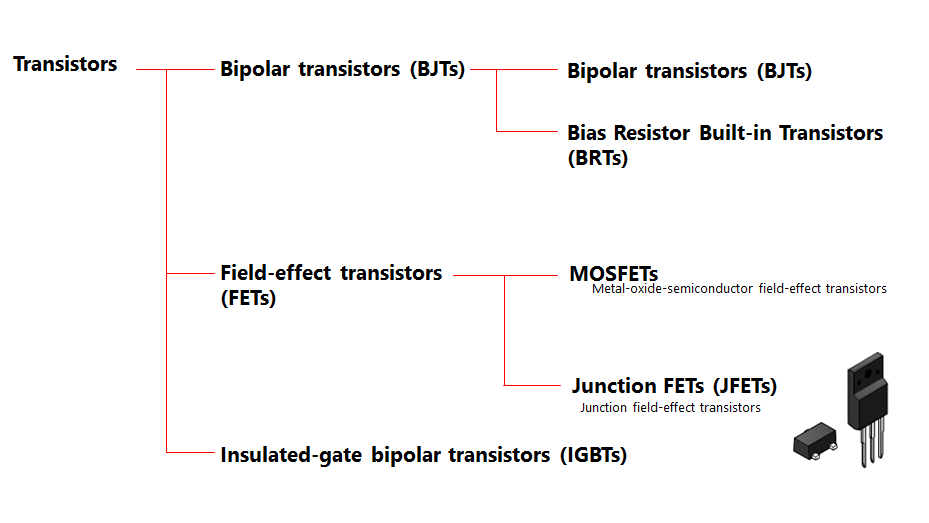

化學(xué)摻雜技術(shù)被大規(guī)模運用于半導(dǎo)體器件的制造,但其技術(shù)有著包括較高的摻雜活化熱預(yù)算、低于固溶極限的摻雜濃度、雜質(zhì)散射和摻雜梯度在內(nèi)各種問題。相應(yīng)地,靜電摻雜技術(shù)被認(rèn)為是最具有替代化學(xué)摻雜技術(shù)的新路線。通過這種技術(shù),摻雜可以被能帶和臨近電極費米能級的相對能量差所控制,通過功函數(shù)調(diào)控或外偏置可實現(xiàn)有效控制。

作為化學(xué)摻雜技術(shù)的替代,靜電摻雜技術(shù)因其非易失性、載流子可控的特性,基于該技術(shù)的可重構(gòu)晶體管被提出,但這需要額外偏置條件來克服易揮發(fā)性。由于非易失性和可控的極化狀態(tài),鐵電材料在非易失性存儲器方面的應(yīng)用越來越廣,這為實現(xiàn)非易失性和可重構(gòu)性提供了技術(shù)路徑。

西電劉艷教授團(tuán)隊與新加坡國立大學(xué)及印度理工學(xué)院聯(lián)合課題組在這一研究方向上取得了重要進(jìn)展,以“Proposal of Ferroelectric Based Electrostatic Doping for Nanoscale Devices”為題發(fā)表于IEEE Electron Device Letters,鄭思穎為第一作者,西電劉艷教授和新加坡國立大學(xué)的Jiuren Zhou為共同通訊作者。

研究內(nèi)容

在本項研究中,團(tuán)隊提出了基于鐵電材料的經(jīng)典摻雜技術(shù),通過插入極性門的鐵電薄膜實現(xiàn)了非揮發(fā)性和可重構(gòu)性,可在不需要恒定偏置條件的情況下制備基于鐵電材料靜電摻雜技術(shù)的可重構(gòu)納米片場效應(yīng)晶體管,具有自然形成的輕摻雜漏極(LDD)*和每立方厘米超過1021的極高的源漏區(qū)摻雜濃度,可改善晶體管亞閾值擺幅*、抑制漏極感應(yīng)勢壘降低(DIBL)*、獲得超低源漏區(qū)電阻。

*輕摻雜漏極:全稱Lightly doped drain,在雙擴(kuò)散漏(double diffuse drain)工藝上發(fā)展而來,在MOS側(cè)墻形成之前增加一道輕摻雜的離子注入流程,側(cè)墻形成后依然進(jìn)行源漏重?fù)诫s離子注入,漏極和溝道之間會形成一定寬度的輕摻雜區(qū)域;相比DDD工藝降低了器件漏極附近峰值電場,削弱了熱載流子注入效應(yīng)。

*亞閾值擺幅:Subthreshold swing,是衡量晶體管開啟與關(guān)斷狀態(tài)之間相互轉(zhuǎn)換速率的性能指標(biāo),它代表源漏電流變化十倍所需要柵電壓的變化量,又稱為S因子,S越小意味著開啟關(guān)斷速率ON/OFF越快。

漏極感應(yīng)勢壘降低:Drain induction barrier lower,也稱漏極誘導(dǎo)勢壘降低,短溝道效應(yīng)之一,當(dāng)溝道長度減小、VDS增加、使得漏結(jié)與源結(jié)的耗盡層靠近時,溝道中的電力線可以從漏區(qū)穿越到源區(qū),并導(dǎo)致源極端勢壘高度降低,從而源區(qū)注入到溝道的電子數(shù)量增加,結(jié)果漏極電流增加。

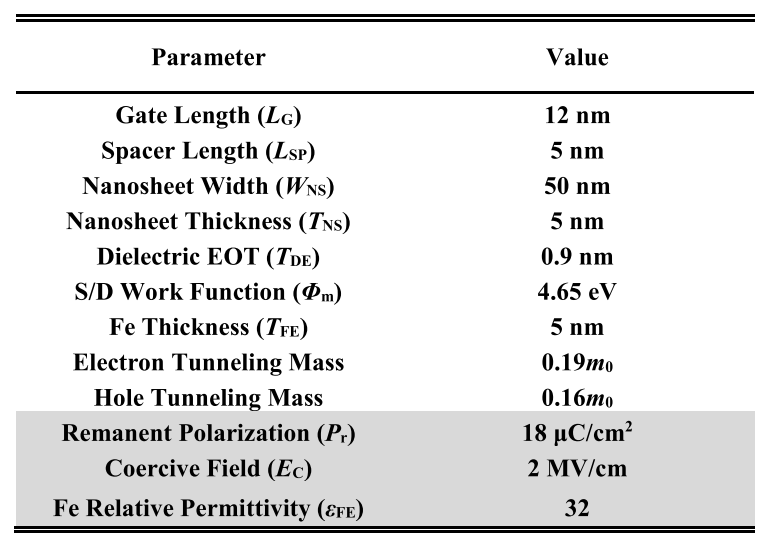

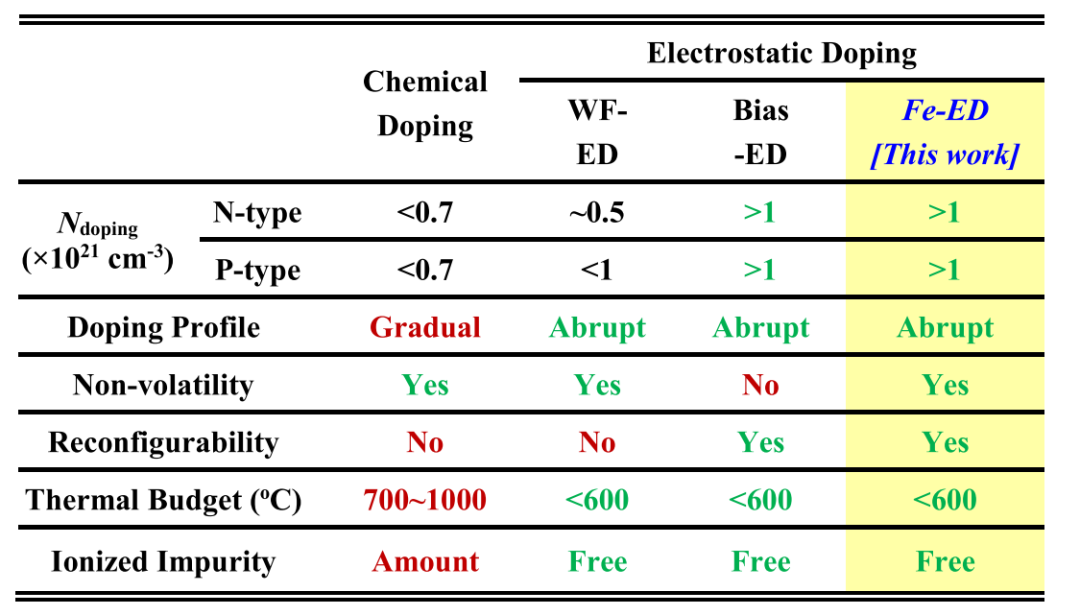

晶體管參數(shù)表

圖(a)鐵電納米片晶體管示意圖

圖(b)鐵電薄膜的自極化和可控極化

圖(c)可重構(gòu)晶體管能帶圖

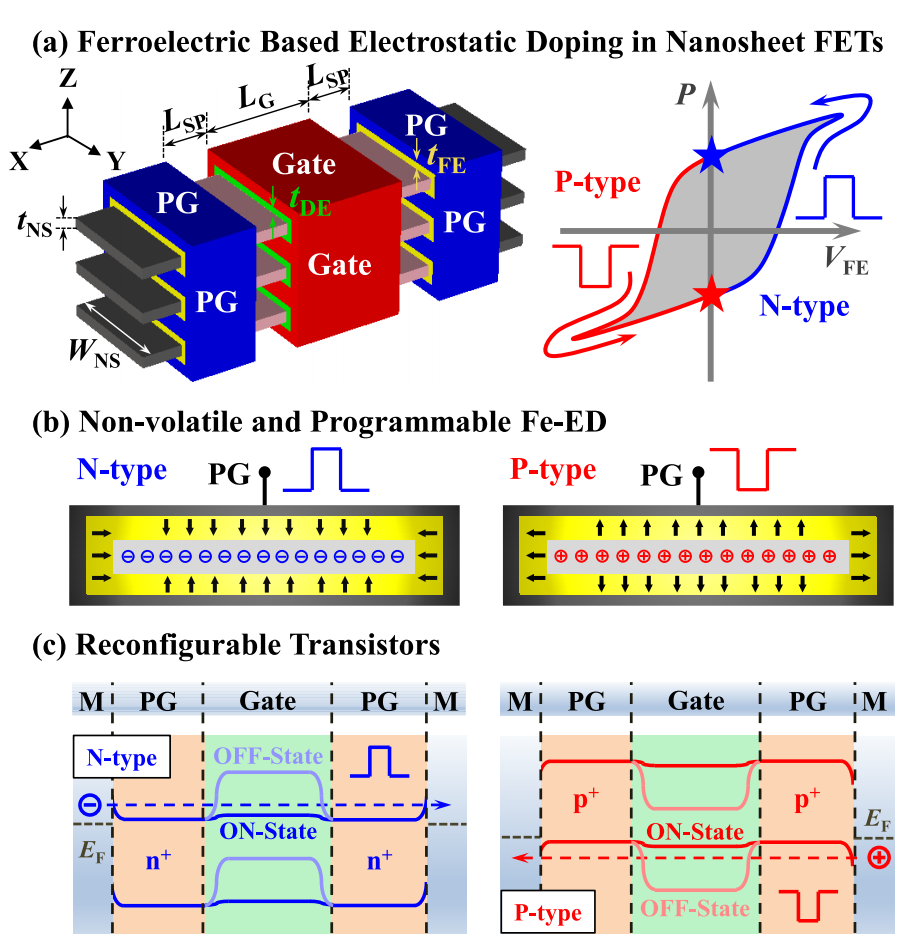

制備過程關(guān)鍵三步:

極性柵極-自對準(zhǔn)控制柵-源漏接觸

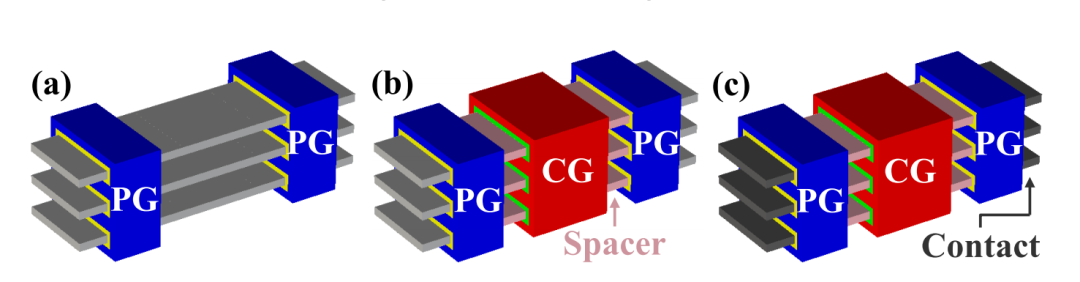

VPG、VGS、VDS均為0時的載流子濃度分布

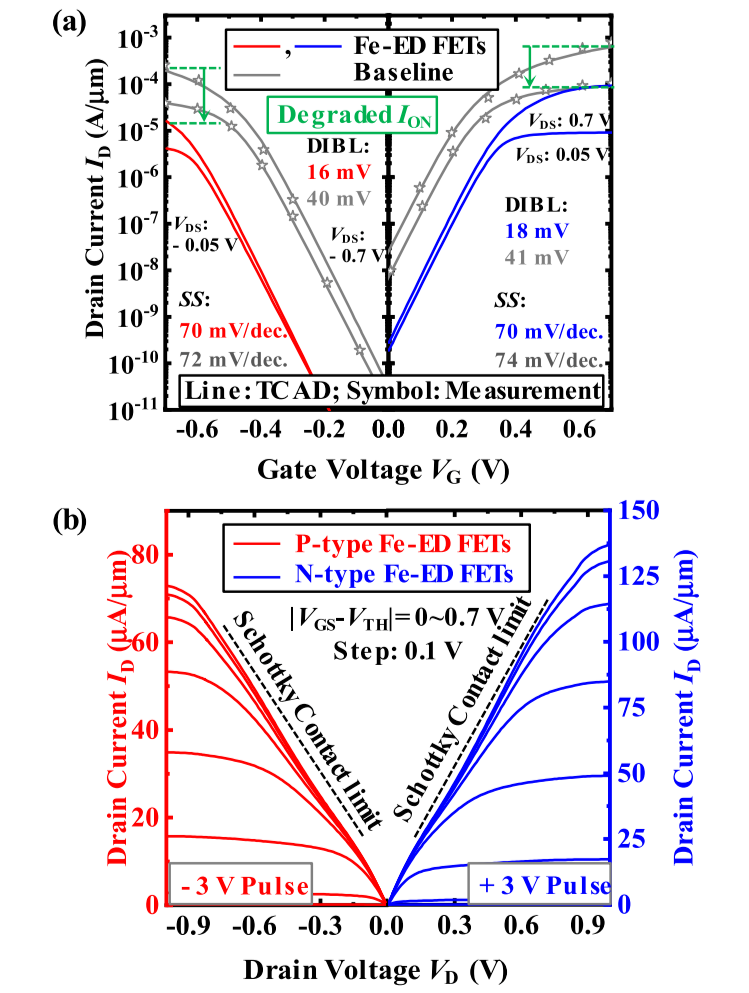

ID-VG曲線和ID-VD曲線

幾類摻雜技術(shù)的成果對比

前景展望

本文所介紹的研究成果實現(xiàn)了無恒定偏置下實現(xiàn)晶體管的非揮發(fā)性和可重構(gòu)性,并具有各種良好的性能改進(jìn),但對于超低漏源電阻的改進(jìn),還需要進(jìn)一步的研究。總而言之,該技術(shù)為先進(jìn)納米器件和和后摩爾新型器件提供了一種新的解決路徑,在forksheet*等高集成度的先進(jìn)工藝中非揮發(fā)性和可控?fù)诫s是必要的。

*forksheet:通過在nanosheet結(jié)構(gòu)中加入電介質(zhì)“墻”隔離同型溝道實現(xiàn)晶體管單元面積縮小的一種晶體管結(jié)構(gòu)。

原文標(biāo)題:科研前線 | 西電靜電摻雜新成果推動新型器件研發(fā)

文章出處:【微信公眾號:芯片揭秘】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

電阻

+關(guān)注

關(guān)注

87文章

5607瀏覽量

174349 -

晶體管

+關(guān)注

關(guān)注

77文章

9979瀏覽量

140681

原文標(biāo)題:科研前線 | 西電靜電摻雜新成果推動新型器件研發(fā)

文章出處:【微信號:ICxpjm,微信公眾號:芯片揭秘】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

耐輻射光電晶體管非密封表面貼裝光耦合器 skyworksinc

多值電場型電壓選擇晶體管結(jié)構(gòu)

晶體管電路設(shè)計(下)

晶體管電路設(shè)計(下) [日 鈴木雅臣]

晶體管與場效應(yīng)管的區(qū)別 晶體管的封裝類型及其特點

燈具揮發(fā)性有機(jī)化合物(VOC)鑒定

晶體管的工作狀態(tài)判斷方法

晶體管的基本工作模式

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

淺析高壓晶體管光耦

NPN晶體管的電位關(guān)系

晶體管電流的關(guān)系有哪些類型 晶體管的類型

PNP晶體管符號和結(jié)構(gòu) 晶體管測試儀電路圖

無恒定偏置下實現(xiàn)晶體管的非揮發(fā)性和可重構(gòu)性

無恒定偏置下實現(xiàn)晶體管的非揮發(fā)性和可重構(gòu)性

評論