芯來科技為方便客戶進(jìn)行基于鴻蒙生態(tài)的RISC-V軟件開發(fā),在Nuclei RISC-V 32位處理器上移植并適配了鴻蒙LiteOS-M內(nèi)核。

目前該內(nèi)核已可支持Nuclei Demo SoC——FPGA評估軟核,和基于芯來科技的RISC-V內(nèi)核的MCU——GD32VF103。

LiteOS-M內(nèi)核

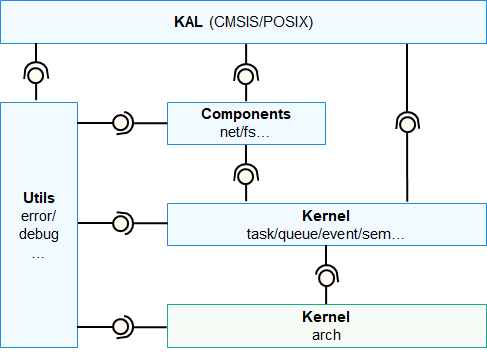

OpenHarmony LiteOS-M內(nèi)核針對MCU類處理器,例如Arm Cortex-M、RISC-V32位的設(shè)備,面向AIoT領(lǐng)域構(gòu)建的輕量級物聯(lián)網(wǎng)操作系統(tǒng)內(nèi)核。此內(nèi)核具有小體積、低功耗、高性能的特點(diǎn)。其代碼結(jié)構(gòu)簡單,主要包括內(nèi)核最小功能集、內(nèi)核抽象層、可選組件以及工程目錄等,分為硬件相關(guān)層以及硬件無關(guān)層,硬件相關(guān)層提供統(tǒng)一的HAL(Hardware Abstraction Layer)接口,提升硬件易適配性,滿足AIoT類型豐富的硬件拓展。

OpenHarmony LiteOS-M核內(nèi)核架構(gòu)圖

芯來開發(fā)板

芯來科技目前有兩款開發(fā)板可以快速體驗(yàn)最新鴻蒙LiteOS-M內(nèi)核:

Nuclei DDR200T——集成了FPGA和通用MCU的RISC-V評估開發(fā)板,以及RV-STAR——基于GD32VF103 MCU的RISC-V評估開發(fā)板。

Nuclei DDR200T開發(fā)板采用12V外部直流電源,包含一個MCU子系統(tǒng)和一個FPGA子系統(tǒng)。

FPGA子系統(tǒng)采用Xilinx XC7A200T-2 FPGA芯片,并且提供板載FPGA JTAG下載器,不需額外配置FPGA下載器即可完成內(nèi)核的燒寫。此外,開發(fā)板還提供豐富的板載存儲(Flash,DDR, eMMC, EEPROM)和豐富的接口資源(數(shù)字,模擬),以及蜂鳥調(diào)試器接口,方便下載調(diào)試。

Nuclei Demo SoC(FPGA評估軟核)就可以燒寫在這塊FPGA子系統(tǒng)上運(yùn)行。

NucleiRV-STAR開發(fā)板

Nuclei RV-STAR開發(fā)板采用GD32VF103VBT6微控制器,結(jié)合芯來科技Bumblebee內(nèi)核,內(nèi)置128KB Flash、32KB SRAM。開發(fā)板外設(shè)資源眾多,包括:

Timer(高級16位定時器*1,通用16位定時器*4)、U(S)ART*5、I2C*2、SPI*3、CAN*2、USBFS*1、ADC*2(16路外部通道)、DAC*2、EXMC*1。開發(fā)板還提供大量接口,包括:USB Type-C接口、Micro USB接口、microSD卡插槽(默認(rèn)沒焊接)、JTAG接口、PMOD接口*2(SPI、I2C)、雙排標(biāo)準(zhǔn)2.54mm排母接口:Arduino兼容接口(外側(cè)),EXMC擴(kuò)展接口(內(nèi)側(cè))以及用戶按鍵*2(復(fù)位、喚醒)。

芯來內(nèi)核

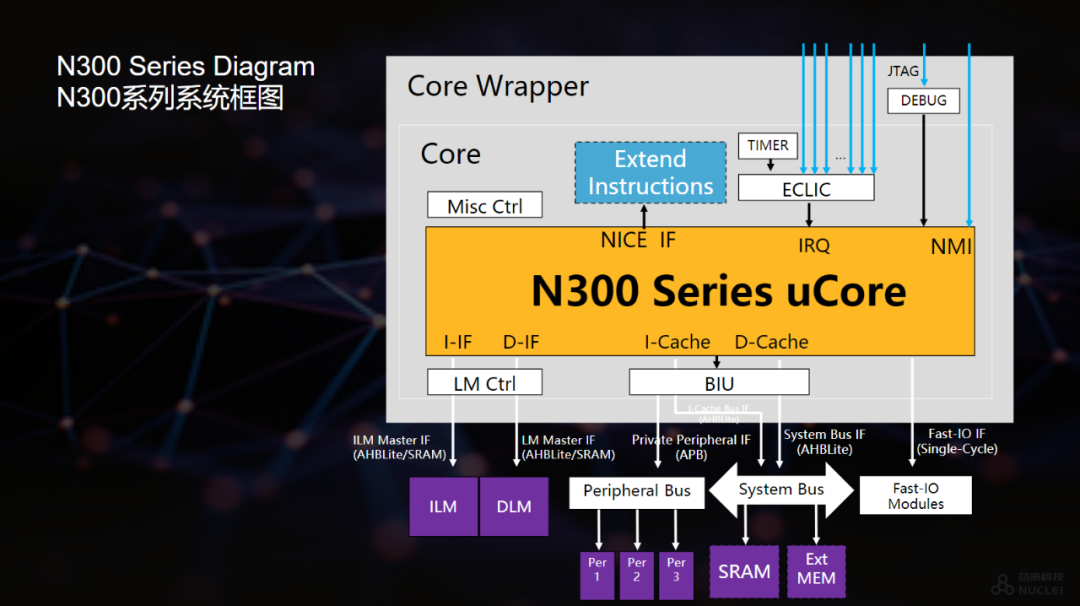

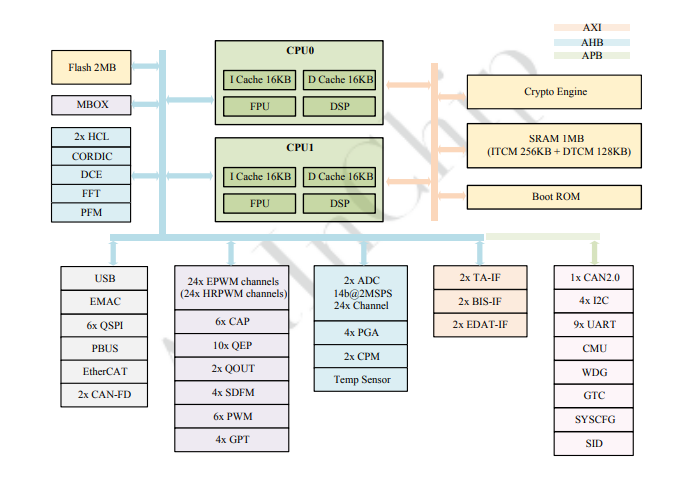

本次OpenHarmony LiteOS-M內(nèi)核支持針對芯來科技N級別內(nèi)核RV32架構(gòu),并采用N307FD內(nèi)核作為使用示例。

N300系列32位超低功耗RISC-V處理器面向機(jī)制能效比且需要DSP,F(xiàn)PU特性的場景而設(shè)計,非常適合對標(biāo)ARM Cortex-M3/M4/M4F/M33內(nèi)核,應(yīng)用于IoT和工業(yè)控制等場景。

芯來LiteOS-M內(nèi)核使用

芯來LiteOS-M內(nèi)核倉庫鏈接如下:https://gitee.com/riscv-mcu/kernel_liteos_m/tree/dev_nuclei/

倉庫內(nèi)整體文件結(jié)構(gòu)直觀明了,在各開發(fā)板對應(yīng)的target文件夾中較為詳細(xì)的列出各文件/文件夾的作用,便于理解和使用。

芯來科技本次支持的所有工程均采用makefile編譯管理,芯來科技GCC工具鏈編譯,資源集中,所有需要的內(nèi)容均可在芯來官網(wǎng)找到。

這里以RV-STAR開發(fā)板為例,介紹倉庫的使用方法:

下載工具鏈并配置驅(qū)動

打開芯來科技文檔與工具頁面,按照以下步驟下載工具鏈:

CentOS或Ubuntu系統(tǒng)請點(diǎn)擊圖中紅框1下載RISC-V GNU工具鏈;

點(diǎn)擊圖中藍(lán)框2-1下載64bit的OpenOCD;

確保make工具版本不低于3.82;

Ubuntu系統(tǒng)使用以下指令安裝make工具

sudo apt-getinstall make

CentOS系統(tǒng)使用以下指令安裝

sudo yum installmake

新建Nuclei文件夾并在此文件夾中新建gcc文件夾和openocd文件夾;

解壓縮之前下載的GNU工具鏈到任意文件夾中,復(fù)制其中bin文件件所在層級的所有內(nèi)容到gcc文件夾中;

同樣解壓縮之前下載的OpenOCD到任意文件夾中,復(fù)制其中bin文件件所在層級的所有內(nèi)容到openocd文件夾中。

工具鏈下載完成后,需要配置驅(qū)動,步驟如下:

連接開發(fā)板到Linux中,確保USB被Linux識別出來;

在控制臺中使用lsusb指令查看信息,參考的打印信息如下:

Bus001Device010: ID0403:6010FutureTechnologyDevicesInternational, LtdFT2232xxxx

將github

https://github.com/riscv-mcu/ses_nuclei_sdk_projects/blob/master/misc/99-openocd.rules

上misc文件夾內(nèi)99-openocd.rules文件復(fù)制到當(dāng)前路徑下,控制臺中輸入以下指令復(fù)制文件到指定路徑下;

sudo cp99-openocd.rules /etc/udev/rules.d/99-openocd.rules

斷開調(diào)試器再重新連接到Linux系統(tǒng)中;

使用ls /dev/ttyUSB*命令查看ttyUSB信息,參考輸出如下:

/dev/ttyUSB0 /dev/ttyUSB1

使用ls -l /dev/ttyUSB1命令查看分組信息,參考輸出如下。可以看到ttyUSB1已經(jīng)加入plugdev組,接下來我們要將自己添加到plugdev組。使用whoami命令查看當(dāng)前用戶名,我們將其記錄為< your_user_name >;

crw-rw-r--1 rootplugdev188, 1 Nov28 12:53/dev/ttyUSB1

使用sudo usermod -a -G plugdev

再次確認(rèn)當(dāng)前用戶名已屬于plugdev組,使用groups命令,可以看到打印信息中有plugdev即成功將當(dāng)前用戶添加至plugdev組。

編譯源碼

請在當(dāng)前控制臺中配置NUCLEI_TOOL_ROOT路徑,假設(shè)Nuclei文件夾所在路徑為/home/Nuclei,輸入:

exportNUCLEI_TOOL_ROOT=/home/Nuclei

或者使用時make選項(xiàng)增加:

NUCLEI_TOOL_ROOT=/home/Nuclei

復(fù)制倉庫代碼到本地。在命令行中輸入:

git clone https://gitee.com/riscv-mcu/kernel_liteos_m.git

復(fù)制代碼到本地;

打開至代碼根目錄下

/target/riscv_nuclei_gd32vf103_soc_gcc/GCC

輸入:makeall

開始編譯,編譯結(jié)束后部分參考輸出如下:

text data bss dec hex filename 243301121676841210a0fa build/Nuclei-rvstar-gd32vf103-soc.elf

若編譯前想清理工程,請使用:

makeclean

下載調(diào)試、運(yùn)行

調(diào)試或運(yùn)行前請先連接RV-STAR開發(fā)板,確保已按照環(huán)境配置中驅(qū)動配置部分配置完成。

同樣配置好NUCLEI_TOOL_ROOT路徑,并打開至代碼根目錄下的:

/target/riscv_nuclei_gd32vf103_soc_gcc/GCC

輸入:

makedebug

進(jìn)入GDB調(diào)試;

等待到進(jìn)入GDB調(diào)試界面時,輸入:

load

下載編譯好的elf文件,就可以開始調(diào)試;

若想直接運(yùn)行,請同樣在調(diào)試時所在位置輸入:

makeupload

運(yùn)行時可以查看串口打印內(nèi)容,使用串口查看工具,這里以minicom為例,若未安裝此工具可自行安裝或使用其他串口查看工具。打開控制臺,輸入:

minicom-D /dev/ttyUSB1 -b 115200

打開串口查看工具。

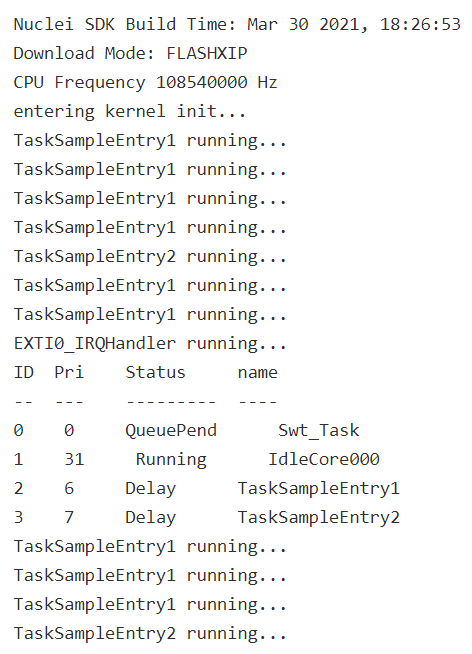

運(yùn)行時參考輸出如下:

總結(jié)

本次芯來RISC-V內(nèi)核支持LiteOS-M內(nèi)核完成了基于ECLIC的OpenHarmony LiteOS-M內(nèi)核任務(wù)調(diào)度移植適配工作,以及芯來內(nèi)核timer移植適配工作。編譯上采用make編譯管理系統(tǒng),各參數(shù)區(qū)分配置,簡單易懂。完全適配芯來GCC編譯器,資源集中,便于查找。使用上簡單易懂,僅兩條指令可完成編譯運(yùn)行。針對不同的開發(fā)板創(chuàng)建了不同的工程,可直接運(yùn)行使用。在根目錄下target文件夾內(nèi),各開發(fā)板對應(yīng)的工程文件夾配有較為詳細(xì)的使用說明,可參考說明搭建編譯運(yùn)行環(huán)境。

編輯:jq

-

dsp

+關(guān)注

關(guān)注

555文章

8136瀏覽量

354756 -

芯片

+關(guān)注

關(guān)注

459文章

52030瀏覽量

434772 -

鴻蒙系統(tǒng)

+關(guān)注

關(guān)注

183文章

2638瀏覽量

67596

原文標(biāo)題:芯來科技RISC-V處理器支持鴻蒙LiteOS-M內(nèi)核

文章出處:【微信號:nucleisys,微信公眾號:芯來科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

匠芯創(chuàng)科技M76P00_M73P00_Datasheet中文數(shù)據(jù)手冊免費(fèi)下載 RISC-V內(nèi)核 主頻552MHz的DSP實(shí)時處理器

匠芯創(chuàng)科技M7000系列選型表分享 RISC-V內(nèi)核的高性能DSP實(shí)時處理器 適配機(jī)器人

2025芯來RISC-V技術(shù)研討會蘇州站成功舉辦

芯來科技攜手芯芒科技發(fā)布RISC-V CPU系統(tǒng)仿真平臺

全國首個!深開鴻LiteOS-M操作系統(tǒng)內(nèi)核榮獲EAL5+安全認(rèn)證!

Imagination放棄RISC-V處理器內(nèi)核開發(fā)

HighTec C/C++編譯器套件全面支持芯來RISC-V IP

賽昉科技發(fā)布全新RISC-V處理器內(nèi)核Dubhe-83

Rivos全新產(chǎn)品采用Andes晶心科技NX45 RISC-V處理器

《RISC-V能否復(fù)制Linux 的成功?》

RISC-V內(nèi)核的32位通用微控制器 GD32VF103芯片簡介

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RT-Thread Safety AUTO成功適配芯來RISC-V車規(guī)內(nèi)核

請問ESP32s3 ULP RISC-V協(xié)處理器是否支持ADC的讀取?

算能全系列RISC-V處理器進(jìn)入PLCT實(shí)驗(yàn)室6.6內(nèi)核維護(hù)工程

芯來科技RISC-V處理器將支持鴻蒙LiteOS-M內(nèi)核

芯來科技RISC-V處理器將支持鴻蒙LiteOS-M內(nèi)核

評論