在本系列的前幾篇文章中 ( "人工智能引發能源問題,我們該怎么辦 (一) “ 和”在 "人工智能引發能源問題,我們該怎么辦 (二)"),我們討論了 Dennard Scaling 和摩爾定律的細目以及對專用和適應性加速器的需求。然后,我們深入研究了功耗問題,并討論了網絡壓縮的高級優勢。

在這第三篇文章中,我們將探討專門構建的“計算有效”神經網絡模型的優點和挑戰。

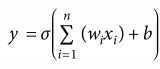

神經網絡可以被歸類為一組大致模仿人腦建模方式的算法,能夠通過引入新數據來完成“學習”過程。事實上,開發專用的“計算高效型”神經網絡模型能提供大量優勢。然而,為了確保模型的有效性,需要考慮幾項關鍵需求。

關鍵點之一是在實現推斷加速器(或就此點而言,廣義的硬件加速器)時應采用何種方式訪問存儲器。在機器學習 (ML) 推斷范疇內,我們特別需要考慮如何將權重和中間激活值一起存儲。過去幾年里已有多種方法投入使用并獲得不同程度的成功。相關的架構選擇帶來的影響十分顯著:

時延:對 L1、L2 和 L3 存儲器的訪問表現出相對較低的時延。如果與下一個圖形運算有關的權重和激活值被緩存起來,那么我們就能保持合理水平的效率。然而,如果我們要從外部 DDR 提取數據,就會發生流水線停頓,進而影響時延和效率。

功耗:訪問外部存儲器的能耗至少比訪問內部存儲器大一個數量級。

計算飽和:一般而言,應用要么受計算限制,要么受存儲器限制。這可能會影響給定推斷范式中可實現的 GOP/TOP,而且在某些情況下,這種影響不可小視。如果被部署的具體網絡的實際性能是 1 TOP,那么使用能達到 10 TOP 峰值性能的推斷引擎價值就不大。

在此基礎上更進一步,考慮到訪問現代賽靈思器件里的內部 SRAM(熟悉賽靈思 SoC 的人也稱其為 BRAM 或 UltraRAM)的能耗大約在幾微微焦耳,與訪問外部 DRAM 的能耗相比,低大約兩個數量級。

我們可以考慮將 TPUv1 作為架構示例。TPUv1 內置有一個 65,536 INT8 MAC 單元,與 28MB 的片上存儲器結合,用于存儲中間激活值。權重從外部 DDR 提取。TPUv1 的理論峰值性能是 92 TOPS。

圖 1:TPUv1 架構

參考資料:Jouppi 等,2017 年,https://arxiv.org/ftp/arxiv/papers/1704/1704.04760.pdf

TPU 是其中一種非常普遍的 Tensor 加速器。它使用復雜的編譯器來調度圖形運算。這種 TPU 對于特定工作負載(引用 CNNO 的速率達到 86 TOPS)體現出極為優異的吞吐效率。然而,CNN 的計算/內存引用比低于 MLP 和 LSTM。因此我們可以看出這些特定的工作負載受存儲器限制。在必須將新權重加載到矩陣單元中時,會導致流水線停頓,CNN1 性能也就會隨之劣化(14.1 TOPS)。

圖 2:各種網絡拓撲下 TPUv1 的極限性能水平

參考資料:Jouppi 等,2017 年,

https://arxiv.org/ftp/arxiv/papers/1704/1704.04760.pdf

神經網絡架構對性能有巨大影響,而且對于選擇推斷解決方案而言,峰值性能指標的價值微乎其微(除非我們能為需要加速的特定工作負載實現高水平的效率)。如今,眾多 SoC、ASSP 和 GPU 廠商繼續為 LeNet、AlexNet、VGG、GoogLeNet 和 ResNet 等經典圖像分類模型推廣性能測試基準。然而,圖像分類任務的實際用例數量有限,而許多時候這種模型只是用作對象檢測與分割等更復雜的任務的后臺特征提取器。

更貼近現實的實際可部署模型的示例包括對象檢測與分割。盡管眾多市售半導體器件標榜可提供數十 TOP 的性能,而這又與不得不花長時間為 YOLOv3 和 SSD 等網絡辛苦找尋正式的 IPS 性能基準測試的現狀有何關聯?開玩笑的說,如果只是要在云存儲中簡單查找照片,比如找出您的貓的照片,我看這真不是什么問題:

圖 3:作者收養的家貓“TumbleWeed”

大量開發者在首次嘗試設計帶有 AI 功能的產品時往往以不能滿足性能要求而告終,迫使他們在設計中途遷移到不同的架構上。這不足為奇。如果這么做意味著需要同時對 SOM 基板的軟硬件進行重新構建,難度將不可小覷。選擇賽靈思 SoC 的主要原因在于,與競爭對手的解決方案不同的是,賽靈思推斷解決方案能在保持處理器和推斷加速器架構不變的情況下,直接提供超過一個數量級的性能縮放。

2017 年谷歌的一個研發團隊(Howard 等,《MobileNet:面向移動視覺應用的高效卷積神經網絡》https://arxiv.org/pdf/1704.04861.pdf )發表了針對移動應用的一類新的模型。MobileNet 的優勢在于它能在保持高精度水平的同時,顯著降低計算成本。MobileNet 網絡采用的重大創新之一是深度可分卷積。在經典卷積中,每個輸入通道對每個輸出通道都有影響。如果我們有 100 個輸入通道和 100 個輸出通道,就有 100x100 條虛擬路徑。然而對深度卷積而言,我們將卷積層劃分為 100 個群組,因此只得到 100 條路徑。每個輸入通道僅與一個輸出通道相連接,這樣就能節省大量計算。

圖 4:經典卷積和深度卷積的連接方式

參考資料:Song Yao,Hotchips Hc30,第 8 節:

https://www.hotchips.org/archives/2010s/hc30/

其結果之一就是 MobileNet 的計算/內存引用比得以下降,這意味著存儲器帶寬和時延對實現高吞吐量來說起著至關重要的作用。

可惜的是,計算效率高的網絡未必適合用硬件實現。在理想情況下,時延應隨 FLOP 的降低而呈線性比例下降。然而誠如老話所言,天下沒有免費的午餐。例如,根據下面的比較,MobileNetv2 的計算工作負載不足 ResNet50 的計算工作負載的十分之一,然而時延并未體現出相同的降幅。

圖 5:MobileNet 與 ResNet50 的計算量及時延對比

參考資料:Song Yao,Hotchips Hc30,第 8 節:

https://www.hotchips.org/archives/2010s/hc30/

從上面的分析中可以看出,時延并未隨 FLOP 的降低發生成比例的 12 倍下降。

那么我們如何解決這個問題?如果我們比較片外通信/計算比,會發現 MobileNet 的模式與 VGG 有很大不同。就 DWC 層而言,我們可以看到該比例為 0.11。因為 PE 陣列中的眾多單元猶如數據中心內的“黑暗”服務器,不從事任何有用的工作,只純粹消耗功耗并占用晶片面積,導致加速器受存儲器限制,效率水平下降。

圖 6:VGG16 與 MobileNetv1 的片外通信/計算比

參考資料:Song Yao,Hotchips Hc30,第 8 節:

https://www.hotchips.org/archives/2010s/hc30/

賽靈思之所以推出 DPUv1,是為了加速常規卷積(以及其他運算)。常規卷積要求縮減輸入通道數量。這種縮減更適合用于硬件推斷,因為它提高了計算/權重存儲比及計算/激活值存儲比。從計算能耗與存儲能耗相權衡的角度來看,這是一種非常優秀的做法。基于 ResNet 的網絡在高性能應用中得到如此廣泛的部署的原因之一在于,與眾多傳統的主干架構相比,使用 ResNet 能提高計算/內存引用比。

深度卷積無法實現這樣的通道數縮減。存儲器性能變得更加重要。

為了開展推斷,我們一般將 DWC 卷積與 PWC 卷積融合,并將 DWC 激活值存儲在片上存儲器里,然后立即啟動 1x1 PWC。就原始 DPU 而言,沒有為 DWC 提供專門的硬件支持,因此效率低于理想水平:

圖 7:MobileNet 與 ResNet50 的運算與時延對比 – DPUv1(無原生 DWC 支持)

參考資料:Song Yao,Hotchips Hc30,第 8 節:

https://www.hotchips.org/archives/2010s/hc30/

為了在硬件中提高 DWC 性能,我們對賽靈思 DPU 中的處理單元 (PE) 的功能進行了修改,并將 DWC 運算符與點卷積融合。第一層處理完畢一個輸出像素后,激活值立即流水線到 1x1 卷積(通過 DPU 中的片上 BRAM 存儲器),而無需寫入到 DRAM。我們可以運用這種專用方法顯著提高部署在 DPU 上的 MobileNet 的效率。

圖 8:DPUv2,專用 DWC 處理單元

參考資料:Song Yao,Hotchips Hc30,第 8節:

https://www.hotchips.org/archives/2010s/hc30/

采用這種改進型 DPUv2 架構,我們能夠顯著提高 MNv1 推斷的效率。此外,通過提高片上存儲器的容量,我們還能進一步提高它的效率,使之與我們在 ResNet50 上獲得的結果相媲美。所有這些都是在 CPU 和硬件架構不變的情況下實現的!

圖 9:MobileNet 與 ResNet50 的時延比較,DPUv1 對比 DPUv2(支持 DWC)

參考資料:Song Yao,Hotchips Hc30,第 8 節:

https://www.hotchips.org/archives/2010s/hc30/

廣泛采用的做法是互不關聯地分別優化推斷硬件和神經網絡模型。應該注意到的是,網絡一般使用 GPU 進行訓練,然后在邊緣部署在架構顯著不同的 SoC 或 GPU 上。為真正優化性能,我們必須適配硬件,才能高效完成模型(不一定對硬件友好)部署。在這種情況下,自適應硬件的主要優勢在于賽靈思器件提供在流片后繼續聯合演進軟硬件的特有能力。

為進一步理解這個問題,不妨考慮題為《彩票假說》的一篇獨創論文(Frankle 和 Carbin,2019 年https://arxiv.org/pdf/1803.03635.pdf)的寓意。在該論文(摘得 2019 年國際學習表征大會桂冠的兩篇論文之一)中,作者“詳細闡述了一種假說”,即“含有子網絡(中獎彩票)的密集隨機初始化前饋網絡,如果單獨訓練,測試精度可媲美經過類似數量(訓練)迭代的原始網絡”。顯然根據這個假說,網絡剪枝的前景仍然光明,AutoML 等技術將很快為我們指明網絡發現與優化過程中的“中獎彩票”。

同樣地,為保證在邊緣實現高效、高精度的部署,當今最優秀的解決方案仍保留著傳統主干架構的通道剪枝。這些主干架構的部署效率也許不高,但這些主干架構的半自動化通道剪枝可提供極為高效的結果(參見賽靈思 VGG-SSD 示例)。因此,我可以將這個假說解釋成:只要您選擇的下一個推斷架構能讓您的設計永不過時,您就可以在今天輕松地找到“中獎彩票”。它能幫助您充分發揮未來網絡架構和優化技術的優勢,同時向您的客戶保證產品經久不衰。

圖 9:我個人的“中獎彩票”假說

我可以非常肯定的是,從“彩票假說”衍生出的未來研究有望引領我們開發出新一代剪枝技術,贏得更大程度的效率提升。此外,我感覺只有采用可提供多維度可擴展性的自適應硬件才能收獲這樣的成果。這并非純粹是我的直覺。

購買ZCU104,下載Vitis-AI,立刻開啟您駛向未來 AI 的旅程吧。

責任編輯:lq

-

存儲器

+關注

關注

38文章

7648瀏覽量

167284 -

神經網絡

+關注

關注

42文章

4814瀏覽量

103525 -

人工智能

+關注

關注

1806文章

48996瀏覽量

249187

原文標題:人工智能引發能源問題,我們該怎么辦?(三)

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

無刷電機小波神經網絡轉子位置檢測方法的研究

神經網絡專家系統在電機故障診斷中的應用

BP神經網絡的優缺點分析

什么是BP神經網絡的反向傳播算法

如何訓練BP神經網絡模型

深度學習入門:簡單神經網絡的構建與實現

人工神經網絡的原理和多種神經網絡架構方法

專門構建的“計算有效”神經網絡模型的優點和挑戰

專門構建的“計算有效”神經網絡模型的優點和挑戰

評論