本系列文章主要針對(duì)FPGA初學(xué)者編寫,包括FPGA的模塊書寫、基礎(chǔ)語法、狀態(tài)機(jī)、RAM、UART、SPI、VGA、以及功能驗(yàn)證等。將每一個(gè)知識(shí)點(diǎn)作為一個(gè)章節(jié)進(jìn)行講解,旨在更快速的提升初學(xué)者在FPGA開發(fā)方面的能力,每一個(gè)章節(jié)中都有針對(duì)性的代碼書寫以及代碼的講解,可作為讀者參考。

16

第十六章:SPI

SPI簡介

電子系統(tǒng)設(shè)計(jì)中,往往被IIC/SPI/UART等總線搞的暈頭轉(zhuǎn)向,本文詳細(xì)介紹SPI總線的接口協(xié)議和應(yīng)用。

SPI總線是一種同步串行外設(shè)接口,它可以使MCU/FPGA/DSP等控制器與各種外圍設(shè)備以串行方式進(jìn)行通信。其具有通信速度快,同步設(shè)計(jì)以及控制協(xié)議簡單等特點(diǎn),是電子系統(tǒng)設(shè)計(jì)的常用選擇之一。很多芯片的控制都提供SPI接口。

SPI 是英語 Serial Peripheral Interface 的縮寫,顧名思義就是串行外圍設(shè)備接口。是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,最早由Motorola提出的。由于其簡單易用的特性,現(xiàn)在很多的芯片都集成了SPI通信協(xié)議。

SPI傳輸串行數(shù)據(jù)時(shí)首先傳輸最高位。波特率可以高達(dá)5Mbps,具體速度大小取決于SPI硬件。例如,Xicor公司的SPI串行器件傳輸速度能達(dá)到5MHz。

SPI flash 芯片應(yīng)用十分廣泛,在很多電子產(chǎn)品上面或多或少都有它的蹤影,如手機(jī)、數(shù)碼、液晶顯示器、機(jī)頂盒、電腦主板等。主要應(yīng)用在EEPROM,F(xiàn)LASH,實(shí)時(shí)時(shí)鐘,AD轉(zhuǎn)換器,還有數(shù)字信號(hào)處理器和數(shù)字信號(hào)解碼器等,也是很多復(fù)雜芯片參數(shù)配置的常用接口。

SPI總線介紹

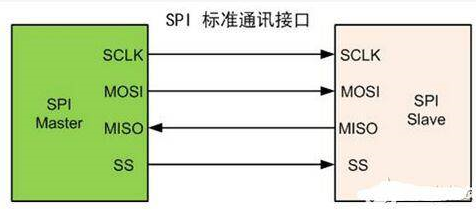

SPI 接口一般使用 4 條線通信,包括片選線(cs_n)、時(shí)鐘線(sclk/sck)、輸入數(shù)據(jù)線(sdi/miso) 和輸出數(shù)據(jù)線(sdo/mosi):

SCLK:串行時(shí)鐘線,由主設(shè)備產(chǎn)生;

MISO:主設(shè)備數(shù)據(jù)輸入,從設(shè)備輸出;

MOSI:主設(shè)備數(shù)據(jù)輸出,從設(shè)備輸入;

CS:從設(shè)備片選信號(hào),由主設(shè)備控制。

其中CS是片選信號(hào),可以預(yù)先規(guī)定其為高使能或者低使能有效時(shí),對(duì)此芯片的操作才有效。這就允許在同一總線上連接多個(gè)SPI設(shè)備。

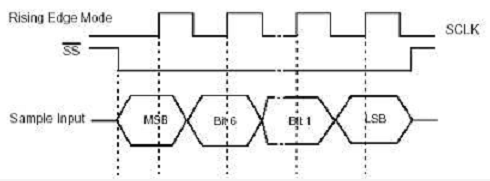

SPI接口在Master控制下產(chǎn)生的從器件使能信號(hào)和時(shí)鐘信號(hào),兩個(gè)雙向移位寄存器按位傳輸進(jìn)行數(shù)據(jù)交換,傳輸數(shù)據(jù)高位在前,低位在后(MSB)。在SCK的下降沿?cái)?shù)據(jù)改變,上升沿一位數(shù)據(jù)被存入移位寄存器,如圖所示:

SPI總線通信特點(diǎn)

1.采用主-從模式(Master-Slave) 的控制方式

SPI 規(guī)定了兩個(gè) SPI 設(shè)備之間通信必須由主設(shè)備 (Master) 來控制從設(shè)備 (Slave). 一個(gè) Master 設(shè)備可以通過提供 Clock 以及對(duì) Slave 設(shè)備進(jìn)行片選來控制多個(gè) Slave 設(shè)備。

2.采用同步方式(Synchronous)傳輸數(shù)據(jù)

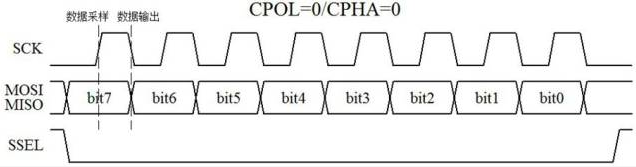

Master 設(shè)備會(huì)根據(jù)將要交換的數(shù)據(jù)來產(chǎn)生相應(yīng)的時(shí)鐘脈沖(Clock Pulse), 時(shí)鐘脈沖組成了時(shí)鐘信號(hào)(Clock Signal) , 時(shí)鐘信號(hào)通過時(shí)鐘極性 (CPOL) 和 時(shí)鐘相位 (CPHA) 控制著兩個(gè) SPI 設(shè)備間何時(shí)數(shù)據(jù)交換以及何時(shí)對(duì)接收到的數(shù)據(jù)進(jìn)行采樣, 來保證數(shù)據(jù)在兩個(gè)設(shè)備之間是同步傳輸?shù)摹?/p>

3.數(shù)據(jù)交換(Data Exchanges)

SPI設(shè)備間的數(shù)據(jù)傳輸之所以又被稱為數(shù)據(jù)交換, 是因?yàn)?SPI 協(xié)議規(guī)定一個(gè) SPI 設(shè)備不能在數(shù)據(jù)通信過程中僅僅只充當(dāng)一個(gè)"發(fā)送(Transmitter)" 或者 "接收者(Receiver)". 在每個(gè) Clock 周期內(nèi), SPI 設(shè)備都會(huì)發(fā)送并接收一個(gè) bit 大小的數(shù)據(jù), 相當(dāng)于該設(shè)備有一個(gè) bit 大小的數(shù)據(jù)被交換了。

SPI FLASH讀寫介紹

對(duì)flash芯片的操作,一般包括對(duì)flash芯片的擦除,編程和讀取,各大廠商的SPI flash芯片都大同小異,操作命令基本是沒什么變化的,當(dāng)我們拿到一款芯片,要特別注意芯片的容量,操作分區(qū)等。

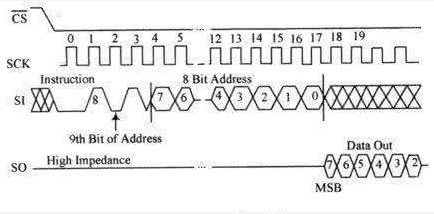

其實(shí),無論是對(duì)芯片的擦除,編程還是讀取操作,我們大致可以按照以下的套路來:寫命令---寫地址---寫(讀)數(shù)據(jù)。正如以下的時(shí)序圖一樣清晰明了,我們先把片選信號(hào)拉低,再依次寫指令,地址和數(shù)據(jù),就可以對(duì)FLASH芯片進(jìn)行操作。

在第十七章中將通過SPI總線控制Flash為例講解擦除的實(shí)現(xiàn)。

責(zé)任編輯:lq

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614258 -

通信

+關(guān)注

關(guān)注

18文章

6177瀏覽量

137381 -

SPI

+關(guān)注

關(guān)注

17文章

1784瀏覽量

94786

原文標(biāo)題:FPGA入門系列15--SPI

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

看完這篇,SPI其實(shí)也很簡單嘛(可下載)

對(duì)于一款新的BSP如何添加SPI驅(qū)動(dòng)

【國產(chǎn)FPGA必備教程】——紫光同創(chuàng)FPGA圖像視頻教程,適用于小眼睛FPGA盤古全系列開發(fā)板

你知道什么是SPI嗎?一文入門,簡單易懂

I2C總線與SPI總線的比較

SH32F9001的SPI介紹與應(yīng)用

請(qǐng)問FPGA同時(shí)連兩片AMC7836時(shí)SPI通信是否會(huì)互擾?

請(qǐng)問DAC80508M的SPI總線支持三線模式嗎?如果SPI總線上面只掛了一個(gè)DAC80508M,CS腳可以直接接地嗎?

采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南

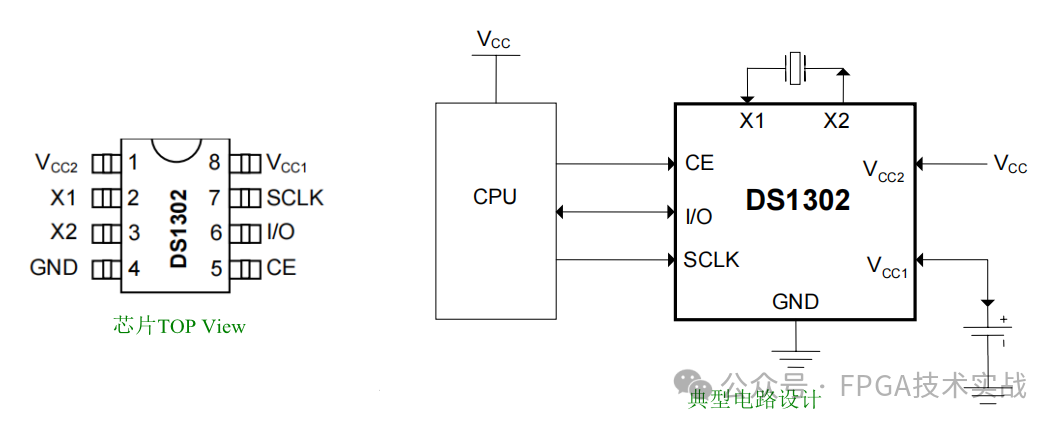

DS1302芯片與FPGA之間SPI通信原理

TDA4系列的SPI啟用和驗(yàn)證

SPI總線的定義和特點(diǎn)

【GD32 MCU 入門教程】GD32 MCU 常見外設(shè)介紹(8)SPI 模塊介紹

FPGA入門系列15--SPI總線介紹

FPGA入門系列15--SPI總線介紹

評(píng)論