在PCB的EMC設計考慮中,首先涉及的便是層的設置;單板的層數由電源、地的層數和信號層數組成;在產品的EMC設計中,除了元器件的選擇和電路設計之外,良好的PCB設計也是一個非常重要的因素。 PCB的EMC設計的關鍵,是盡可能減小回流面積,讓回流路徑按照我們設計的方向流動。而層的設計是PCB的基礎,如何做好PCB層設計才能讓PCB的EMC效果最優呢?

1、PCB層的設計思路:PCB疊層EMC規劃與設計思路的核心就是合理規劃信號回流路徑,盡可能減小信號從單板鏡像層的回流面積,使得磁通對消或最小化。 1、單板鏡像層 鏡像層是PCB內部臨近信號層的一層完整的敷銅平面層(電源層、接地層)。主要有以下作用: (1)降低回流噪聲:鏡像層可以為信號層回流提供低阻抗路徑,尤其在電源分布系統中有大電流流動時,鏡像層的作用更加明顯。 (2)降低EMI:鏡像層的存在減少了信號和回流形成的閉合環的面積,降低了EMI; (3)降低串擾:有助于控制高速數字電路中信號走線之間的串擾問題,改變信號線距鏡像層的高度,就可以控制信號線間串擾,高度越小,串擾越小; (4)阻抗控制,防止信號反射。

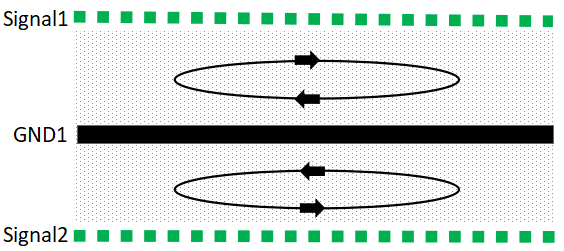

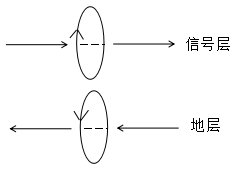

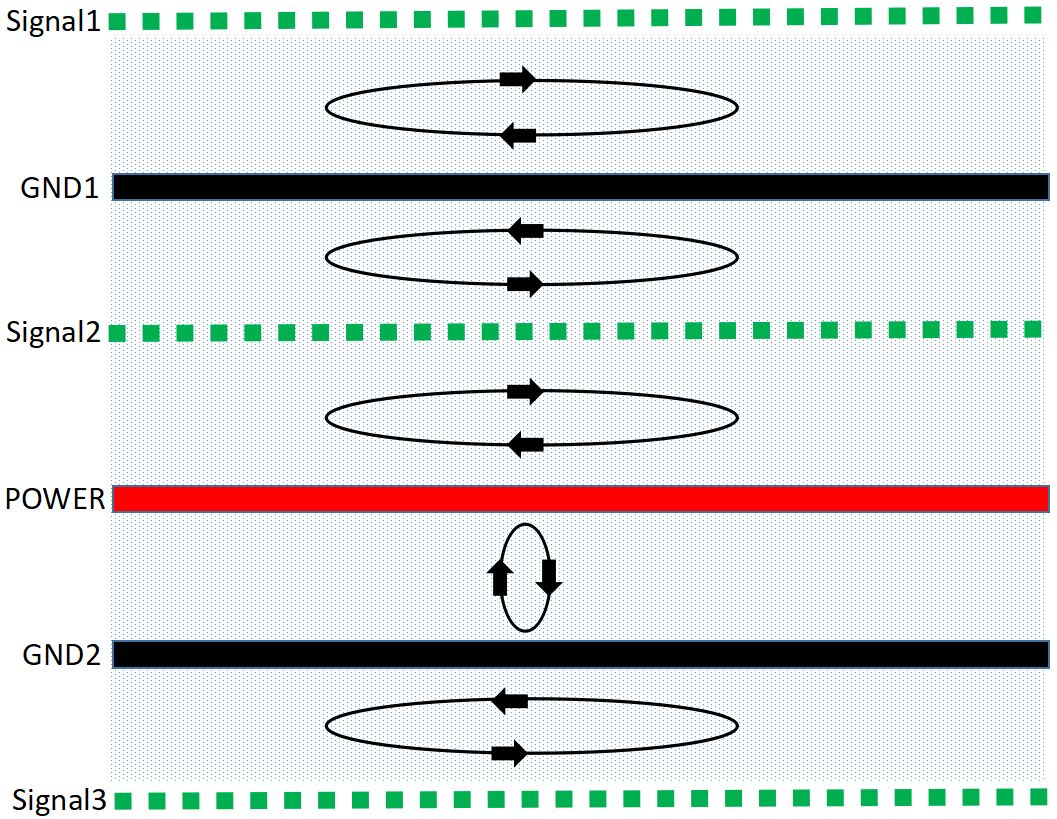

2、鏡像層的選擇 (1)電源、地平面都能用作參考平面,且對內部走線有一定的屏蔽作用; (2)相對而言,電源平面具有較高的特性阻抗,與參考電平存在較大的電勢差,同時電源平面上的高頻干擾相對比較大; (3)從屏蔽的角度,地平面一般均作了接地的處理,并作為基準電平參考點,其屏蔽效果遠遠優于電源平面; (4)選擇參考平面時,應優選地平面,次選電源平面。 2、磁通對消原理: 根據麥克斯韋方程,分立的帶電體或電流,它們之間的一切電的及磁的作用都是通過它們之間的中間區域傳遞的,不論中間區域是真空還是實體物質。在PCB中磁通總是在傳輸線中傳播的,如果射頻回流路徑平行靠近其相應的信號路徑,則回流路徑上的磁通與信號路徑上的磁通是方向相反的,這時它們相互疊加,則得到了通量對消的效果。 3、磁通對消的本質就是信號回流路徑的控制,具體示意圖如下:

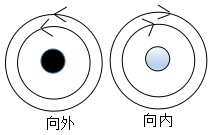

4、如何用右手定則來解釋信號層與地層相鄰時磁通對消效果,解釋如下: (1)當導線上有電流流過時,導線周圍便會產生磁場,磁場的方向以右手定則來確定。 (2)當有兩條彼此靠近且平行的導線,如下圖所示,其中一個導體的電流向外流出,另一個導體的電流向內流入,如果流過這兩根導線的電流分別是信號電流和它的回流電流,那么這兩個電流是大小相等方向相反的,所以它們的磁場也是大小相等,而方向是相反的,因此能相互抵消。

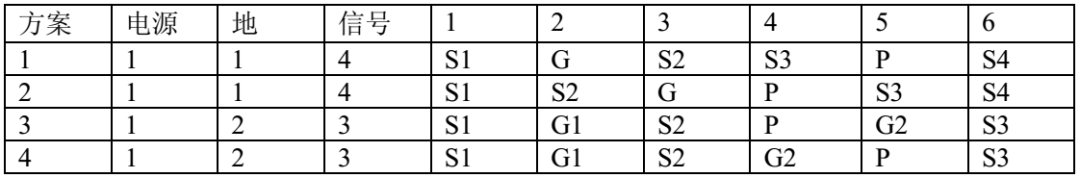

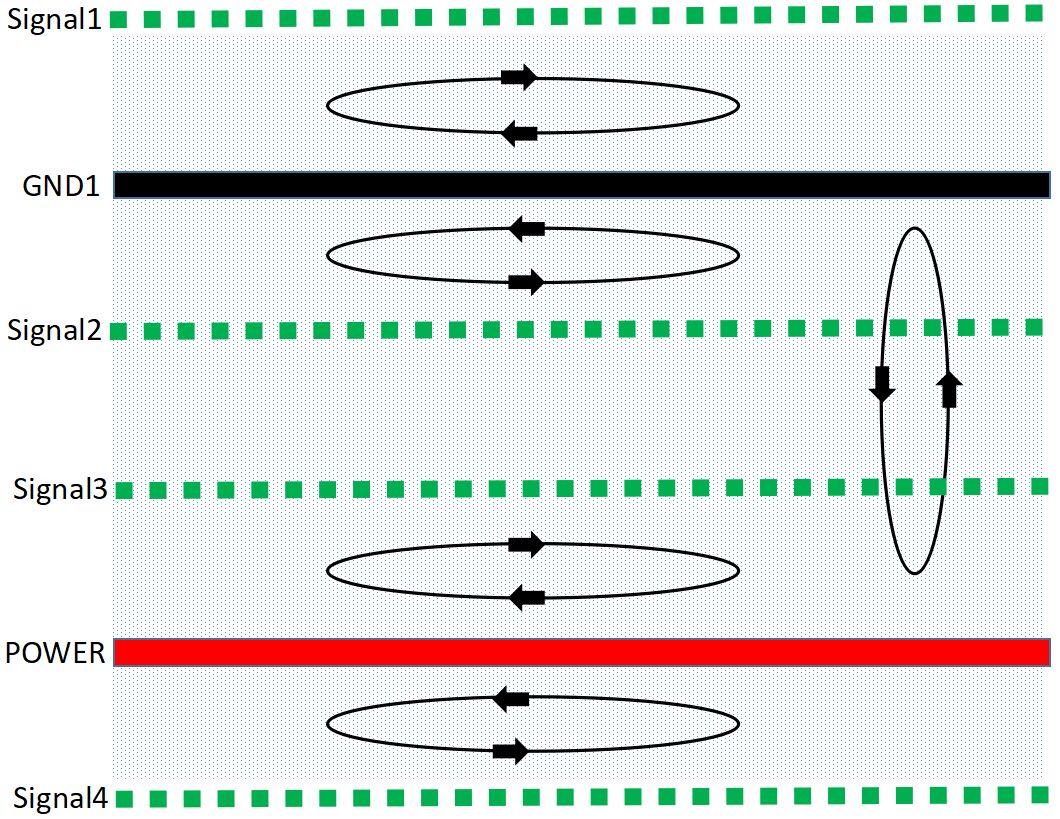

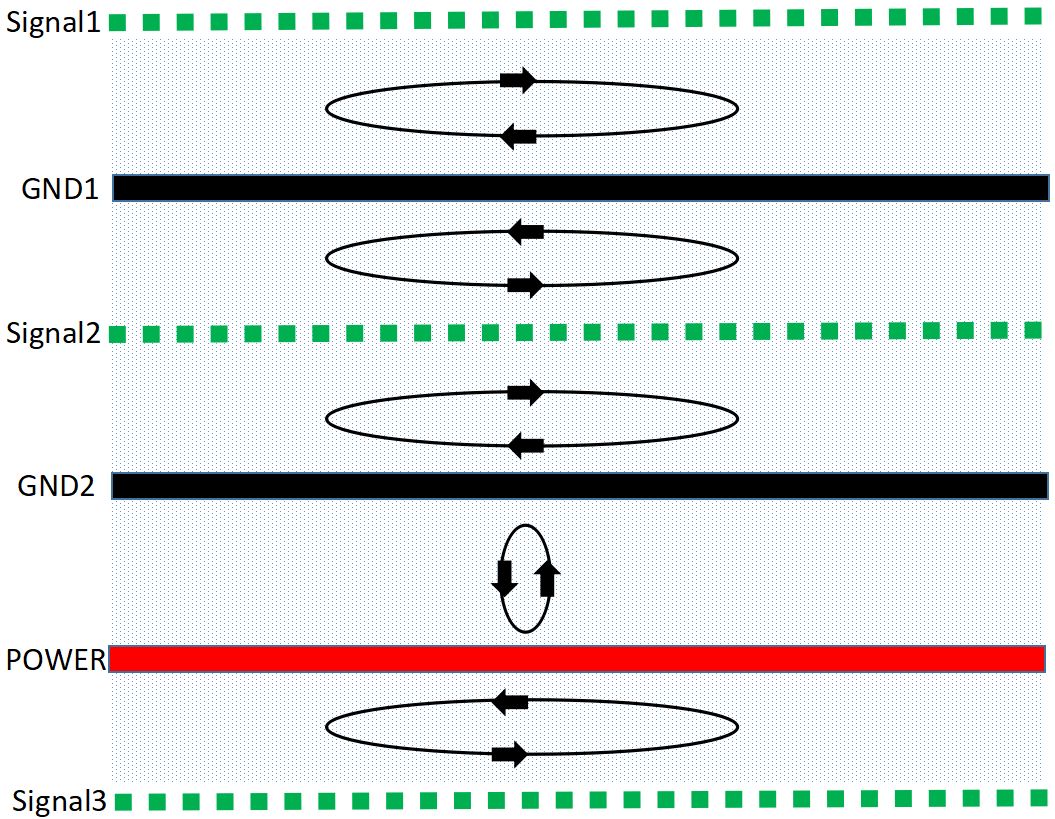

5、六層板設計實例

1、對于六層板,優先考慮方案3;

分析: (1)由于信號層與回流參考平面相鄰,S1、S2、S3相鄰地平面,有最佳的磁通抵消效果,優選布線層S2,其次S3、S1。 (2)電源平面與GND平面相鄰,平面間距離很小,有最佳的磁通抵消效果和低的電源平面阻抗。 (3)主電源及其對應的地布在4、5層,層厚設置時,增大S2-P之間的間距,縮小P-G2之間的間(相應縮小G1-S2層之間的間距),以減小電源平面的阻抗,減少電源對S2的影響。 2、在成本要求較高的時候,可采用方案1;

分析: (1)此種結構,由于信號層與回流參考平面相鄰,S1和S2緊鄰地平面,有最佳的磁通抵消效果; (2)電源平面由于要經過S3和S2到GND平面,差的磁通抵消效果和高的電源平面阻抗; (3)優選布線層S1、S2,其次S3、S4。 3、對于六層板,備選方案4

分析: 對于局部、少量信號要求較高的場合,方案4比方案3更適合,它能提供極佳的布線層S2。 4、最差EMC效果,方案2

分析: 此種結構,S1和S2相鄰,S3與S4相鄰,同時S3與S4不與地平面相鄰,磁通抵消效果差。 6、總結PCB層設計具體原則: (1)元件面、焊接面下面為完整的地平面(屏蔽); (2)盡量避免兩信號層直接相鄰; (3)所有信號層盡可能與地平面相鄰; (4)高頻、高速、時鐘等關鍵信號布線層要有一相鄰地平面。

原文標題:PCB多層板 : 磁通對消法有效控制EMC

文章出處:【微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

pcb

+關注

關注

4354文章

23423瀏覽量

406899 -

emc

+關注

關注

172文章

4119瀏覽量

186015

發布評論請先 登錄

PCB的EMC設計(一):層的設置與排布原則

如何才能讓PCB的EMC效果達到最優?

如何才能讓PCB的EMC效果達到最優?

評論