本文轉載自:ZYNQ微信公眾號

ILA 簡介

集成邏輯分析儀 (Integrated Logic Analyzer :ILA) 功能允許用戶在 FPGA 設備上執行系統內調試后實現的設計。當設計中需要監視信號時,應使用此功能。用戶還可以使用此功能在硬件事件和以系統速度捕獲數據時觸發。

添加 ILA

1.使用 IP 添加

添加IP

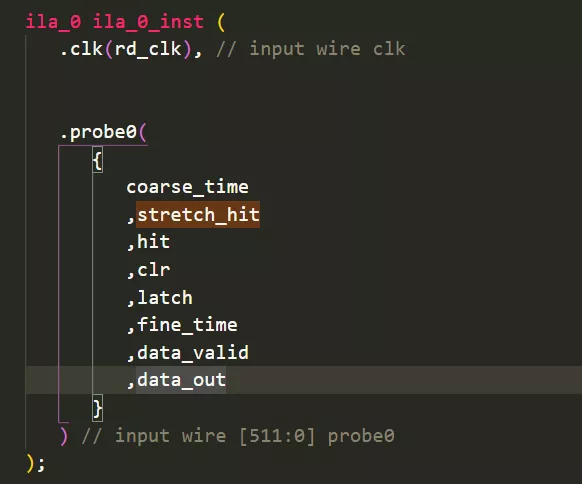

例化IP,并將所需要的信號放入 Probe 里面

2.圖形界面添加

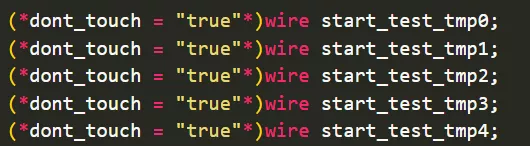

給待測試的信號加上約束,防止被優化

在綜合選項下點擊set up debug,選擇需要查看的信號即可

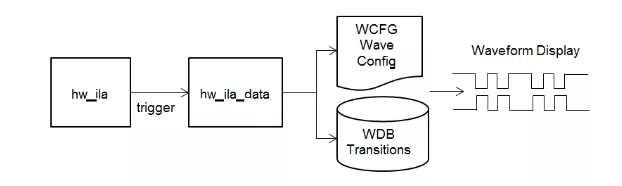

ILA 數據和波形的關系

1. hw_ila表示的是ila核

2. hw_ila_data表示保存在存儲器中的ila文件

3. WCFG是波形配置(信號顏色,總線進制表示,信號順序,marker等)

4. WDB是波形數據庫(波形數據)

ILA 失敗情景

情景1:沒有波形窗口

現象如下:

WARNING: [Labtools 27-3123] The debug hub core was not detected at User Scan Chain 1 or 3.

Resolution:

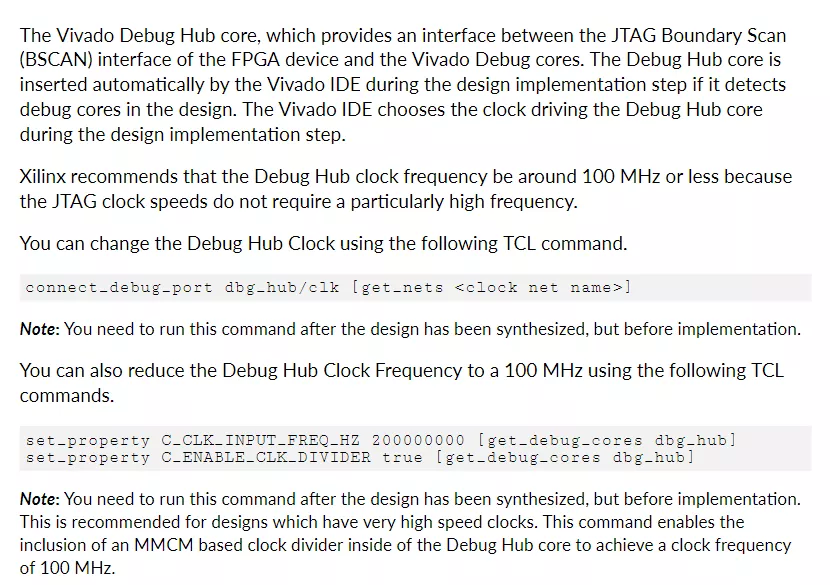

1. Make sure the clock connected to the debug hub (dbg_hub) core is a free running clock and is active OR

2. Manually launch hw_server with -e “set xsdb-user-bscan ” to detect the debug hub at User Scan Chain of 2 or 4. To determine the user scan chain setting, open the implemented design and use: get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]。

WARNING: [Labtools 27-1974] Mismatch between the design programmed into the device xc7z010_1 and the probes file E:/Xilinx/example/dma_sg_m/dma_sg_m.runs/impl_1/debug_nets.ltx.

The device design has 0 ILA core(s) and 0 VIO core(s)。 The probes file has 1 ILA core(s) and 0 VIO core(s)。

Resolution:

1. Reprogram device with the correct programming file and associated probes file OR

2. Goto device properties and associate the correct probes file with the programming file already programmed in the device.

解決方法:查看 ILA 的時鐘,如果不是自由時鐘會出現這種問題,然后重啟VIVADO軟件,重新打開

情景2:有波形窗口沒有波形

現象如下:

使用示波器查看ILA信號發現時鐘頻率發現是10M

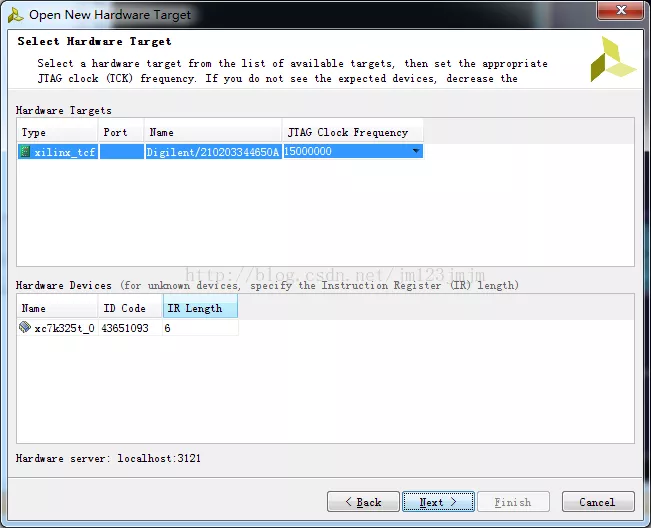

分析:查看 Xilinx 手冊發現JATG的時鐘頻率要比被ILA的時鐘頻率2.5倍低

解決方法1:修改 Hardware Target 的 JTAG 時鐘頻率

解決方法2:在TCL里面添加約束

上電后查看 ILA 信號

使用場景:flash偶爾在上電后讀出來后出錯,可以使用該方法。

一般情況下都是讓要抓的事件延遲發生或者循環發生,方便調試。

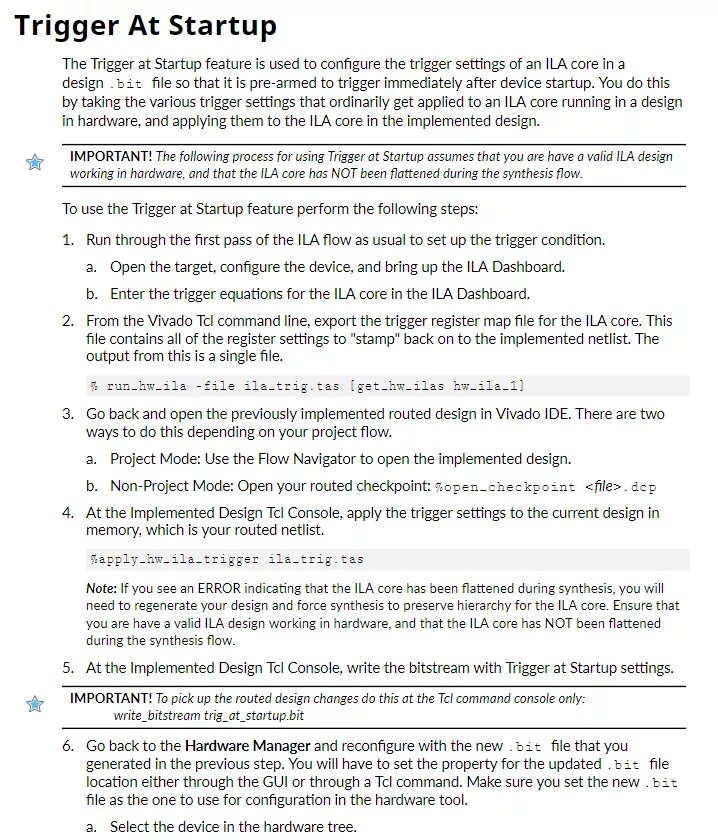

如果實在要抓啟動時的事件,按下面的步驟:(下面流程是ILA核在綜合階段不能浮空)

先把有ILA核的bit文件下進去,設置觸發好條件

運行下面的Tcl命令把觸發寄存器的值保存在tas文件中

%run_hw_ila -file ila_trig.tas [get_hw_ilas hw_ila_1]

打開實現后的implement工程

運行下面的Tcl命令把觸發設置加到當前內存里已經布線的implement設計上去

%apply_hw_ila_trigger ila_trig.tas

注意:如果發生錯誤的話說明ILA核在綜合過程中被flattened了,這時需要設置保留hierarchy重新綜合實現。

直接用Tcl命令生成bit文件,不能點擊生成bit命令,這樣工程會認為implement發生了改動而全部重新布線。

write_bitstream trig_at_startup.bit

下載bit到芯片。

參考鏈接

chrome-extension://ibllepbpahcoppkjjllbabhnigcbffpi/https://www.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug9.。.

chrome-extension://ibllepbpahcoppkjjllbabhnigcbffpi/https://www.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug9.。.

審核編輯:何安

-

Vivado

+關注

關注

19文章

828瀏覽量

68169

發布評論請先 登錄

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

一文詳解Vivado時序約束

Vivado FIR IP核實現

Vivado Design Suite用戶指南:邏輯仿真

Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明

通過spi對ADC12DL3200進行寄存器配置,當0x200的值為0x01時沒有數據,為什么?

Xilinx_Vivado_SDK的安裝教程

每次Vivado編譯的結果都一樣嗎

Vivado中關于ILA的詳解

Vivado中關于ILA的詳解

評論