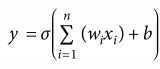

神經網絡可以被歸類為一組大致模仿人腦建模方式的算法,能夠通過引入新數據來完成“學習”過程。因此,開發專用的“計算高效型”神經網絡模型,會為機器學習帶來諸多好處。

然而,如何才能確保模型的高效性,關鍵點之一是在實現推斷加速器(廣義的硬件加速器)時應采用何種方式訪問存儲器,特別是要考慮如何將權重和中間激活值一起儲存。幾項關鍵考量包括:

時延

對 L1、L2 和 L3 存儲器的訪問表現出相對較低的時延。如果與下一個圖形運算有關的權重和激活值被緩存起來,那么我們就能保持合理水平的效率。然而,如果我們要從外部 DDR 提取數據,就會發生流水線停頓,進而影響時延和效率。

功耗

訪問外部存儲器的能耗至少比訪問內部存儲器大一個數量級。

計算飽和

一般而言,應用要么受計算限制,要么受存儲器限制。這可能會影響給定推斷范式中可實現的 GOP/TOP,而且在某些情況下,這種影響不可小視。如果被部署的具體網絡的實際性能是 1 TOP,那么使用能達到 10 TOP 峰值性能的推斷引擎價值就不大。

What's more?

更進一步,考慮到訪問現代賽靈思器件里的內部 SRAM(熟悉賽靈思 SoC 的人也稱其為 BRAM 或 UltraRAM),其能耗大約在幾微微焦耳,與訪問外部 DRAM 的能耗相比,低大約兩個數量級。

過去幾年里已有多種方法投入使用并獲得不同程度的成功,相關的架構選擇帶來的影響十分顯著。本文將以 TPUv1 架構為例,詳細闡述如何運用專門構建的神經網絡模型,進一步提升機器學習推斷的效率。

原文標題:提升效率的神經網絡模型出現了!

文章出處:【微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

存儲器

+關注

關注

38文章

7648瀏覽量

167277 -

神經網絡

+關注

關注

42文章

4814瀏覽量

103518

原文標題:提升效率的神經網絡模型出現了!

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

無刷電機小波神經網絡轉子位置檢測方法的研究

基于FPGA搭建神經網絡的步驟解析

BP神經網絡與卷積神經網絡的比較

如何優化BP神經網絡的學習率

BP神經網絡的優缺點分析

BP神經網絡與深度學習的關系

如何訓練BP神經網絡模型

深度學習入門:簡單神經網絡的構建與實現

人工神經網絡的原理和多種神經網絡架構方法

提升效率的神經網絡模型

提升效率的神經網絡模型

評論