一種增加音頻轉換器系統動態范圍的常用技術是使用相同的信號和輸出總和并行操作兩個轉換器通道。相關信號的總和使信號電平增加 6 dB,而不相關噪聲源的總和僅使噪聲電平增加 3 dB。

CS5381 的實施要求

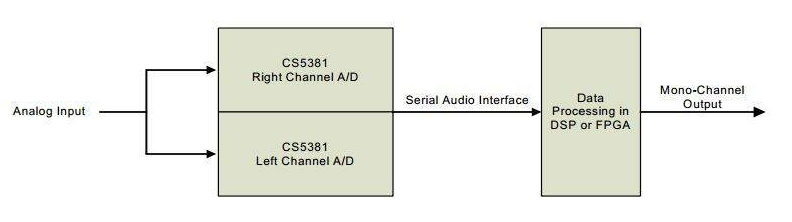

圖 1 所示的框圖顯示了 CS5381 A/D 的實現。請注意,相同的模擬信號應用于 CS5381 內的每個 A/D 轉換器。然后在數字信號處理器 (DSP) 或現場可編程門陣列 (FGPA) 中執行所需的數學運算。

需要注意的是,加法(或減法)必須使用同步采樣和時間對齊的數據對來執行。在串行音頻接口內,左后右聲道數據對是同步采樣數據。然而,右聲道數據對與左聲道數據對相對于彼此在時間上偏移一個采樣周期,并且這些對的相加或相減將產生錯誤的結果。

單模框圖

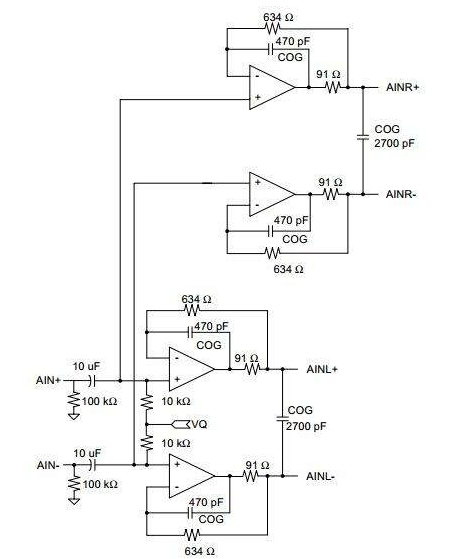

CS5381 在單聲道模式下的推薦模擬輸入緩沖器 CS5381的實現需要單獨的輸入緩沖器級用于差分模擬輸入。已證明驅動兩個差分輸入的單個緩沖器會導致不可接受的失真水平。推薦的緩沖器拓撲與 CS5381 評估板 CDB5381 上顯示的幾乎相同。圖 2 中的示意圖是方程 eo = A/2 + B/2 的建議緩沖區實現。

CS5381 推薦的同相配置緩沖器實現

演示技術

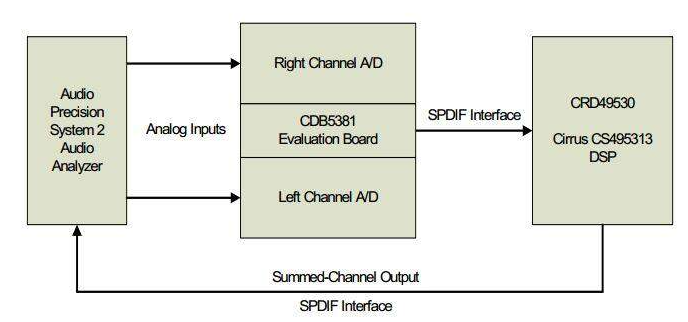

使用標準 Cirrus Logic 評估板和 Audio Precision System 2 組裝測試系統來演示該技術是一件相對簡單的事情。圖 3 中的框圖顯示了一個測試設置,其中包括 CDB5381 和 CRD43530,評估CS5381 A/D 和 CS495313 音頻 DSP 板。Audio Precision System 2 是模擬信號的來源,也是用于生成性能數據和繪圖的分析工具。評估板和 Audio Precision System 2 之間的數字互連是標準的 S/PDIF (IEC-60958) 接口。評估是在 48 kHz 采樣率下進行的,但性能改進在所有采樣率下都有效。

測試系統框圖

編輯:hfy

-

FGPA

+關注

關注

1文章

26瀏覽量

16261 -

數字信號處理器

+關注

關注

5文章

482瀏覽量

27872 -

音頻轉換器

+關注

關注

0文章

24瀏覽量

45437

發布評論請先 登錄

EEPROM芯片內部的1路14bit ADC, ADC精度受使用通道數和采樣率是怎么樣的?

AN-1279: 如何過采樣5 MSPS、18/16位精密SAR轉換器以便增加動態范圍

ADC344X的外部同步輸入SYSREF范圍是-0.3~(AVDD + 0.3 = 2.1)V,是否可以通過FPGA輸出1.8V信號來直接驅動?

如何通過TLA2528獲取8個通道的adc值?

PCM1808的通道溢出、動態范圍窄是什么原因導致的?怎么解決?

adc0809輸入電壓范圍 adc0809和adc0808區別

什么是無雜散動態范圍 (SFDR)?為什么 SFDR 很重要?

使用TLV320ADC5140/6140和PCM5140-Q1/PCM6140-Q1中的動態范圍增強器

ADS2806高動態范圍、12位流水線式模數轉換器(ADC)數據表

ADS5232高動態范圍、12位流水線式模數轉換器(ADC)數據表

ADS5231高動態范圍、12位流水線式模數轉換器(ADC)數據表

ADS850高動態范圍、14位模數轉換器(ADC)數據表

如何通過通道總和增加 ADC 動態范圍

如何通過通道總和增加 ADC 動態范圍

評論