最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

流程:

1. 異步復位:

優點:⑴大多數 DFF 都有異步復位端口,因此采用異步復位可以節約資源。

⑵設計相對簡單。

⑶異步復位信號識別方便,而且可以很方便地使用 fpga 的全局復位端口。

缺點:⑴在復位信號釋放時容易出現問題,亞穩態。

⑵復位信號容易受到毛刺的影響。這是由于時鐘抖動或按鍵觸發時的硬件原因造成的。

代碼:一個 4bit 的計數器。

1 always @(posedge clk or negedge sys_rst_n) begin

2 if (~sys_rst_n) begin

3 count <= 0;

4 end //if

5 else begin

6 count <= count + 1'b1; ? ?

7 end //else

8 end //always

復位信號低電平時候,系統立刻進入復位態;

2. 同步復位:

優點:⑴降低亞穩態出現的概率。

⑵使所設計的系統成為 100%的同步時序電路,有利于時序分析,綜合出來的 Fmax 一般較高。

⑶只有在時鐘有效沿才有效,可以濾除高于時鐘頻率的毛刺。

缺點:⑴復位信號的有效時長必須大于時鐘周期,才能真正被系統識別并完成復位任務。

⑵大多數的 Dff 只有異步復位端口,會浪費較多的邏輯資源。

代碼:

1 always @(posedge clk) begin

2 if (~sys_rst_n) begin

3 count <= 0;

4 end //if

5 else begin

6 count <= count + 1'b1; ? ?

7 end //else

8 end //always

時鐘上升沿如果復位信號為低電平,復位開始,時鐘上升沿若復位信號為高電平,復位結束。

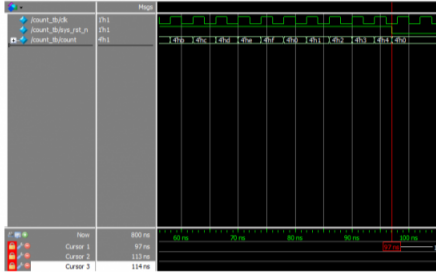

3. 異步復位同步釋放:(推薦使用)

優點:結合了同步復位與異步復位的優點。

缺點:容易受到噪聲與宰脈沖的干擾。如果可能,最好對輸入到 fpga 的異步復位信號先進行濾波與去抖動。

代碼:

1 module rstn_as (

2 //input;

3 input wire clk,

4 input wire sys_rst_n,

5 //output;

6 output reg rst_n

7 );

8 reg rst_n_reg;

9 always @(posedge clk or negedge sys_rst_n) begin

10 if (~sys_rst_n) begin

11 rst_n <= 1'b0;

12 rst_n_reg <= 1'b0;

13 end //if

14 else begin

15 rst_n_reg <= 1'b1;

16 rst_n <= rst_n_reg; ? ?

17 end //else

18 end //always

19

20 endmodule

wire rst_n;

rstn_as u1(

.clk (clk),

.sys_rst_n (sys_rst_n),

.rst_n (rst_n)

);

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

count <= 0;

end //if

else begin

count <= count + 1'b1; ? ?

end //else

end //always

當復位信號低電平時,系統立即復位;當時鐘上升沿檢測到復位信號失效后,在下一個時鐘上升沿拉高 rst_n。新的 rst_n 是已經同步化了的復位信號。

以上。

審核編輯 黃昊宇

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613881

發布評論請先 登錄

電路仿真軟件哪個更實用

基于Altium Designer的電路仿真

基于FPGA的SoC驗證平臺實現電路仿真偵錯

FPGA設計實戰-復位電路仿真設計

FPGA設計實戰-復位電路仿真設計

評論