按照仿真對象劃分,電路仿真工具通常分為三大類:晶體管級的模擬電路仿真工具、門級和RTL級的數(shù)字電路仿真工具、模數(shù)混合電路仿真工具。

1.模擬電路仿真工具

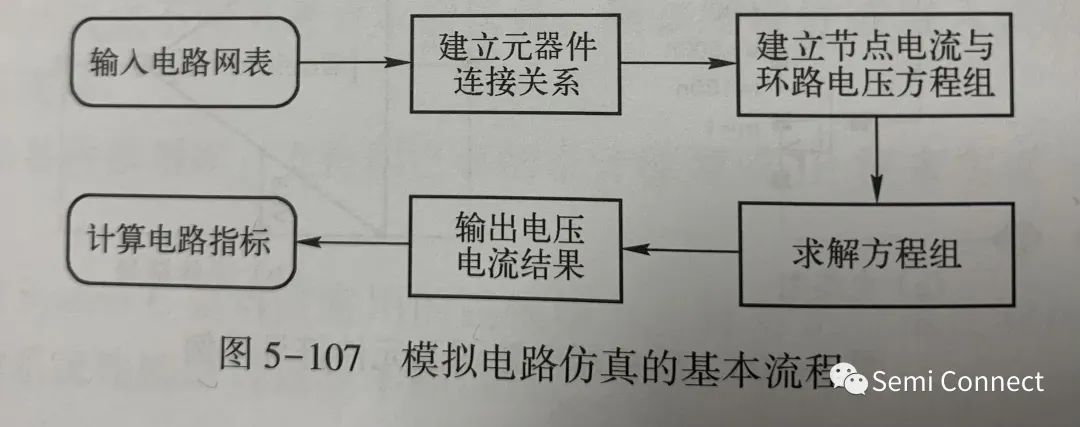

模擬電路仿真的基本流程如圖5-107所示。

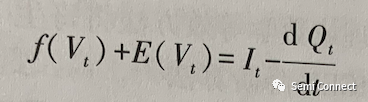

模擬電路的方程為

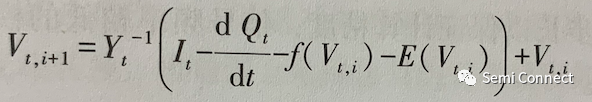

式中,t為時間;Vt為節(jié)點電壓;It為節(jié)點獨立電流源;Qt為節(jié)點電荷;f(Vt)為節(jié)點非線性電流;E(Vt)為節(jié)點受控電流。采用Newton-Raphson迭代法可以求解該方程組,得到解的迭代形式(i=1,2,3,......,為迭代次數(shù)):

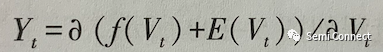

式中,Yt為f(Vt)+E(Vt)的雅克比矩陣,即

Yt通常是一個稀疏矩陣,可以采用LU分解算法降低其計算復(fù)雜度。在LU分解之前對Yt的行列進行預(yù)排列,可以減少計算量并提高迭代計算的穩(wěn)定性。結(jié)構(gòu)較為特殊的電路其Yt矩陣為稠密矩陣,用PCG、GMRES等算法可以獲得更快的求解速度。電荷Qt對時間t的微分計算有Forward Euler法、Backward Euler法等單步算法與TRAP、GEAR等多步算法,其精度與穩(wěn)定性受電路類型影響。

求解方程組的計算量隨著電路節(jié)點的增加而急劇增加,因此商業(yè)模擬電路仿真工具中通常會加入多種加速技術(shù)以提高性能。

(1)并行計算:將電流與雅克比矩陣的計算分配到多個CPU上同時進行。

(2)旁路(Bypass)技術(shù):當(dāng)節(jié)點電壓變化不大時無須重新計算非線性電流與雅克比矩陣,僅對電流做線性修正。

(3)節(jié)點合并(Node Folding)技術(shù):采用線性修正的算法消除非線性器件的內(nèi)部節(jié)點,減少方程數(shù)。

對于更大規(guī)模的電路,仿真工具還會引入一些降低精度但可以極大提高仿真速度與容量的技術(shù),即快速仿真技術(shù)。這些技術(shù)主要有如下幾種。

(1)查表模型(Table Model):采用查表插值的辦法計算非線性器件的電流電荷。

(2)事件驅(qū)動(Event Driven):將電路劃分為若干模塊獨立求解,僅在端口節(jié)點的電壓變化時才重新計算相鄰模塊。

(3)同態(tài)技術(shù)(Isomorphism):結(jié)構(gòu)相同、電壓相近的多個模塊共享雅克比矩陣,只求解一次方程組,不同模塊之間微小的差異依靠線性插值修正。

此外,寄生效應(yīng)會影響集成電路的性能甚至功能,而考慮了寄生效應(yīng)的模擬電路仿真則稱為模擬電路后仿真。在后仿真中,寄生器件導(dǎo)致矩陣規(guī)模急劇增大,耦合效應(yīng)導(dǎo)致矩陣填充更為稠密,為此需要引入加速技術(shù)在精度影響很小的前提下提高仿真速度與容量,常用的技術(shù)如下。

(1)RC約減:通過物理或數(shù)學(xué)等效方法將寄生RC網(wǎng)絡(luò)簡化為規(guī)模較小的等效電路,其常用算法為TICER降價算法。

(2)電路劃分:將電路分割為多個耦合較少的模塊分別計算,結(jié)果回代到頂層矩陣得到電路的解。常用方法有超圖劃分、BBD和SuperLU等。

(3)多重速率:根據(jù)工作頻率將電路劃分成多個模塊,信號頻率較高的模塊設(shè)置較小的時間步長以保證計算精度,信號頻率較低的模塊設(shè)置較大時間步長以提升計算速度。

2.數(shù)字電路仿真工具

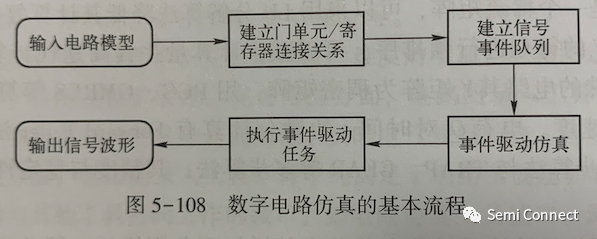

數(shù)字電路仿真的基本流程如圖5-108所示。

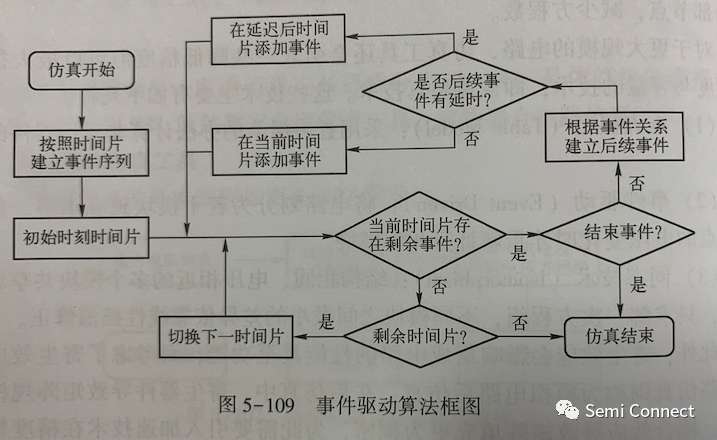

數(shù)字電路一般采用VHDL、Verilog HDL或者System Verilog等語言來描述。這些語言支持對邏輯信號的時序關(guān)系進行量化及檢測。數(shù)字電路仿真采用事件驅(qū)動算法進行信號邏輯仿真,即邏輯單元的輸入/輸出信號為有限數(shù)量的邏輯態(tài),其輸出僅在輸入信號狀態(tài)發(fā)生變化的情況下重新計算。事件驅(qū)動算法框圖如圖5-109所示。

在數(shù)字電路仿真中可以附加SDF(Standard Delay Format)文件進行后仿真以得到更準確的時序結(jié)果。該文件通過提取電路版圖獲得元器件與連線精確延時而產(chǎn)生。數(shù)字電路仿真的速度遠高于模擬電路仿真,但精度遠低于模擬電路仿真。

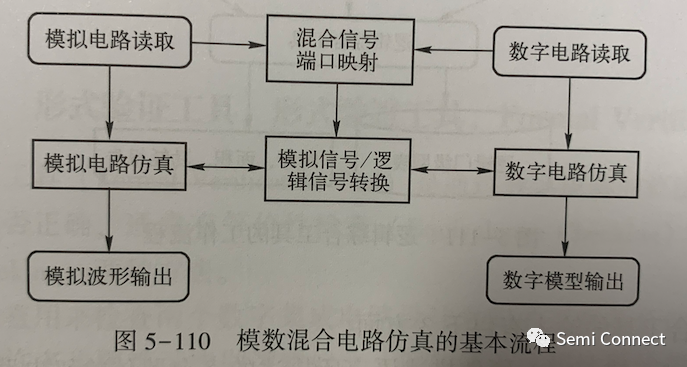

3.模數(shù)混合電路仿真工具

模數(shù)混合電路仿真結(jié)合模擬與數(shù)字信號電路仿真工具,對不同模塊分別采用晶體管級或門級/RTL級電路進行仿真。模數(shù)混合電路仿真的核心是識別模擬信號與數(shù)字信號相連的節(jié)點,并通過信號轉(zhuǎn)換算法將其中連續(xù)的模擬信號與離散的數(shù)字信號互相轉(zhuǎn)換。模數(shù)混合電路仿真的基本流程如圖5-110所示。

審核編輯:劉清

-

模擬電路

+關(guān)注

關(guān)注

125文章

1588瀏覽量

103619 -

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43145 -

晶體管

+關(guān)注

關(guān)注

77文章

9970瀏覽量

140522 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60607

原文標題:可編程邏輯電路設(shè)計—仿真工具

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Multisim模擬電路仿真教程

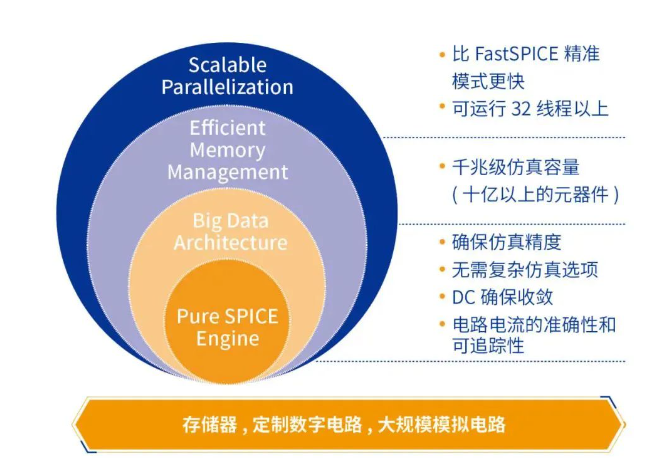

概倫電子千兆級高精度電路仿真器NanoSpice Giga介紹

Qorvo電路仿真工具QSPICE:賦能工程師重塑電路設(shè)計、簡化業(yè)務(wù)流程和重新定義客戶互動

東芝在線電路仿真器的核心優(yōu)勢

數(shù)模混合電路仿真實現(xiàn)

Verilog 電路仿真常見問題 Verilog 在芯片設(shè)計中的應(yīng)用

網(wǎng)絡(luò)線纜有哪幾大類

法動科技系統(tǒng)級電路仿真設(shè)計平臺FDSPICE介紹

hspice共源放大電路仿真分析

連接器通常可以分為以下幾大類

電路仿真和PCB設(shè)計軟件

電路仿真工具通常分為幾大類

電路仿真工具通常分為幾大類

評論