來(lái)源:電源網(wǎng)編譯

總部位于諾丁漢的無(wú)晶圓廠芯片初創(chuàng)企業(yè)“Search For The Next”(SFN)聲稱,只有8個(gè)光刻掩模可以制造出低功耗的自定義邏輯芯片,而CMOS需要20多個(gè)掩模。

公司首席執(zhí)行官David Summerland表示,這樣就減少了生產(chǎn)前置時(shí)間——到2020年12月的目標(biāo)是兩周。

他還表示,僅使用這八層,就可以包括電源和模擬元件。

整個(gè)方案的關(guān)鍵是Bizen,它是一種新穎的晶體管-本質(zhì)上是一種pnp器件,其基極通過(guò)量子隧道結(jié)驅(qū)動(dòng),并且包括第二個(gè)隧道結(jié)以內(nèi)部自偏置晶體管-稍后將進(jìn)一步介紹該技術(shù)。 Summerland說(shuō),這是從硅開(kāi)始的,但是能夠遷移到氮化鎵和其他化合物半導(dǎo)體。

Silicon Bizen不僅是一項(xiàng)理論研究:Search For The Next與已建立的基于Glenrothes的芯片制造商Semefab合作,該公司已經(jīng)在運(yùn)行Bitzen晶片。

兩家公司共同致力于在明年第二季度向潛在客戶提供技術(shù)演示器樣品芯片。

根據(jù)Summerland的說(shuō)法,要?jiǎng)?chuàng)建VHDL,將有一個(gè)免費(fèi)的Cadence流程設(shè)計(jì)套件(PDK)和標(biāo)準(zhǔn)庫(kù),使Bizen“比CMOS的生產(chǎn)速度快80-90%”。

Bizen晶體管

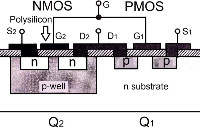

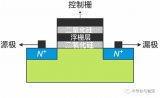

SFN的晶體管具有類似pnp的結(jié)構(gòu),但基極有所不同。

Summerland說(shuō):“這是一種雙極機(jī)制,而不是像MOSFET那樣的單極機(jī)制。”“您不會(huì)像BJT那樣直接與基座接觸,它也不會(huì)像MOSFET那樣被氧化物隔離。取而代之的是到基阱的隧道結(jié),其中摻雜很重且交界突然。結(jié)果就是Bizen-雙極穩(wěn)壓管-保留了傳統(tǒng)雙極處理的優(yōu)點(diǎn),但通過(guò)使用齊納量子隧道力學(xué)消除了缺點(diǎn)。

根據(jù)SNF的說(shuō)法,雖然可以將名稱“收集器”和“發(fā)射極”用于兩個(gè)非隧道(“基極”)電極,但該設(shè)備是對(duì)稱的-可以在不更改功能的情況下交換這兩個(gè)端子,因此它具有選擇將它們命名為“陽(yáng)極1”和“陽(yáng)極2”。

第二個(gè)隧道結(jié)使設(shè)備偏置,以便在隧道端子開(kāi)路時(shí)“接通”(但不飽和)。 根據(jù)Summerland的說(shuō)法,雖然這表示在操作過(guò)程中有連續(xù)的電流流到地面,但隧道電流通常僅為2-5nA,他補(bǔ)充說(shuō),可以通過(guò)包括一個(gè)可以斷開(kāi)偏置隧道連接的單一結(jié)構(gòu)來(lái)引入低功耗“睡眠”模式。負(fù)軌上有許多(也許是一千個(gè))雙結(jié)晶體管的結(jié)。”

Bizen三項(xiàng)輸入NOR門(mén)-這是電流而非電壓邏輯。將任何輸入連接到正軌以停止陽(yáng)極之間的導(dǎo)通。

在這種開(kāi)路條件下,隧道電極將以200-300mV的電壓浮在最正的陽(yáng)極下方,并且該器件可以在其陽(yáng)極之間通過(guò)20-30nA的電流,在這些陽(yáng)極之間的壓降可低至幾毫伏。

這使一個(gè)Bizen晶體管能夠?qū)㈦S后的Bizen晶體管的大致10個(gè)隧道結(jié)上拉至正軌的毫伏以內(nèi)-要使用TTL說(shuō)法,它的扇出度約為0。

當(dāng)設(shè)備的隧道連接被拉到正極時(shí),其兩個(gè)陽(yáng)極之間的電流路徑將關(guān)閉,隨后設(shè)備的隧道端子不會(huì)被驅(qū)動(dòng)-它們會(huì)懸空。

因此,使用Bizen晶體管構(gòu)建的任何邏輯都是基于電流的邏輯,而不是基于電壓的邏輯,并且不需要占用空間的電阻器或偏置隧道結(jié)以外的額外電流吸收器。

根據(jù)Summerland的說(shuō)法,可以使用Bizen晶體管實(shí)現(xiàn)任何任意邏輯功能,并且只需要四個(gè)工藝光刻掩模(而不是整個(gè)工藝的八個(gè)掩模)即可實(shí)現(xiàn)僅邏輯芯片,因?yàn)榭梢栽诰w管內(nèi)部建立晶體管到晶體管的連接。四層–無(wú)需金屬層。如上所述,正在準(zhǔn)備設(shè)計(jì)工具。“如果我們使用ARM或x86 [處理器],我們將使用幾個(gè)金屬層進(jìn)行路由,”Summerland說(shuō)。

上邊(黃色)是Bizen D型主從觸發(fā)器,在該1μm工藝示例中,僅需八個(gè)晶體管,并占45 x37μm。不需要金屬層。在相同尺寸的工藝上,根據(jù)Summerland的CMOS版本(左,綠色),將需要28-35個(gè)晶體管,并占用112 x37μm(金屬觸點(diǎn)為2.5μm,89 x30μm金屬觸點(diǎn)窗口為縮小(1.3μm)為1μm。 這是一個(gè)相對(duì)粗糙的過(guò)程:“從理論上講,我們可以擴(kuò)展Bizen過(guò)程,目前正在研究證明這一點(diǎn),”他補(bǔ)充說(shuō)。

那耗電量呢?那些靜止的鈉會(huì)增加。

是的,同意Summerland,但是Bizen的動(dòng)態(tài)功率要小得多,因?yàn)樗鼪](méi)有與cmos相關(guān)的所有浪費(fèi)功率的MOSFET柵電容。

功率晶體管

據(jù)SFN稱,八層工藝還可以容納高達(dá)650V的NPN功率晶體管和這些晶體管的基極驅(qū)動(dòng)器。

根據(jù)Semefab首席執(zhí)行官艾倫·詹姆斯(Allen James)的說(shuō)法,Bizen實(shí)際上是出于為雙極芯片加香料的需要而發(fā)展的:

Semefab與SFN合作,探索在降低智能電源IC工藝復(fù)雜性的同時(shí)保持對(duì)芯片進(jìn)行編程的能力的方法。早期建議被拒絕,因?yàn)樗鼈儾荒軡M足所需的低口罩?jǐn)?shù)量目標(biāo)。最終,SFN提出了使用微型反向偏置的齊納二極管結(jié)構(gòu)的量子隧道效應(yīng)的想法。結(jié)果表明,經(jīng)過(guò)仔細(xì)建模,可以將常規(guī)橫向和縱向雙極結(jié)構(gòu)的集成設(shè)計(jì)為結(jié)合Bizen,而不會(huì)造成額外的過(guò)程復(fù)雜性。最初我很懷疑,但是我接受了這個(gè)概念并看到了早期的結(jié)果,它的確打動(dòng)了許多顛覆行業(yè)的盒子。盡管CMOS容易發(fā)生閂鎖和ESD,但這并不是一個(gè)問(wèn)題,而是CMOS有缺陷。CMOS低功耗,已經(jīng)通過(guò)了時(shí)間的考驗(yàn)并且通常可靠。但是,它很復(fù)雜,并且與電源集成時(shí)更是如此。復(fù)雜性意味著更長(zhǎng)的交貨時(shí)間和更高的成本。

但是雙極功率晶體管不是有損耗的嗎?

不,Summerland認(rèn)為,功率MOSFET只不過(guò)是它們,而且它們也不必變慢。MOSFET跨導(dǎo)基于漏極電流的平方根。他說(shuō),BJT跨導(dǎo)與集電極電流成正比,而跨導(dǎo)與速度有關(guān),除非MOSFET的寬度比長(zhǎng)度長(zhǎng)得多。我們相信,Bizen電源IC的開(kāi)關(guān)速度將與IGBT的MOSFET一樣快。”

工藝設(shè)計(jì)套件(PDK)包括1A和10A功率晶體管。

模擬計(jì)算

SFN的最后一招是Bizen模擬模塊–運(yùn)算放大器和比較器(在PDK中),甚至是模擬計(jì)算模塊,例如分頻器-模擬計(jì)算模塊在某些情況下避免使用邏輯-從而避免使用相關(guān)的ADC和DAC應(yīng)用程序。如果采用邏輯,Summerland采用粗細(xì)結(jié)構(gòu),可以預(yù)測(cè)1μW1μs的模擬除法,而不是大約20條指令和大約100條指令周期。這種模擬處理功能被稱為“即時(shí)處理單元” IPU。

溫度范圍

SFN預(yù)測(cè)使用Bizen晶體管的芯片以及與Semefab合作開(kāi)發(fā)的相關(guān)工藝將在-40至+ 85°C的溫度范圍內(nèi)運(yùn)行,盡管詳細(xì)數(shù)據(jù)需要運(yùn)行更多的晶圓。Summerland說(shuō):“我們處于'技術(shù)準(zhǔn)備水平'5級(jí)”。

隧穿電流受溫度影響,但該公司將平衡工藝參數(shù)和預(yù)期的工作電壓(范圍為5V至3V,并且在不同的摻雜下可能更低),以達(dá)到雪崩和齊納特性交叉以最小化溫度的目的系數(shù)。

Semefab的James告訴《電子周刊》:“溫度系數(shù)將與二極管的暗電流泄漏相距100萬(wàn)英里,二極管每7°C就會(huì)增加一倍。”這促使Summerland補(bǔ)充說(shuō):“這要小幾個(gè)數(shù)量級(jí),這就是為什么 我們選擇隧道電流而不是漏電流。”

關(guān)于準(zhǔn)備情況,詹姆斯說(shuō),他的公司現(xiàn)在正在驗(yàn)證PDK,并預(yù)測(cè)明年第二季度的Bizen邏輯,“運(yùn)放和比較器的集成可能會(huì)收斂到相同的時(shí)間范圍。我們已經(jīng)完成了垂直功率晶體管,盡管我們還沒(méi)有達(dá)到650V。”

他強(qiáng)調(diào)說(shuō),他的公司能夠?qū)izen芯片設(shè)計(jì)轉(zhuǎn)變?yōu)楣璧乃俣扔卸嗫臁!霸撨^(guò)程不是火箭科學(xué):它使用標(biāo)準(zhǔn)擴(kuò)散和標(biāo)準(zhǔn)晶圓廠模塊。沒(méi)有什么深?yuàn)W的。在特征尺寸為1μm的情況下,我們甚至不必考慮晶圓平面化-該技術(shù)對(duì)輪廓感到滿意。我們可以在兩到三個(gè)星期內(nèi)完成運(yùn)行。”

詹姆斯補(bǔ)充說(shuō):“在Bizen成為商業(yè)現(xiàn)實(shí)之前,還有一段路要走,我們?nèi)栽趯W(xué)習(xí),但是Semefab和SFN一直在努力工作。”

技術(shù)示范

明年第二季度,將向潛在采用該工藝的技術(shù)人員提供技術(shù)演示。

SFN對(duì)此沒(méi)有多說(shuō),只是說(shuō)它將結(jié)合Bizen邏輯,模擬IPU和電源。

Summerland告訴《電子周刊》,它可能有一個(gè)800 x800μm的管芯,中間有一個(gè)300 x300μmIPU,被包括垂直電源npn在內(nèi)的功能所包圍。

他說(shuō),它可能采用類似于TO-92塑料外殼的材料,甚至可能只有三個(gè)連接,堅(jiān)決拒絕透露其預(yù)期功能。

本文來(lái)源electronicsweekly,電源網(wǎng)編譯。

審核編輯 黃昊宇

-

集成電路

+關(guān)注

關(guān)注

5417文章

11942瀏覽量

366990 -

IC

+關(guān)注

關(guān)注

36文章

6093瀏覽量

178315 -

晶體管

+關(guān)注

關(guān)注

77文章

9977瀏覽量

140604

發(fā)布評(píng)論請(qǐng)先 登錄

LM395系列 42V 功率晶體管數(shù)據(jù)手冊(cè)

浮思特 | CMOS技術(shù)原理與應(yīng)用:從晶體管結(jié)構(gòu)到反相器設(shè)計(jì)

多值電場(chǎng)型電壓選擇晶體管結(jié)構(gòu)

晶體管電路設(shè)計(jì)(下)

晶體管電路設(shè)計(jì)(下) [日 鈴木雅臣]

集成電路制造工藝中的偽柵去除技術(shù)介紹

集成電路的引腳識(shí)別及故障檢測(cè)

探索集成電路的奧秘

短溝道二維晶體管中的摻雜誘導(dǎo)輔助隧穿效應(yīng)

隧穿晶體管的原理及優(yōu)勢(shì)

浮柵晶體管的組成結(jié)構(gòu)以及原理

單片集成電路和混合集成電路的區(qū)別

芯片晶體管的深度和寬度有關(guān)系嗎

晶體管功率繼電器的基本介紹

高壓功率IC片上靜電防護(hù)器件

隧穿晶體管在同一塊易于制造的集成電路(IC)上提供邏輯與功率

隧穿晶體管在同一塊易于制造的集成電路(IC)上提供邏輯與功率

評(píng)論