EMI指的是電子系統對外界所產生電磁輻射或干擾的強度。

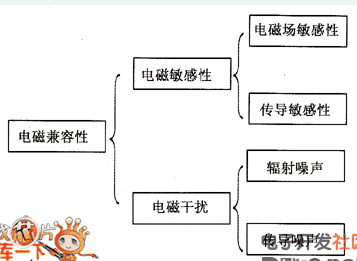

EMC指的是對電子產品在電磁場方面干擾大小(EMI)和抗干擾能力(EMS)。

電磁干擾、噪聲產生和信號傳輸不良是造成電子線路故障的主要原因。據估計,由原型PCB電路的電磁干擾(EMI)引起的故障率高達50%。較差的電路設計是導致不必要電磁輻射或易感性的最終原因。5G的到來將進一步推動未來幾年對無EMI PCB的需求。

下面我們探討PCB設計中如何避免MEI的產生和MEC兼容性問題:

一、 電源線布局

1、根據電源電流大小,計算出布線寬度,并盡可能加寬。

2、電源線和地線的方向應與數據傳輸方向一致。

3、在電源的輸入端加上解耦電容,一般設置為10~100uF。

二、地線布局

1、數字地和模擬地進行分離

數字地和模擬地最終要連接在一起,有四種方法解決此問題:① 用磁珠連接;②用電容連接;③用電感連接;④用0歐姆電阻連接。

磁珠,等效電路相當于帶阻限波器,只對某個頻點的噪聲有抑制作用,使用時需要預先估計噪聲頻率,以便選用適當型號。對于頻率不確定或無法預知的情況,用磁珠連接不合理。

電容,隔直通交,造成浮地,沒效果。

電感,體積較大,雜散參數多,不穩(wěn)定。

0歐電阻,相當于很窄的電流通路,能夠有效地限制環(huán)路電流,使噪聲得到抑制。電阻在所有頻帶上都有衰減作用(0歐電阻也有阻抗),這點比磁珠強。

2、接地線盡量加寬或加厚,使其能通過計算出電流的3倍,一般我2~3mm。

3、地線應盡量形成死循環(huán)回路,減小地線壓差。

三、解耦電容

1、為每個IC的VCC和GND都并聯一個0.01uF~0.1uF陶瓷電容。

2、抗噪聲能力弱、關斷電流變化大的器件,及ROM和RAM,在VCC和GND間并聯電容,進行解耦。

3、單片機的Reset引腳加0.01uF解耦電容。

4、解耦電容的走線不能太長,特別是高頻旁路電容的走線。

5、電源的輸入端加上解耦電容,一般設置為10~100uF。

電源與集成電路之間的解耦電容有兩方面作用:①集成電路儲能電容;②繞過器件的高頻噪聲。

一般情況下,解耦電容的大小為C=1/F,F為數據傳輸頻率,0.1uF對應10Mhz,0.01對應100Mhz。典型的解耦電容是0.1uF,其分布電感典型值是5uH,并聯共振頻率是7Mhz。也就是說對10Mhz一下的噪聲有良好解耦效果,對于40Mhz以上的噪聲幾乎沒有什么作用。解耦電容的管教盡量短,長引腳會引起解耦電容自諧振。例如:當1nF陶瓷貼片電容引腳長6.3mm時,其自諧振頻率是35Mhz,當引腳長度我12.6mm時,自諧振頻率約為32Mhz。

四、器件布置

2、大電流走線和信號走線盡量遠離邏輯電路器件;

3、pcb電路板在機箱中運行時,發(fā)熱器件盡量放在機箱的頂部。

五、PCB抗干擾設計

1、IO驅動線采用串聯電阻法,降低控制電路電位上下跳變速度,減少信號反射;

2、時鐘線的周圍用地線包裹,以及時鐘線盡量的短;

3、I/O驅動電路盡可能的靠近PCB板的邊緣,對進入PCB板的信號進行濾波,對來自高噪聲區(qū)的信號進行濾波;

4、對未使用的門電路輸出端不應掛起。未使用的運放電路的正輸入接地,負輸入接在輸出端上;

5、盡量使用45度折線代替90度折線,減少高頻信號的外部傳輸和耦合;

6、采用垂直布線,垂直于I/O線的時鐘線小于平行于IO線的時鐘干擾;

7、元器件的引腳引線盡可能的短,降低耦合或干擾;

8、不要在石英晶振或易受干擾的器件下面布線;

9、不要在弱信號或低頻信號的周圍形成電流回路。

六、其它

1、總線加上10K上拉或下拉電阻,抗干擾比較好;

2、每個地址線的線長盡可能的短,抗干擾比較好;

3、對于2層PCB板,兩側的布線盡量垂直;

4、未使用的引腳通過上拉電阻(約10K)連接到GND或VCC引腳上;

5、發(fā)熱的元件盡量離開IC、晶振、電解電容等容易受到影響的器件;

6、抑制大功率器件對單片機等數字器件的干擾及數字電路對模擬電路的干擾,用高頻扼流線圈連接模擬地和數字地。

7、電源線、交流線、信號線要做到分離開。電源線和交流線盡量另布一個PCB板。

8、一個過孔引起大約0.6pF的電容,一個集成電路的封裝材料引起2-10pF的分布電容,一個接插件引起約有520uF的分布電感,一個雙列直插24引腳的集成電路插座引起4-18uF的分布電感。

編輯:hfy

-

pcb

+關注

關注

4354文章

23422瀏覽量

406894 -

晶振

+關注

關注

35文章

3202瀏覽量

69607 -

電磁干擾

+關注

關注

36文章

2379瀏覽量

106312

發(fā)布評論請先 登錄

PCB設計與電磁兼容

PCB設計中的EMC、EMI電磁兼容性考慮!

PCB中電磁兼容性設計

提升電路板電磁兼容性的方法

PCB設計之如何設計電磁兼容性?

印刷電路板(PCB)開發(fā)技術中的電磁的兼容性

單片機PCB設計對電磁兼容性的處理

淺談pcb設計中MEI產生和MEC兼容性

淺談pcb設計中MEI產生和MEC兼容性

評論