兩種晶體管一起造——英特爾正在研究的晶體管堆疊技術將大幅度提高芯片的計算密度。 目前我們所熟知的臺積電、三星、英特爾、格芯、中芯國際等芯片代工廠量產的先進工藝普遍采用基于多柵鰭型場效應晶體管(FinFET)結構。在 5 納米及以下的制程時,更先進的技術節點面臨的發熱和漏電將變得難以控制,人們必須尋找全新的工藝,堆疊晶體管設計正在成為重要方向。

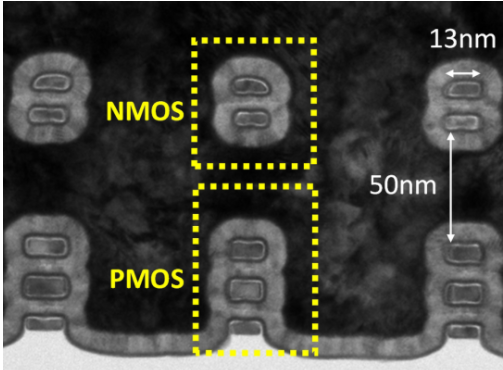

NMOS 和 PMOS 組件通常是并列出現在芯片上的。英特爾現在已經找到了讓它們彼此堆疊的方法,這可以大幅度降低電路尺寸。 當今幾乎所有電子設備的算力本質都是兩種晶體管的組合——NMOS 和 PMOS。當電壓信號輸入時,其中一個打開則另一個會被關閉,兩者放在一起時,只有 bit 變化才有電流,這種設計顯著降低了能耗。這種晶體管組合自 1959 年以來幾乎沒有變化,但隨著芯片制造制程的不斷提升,電路正在不斷被縮小,它們之間的距離也在不斷靠近。 在本周 IEEE 國際電子設備會議(IEDM)上,英特爾展示了一種全新的方式:將 NMOS 和 PMOS 對堆疊起來,該方案有效地將簡單 CMOS 電路的占位面積減少了一半,這意味著未來 IC 的晶體管密度可能直接翻倍。

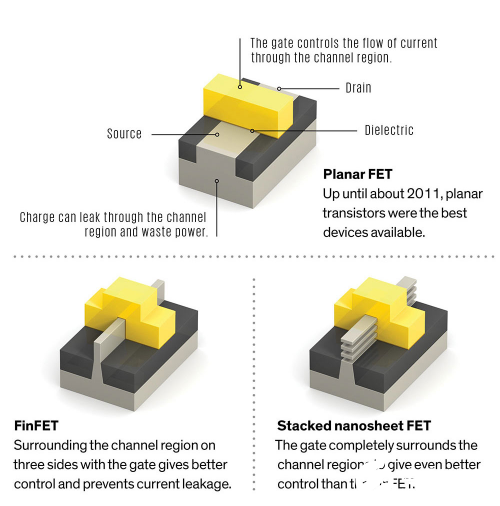

這種設計被廣泛認為會首先被應用于下一代制程晶體管即 nanosheet、nanoribbon(納米薄片)、nanowire(圓柱體納米線),或被稱為全環繞柵極晶體管(Gate-All-Around FET)的方法上,這可能是常規架構計算機通向摩爾定律的最后一步。nanosheet 的溝道區域不會是像目前 FinFET 等方式,由垂直硅鰭片構成晶體管主要部分,而是由多層、水平、幾納米厚的片層堆疊在一起構成。

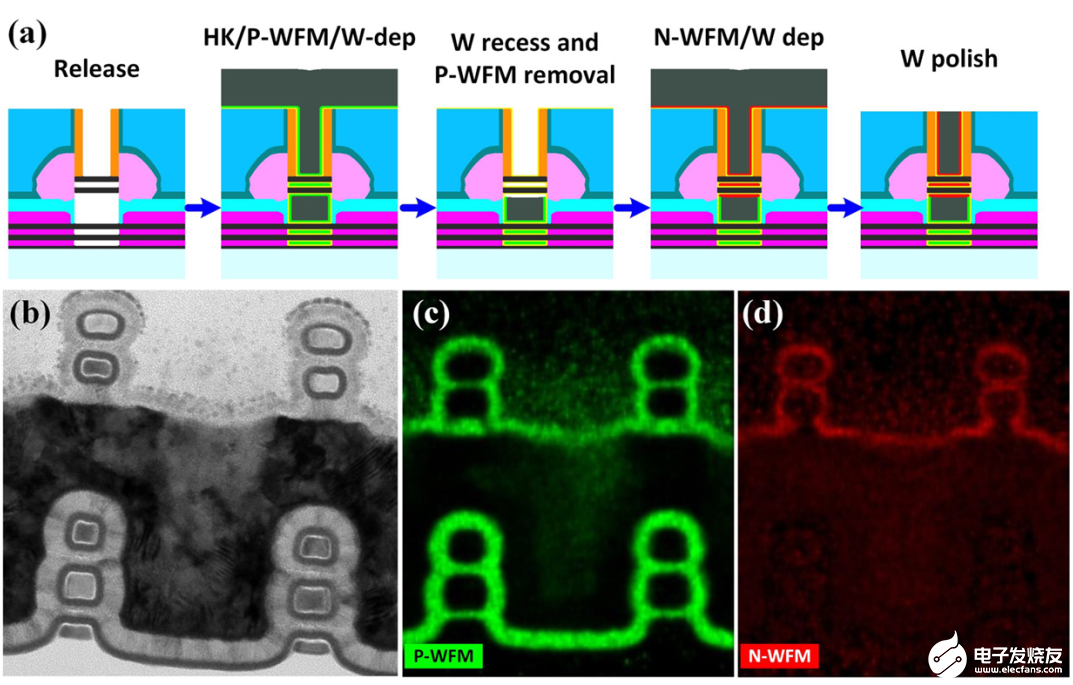

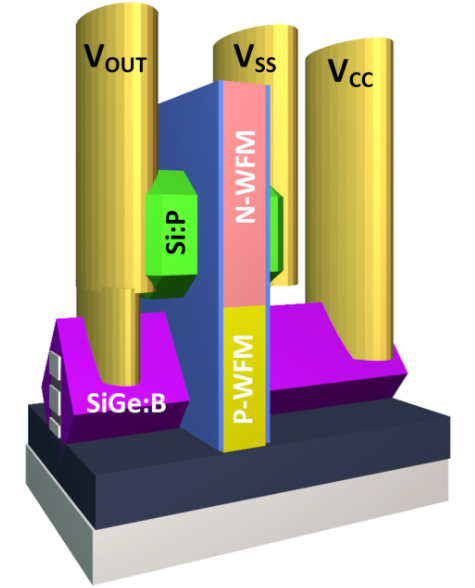

CMOS 設備已經從平面發展到 FinFET,馬上就將在 3nm 制程節點上轉為 nanosheet。進一步縮小的電路需要堆疊NMOS 和 PMOS。 英特爾的工程師打算使用這些組件來構建最簡單的 CMOS邏輯電路,即逆變器(inverter)。它需要由兩個晶體管組成,兩個電源連接,一個輸入和一個輸出連接。即使是像今天晶體管并排放置的設計中,這種布局也已非常緊湊了。但通過堆疊晶體管,調整互聯,逆變器的面積還可以減半。 英特爾用于構建堆疊式 nanosheet 的方法被稱為自對準工藝,因為它可以在實際上相同的步驟中構建兩種組件。這是至關重要的一點,因為假如出現第二種步驟的話(例如在互相分離的晶片上制造兩種組件再粘合),可能會導致無法對準,進而失敗。 從本質上講,晶體管堆疊技術是對 nanosheet 晶體管制造方式的修改。它從硅和硅鍺的重復層開始,隨后將其雕刻成一個較高的窄鰭,然后蝕刻掉硅鍺,留下一組懸浮的 nanosheet。通常,所有的 nanosheet 都會形成單獨的晶體管。但是在新方法中,為了形成一個 NMOS 器件,頂部的兩個 nanosheet 被連接到了磷摻雜的硅上,而底部的兩個 nanosheet 被連接到了硼摻雜的硅鍺上以產生 PMOS。 「完整的『集成流程』當然會更加復雜,但英特爾的研究者們正希望讓工藝盡可能地簡單,」英特爾高級研究員、組件研究主管 Robert Chau 表示。「集成流程不能太復雜,因為這將影響到制造具有堆疊CMOS 芯片的實用性。這是一個非常實際的流程,可產生可觀的結果。」

逆變器由兩個彼此疊置的晶體管組成,它們的某些部分和互連點是公用的。 「一旦你掌握了這種方法,接下來要做的就是追求性能了,」Chau 說道。這可能將涉及改進的 PMOS 組件,目前它在驅動電流的能力上落后于 NMOS。解決這個問題的答案可能在于在晶體管通道中引入「應變」,其思路是讓硅晶格變形,從而為電載荷創造更快的通路(此處為孔洞)。英特爾早在 2002 年就將應變方法引入其芯片。在另一項 IEDM 的研究中,英特爾展示了一種在 nanoribbon 晶體管中產生壓縮應變和拉伸應變的方法。 除了英特爾之外,其他頂尖芯片工廠和研究機構也在尋求堆疊式的 nanosheet 設計,當然有些時候類似的方法會被命名為互補 FET 或納米薄片場效應晶體管(CFET)。比利時研究組織 Imec 率先提出了 CFET 概念,并于去年 6 月在 IEEE VLSI 研討會上報告了構建它們的過程。不過,Imec 組件并非完全由 nanosheet 晶體管構成——它的底層由 FinFET 組成,頂層是單個 nanosheet。 來自臺灣省的半導體研究中心(Taiwan Semiconductor Research Institute, TSRI)研究人員提出了另一種 CFET 的生產方法,其 PMOS 和 NMOS 需要用不同的 nanosheet 制造出來。英特爾的電路在三個 nanosheet PMOS 上有兩個 NMOS,相比之下更接近于堆疊組件的概念。

編輯:hfy

-

CMOS

+關注

關注

58文章

6025瀏覽量

238879 -

英特爾

+關注

關注

61文章

10196瀏覽量

174686 -

逆變器

+關注

關注

293文章

4905瀏覽量

210967 -

晶體管

+關注

關注

77文章

10020瀏覽量

141684 -

場效應晶體管

+關注

關注

6文章

395瀏覽量

20034

發布評論請先 登錄

下一代高速芯片晶體管解制造問題解決了!

蘋果A20芯片的深度解讀

多值電場型電壓選擇晶體管結構

晶體管電路設計(下)

晶體管故障診斷與維修技巧 晶體管在數字電路中的作用

晶體管與場效應管的區別 晶體管的封裝類型及其特點

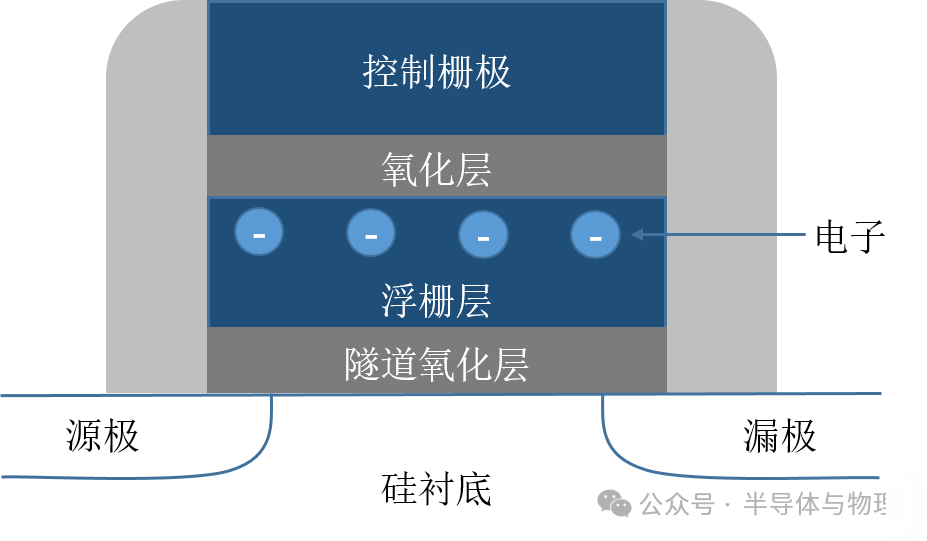

3D-NAND浮柵晶體管的結構解析

深度解讀提高芯片計算的密度晶體管堆疊技術

深度解讀提高芯片計算的密度晶體管堆疊技術

評論