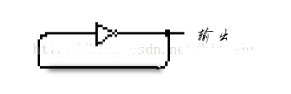

反向器是一個(gè)簡(jiǎn)單的器件,用一個(gè)繼電器就可以實(shí)現(xiàn)。當(dāng)我們把反向器的輸出連接到輸入時(shí),會(huì)發(fā)生什么呢?

當(dāng)輸入為0時(shí),輸出為1;輸出連接到輸入上,此時(shí)輸入又變成1,輸出值變成0;如此反復(fù)。需要特別指出的是,反向器實(shí)際上是一個(gè)繼電器,而繼電器從一個(gè)狀態(tài)轉(zhuǎn)換到另一個(gè)狀態(tài)是需要時(shí)間的。所以,即使輸入和輸出是相等的,輸出也會(huì)很快地改變,成為輸入的倒置(當(dāng)然,隨即輸出也就改變了輸入,如此反復(fù))。

這種電路稱為振蕩器(oscillator)。

振蕩器又常被稱為時(shí)鐘,因?yàn)樗妮敵鲈?、1之間按固有的規(guī)律交替變化。

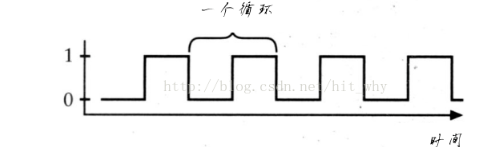

振蕩器從一個(gè)初始狀態(tài)經(jīng)過一段時(shí)間又回到這個(gè)狀態(tài);這個(gè)時(shí)間間隔定義為振蕩器的一個(gè)循環(huán),又叫周期。如下圖所示

周期的倒數(shù)就是頻率,也就是每秒鐘振蕩器產(chǎn)生循環(huán)的次數(shù)。

第一個(gè)圖所示的連接方式叫做反饋,系統(tǒng)的輸出反饋給輸入。

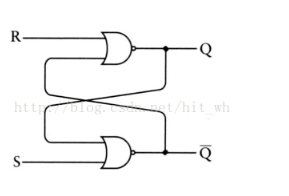

下面看一個(gè)電路圖

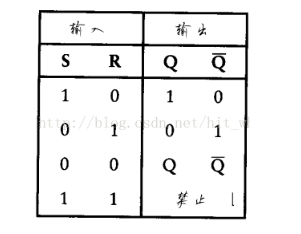

上圖由兩個(gè)或非門組成。實(shí)際上這就是一個(gè)R-S觸發(fā)器。其真值表如下所示

S是置位,R是復(fù)位。當(dāng)R為1時(shí),Q為0,Q非為1;當(dāng)S為1時(shí),Q非為0,Q為1;當(dāng)兩者都為0時(shí),輸出狀態(tài)保持不變。兩者同時(shí)為1的情況是不允許存在的,一定要避免這種情況。

R-S觸發(fā)器的好處是可以記憶電路:Q的狀態(tài)反映了輸入端的狀態(tài)。例如此時(shí)S和R均為0,、Q為1,那我們就知道S之前為1,R為0。

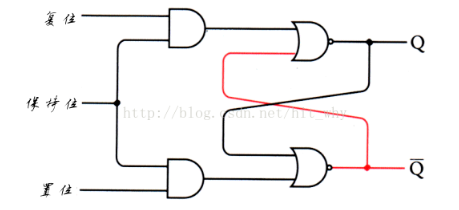

但有時(shí)我們需要記憶功能更強(qiáng)大的電路,于是有了下面的電路。

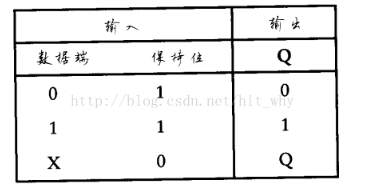

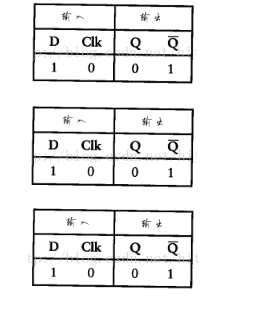

其真值表為

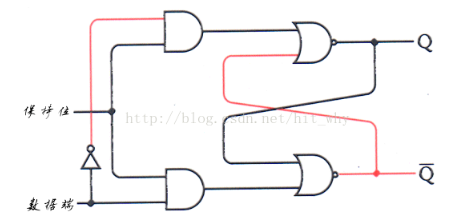

當(dāng)保持位為1時(shí),它實(shí)際上就是一個(gè)R-S觸發(fā)器;當(dāng)保持位為0時(shí),置位和復(fù)位段數(shù)值無論是什么,對(duì)輸出都沒有影響。我們就可以控制輸出的記憶時(shí)間等。但我們需要兩個(gè)輸入,現(xiàn)在有三個(gè)。首先我們知道R-S觸發(fā)器兩個(gè)輸入端不能同時(shí)為1;而且兩個(gè)輸入端同時(shí)為0,也沒有意義,因?yàn)楸3治粸?已經(jīng)包含這種情況。因此將電路圖改為以下形式

當(dāng)保持位為1時(shí),Q反映了數(shù)據(jù)端的數(shù)值,數(shù)據(jù)端就相當(dāng)于置位。當(dāng)保持位為0時(shí),輸入端對(duì)輸出端沒有任何影響。此時(shí)R-S觸發(fā)器處于記憶狀態(tài)。

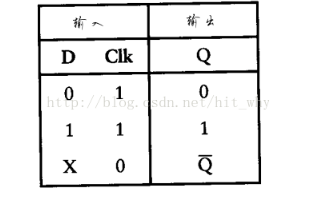

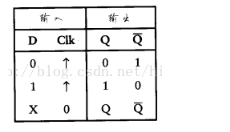

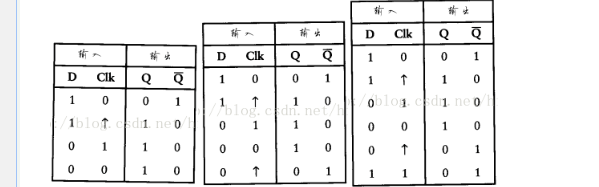

這個(gè)電路又叫電平觸發(fā)的D型觸發(fā)器,電平觸發(fā)是指當(dāng)數(shù)據(jù)端電平為1或者為0時(shí)就會(huì)影響輸出。D代表輸入端(數(shù)據(jù)端),其真值表如下

這個(gè)電路也叫D鎖存器,實(shí)際上就是1位存儲(chǔ)器,多個(gè)1位存儲(chǔ)器可以構(gòu)成多位存儲(chǔ)器。

由以上內(nèi)容可知,每個(gè)鎖存器包括兩個(gè)或非門、兩個(gè)與門和一個(gè)反向器。

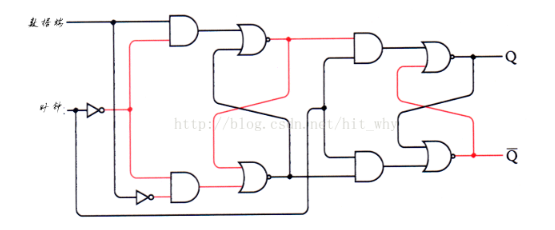

對(duì)某些應(yīng)用而言,上面的電平觸發(fā)器就夠用了,但對(duì)另外一些來說,邊沿觸發(fā)器則更有效。對(duì)于邊沿觸發(fā)器,只有當(dāng)電平從0->1或者從1->0時(shí)數(shù)據(jù)才會(huì)改變。邊沿觸發(fā)器可以由兩級(jí)R-S觸發(fā)器連接而成,如下所示

上面的電路在上升沿觸發(fā),下面分析一下。這里時(shí)鐘同時(shí)控制著第一級(jí)和第二級(jí)R-S觸發(fā)器。進(jìn)一步分析,假設(shè)初始狀態(tài)數(shù)據(jù)和時(shí)鐘均為0,Q也為0。現(xiàn)在數(shù)據(jù)端變?yōu)?,此時(shí)第一級(jí)觸發(fā)器的輸出變?yōu)?,但是由于時(shí)鐘為0,此時(shí)第一級(jí)觸發(fā)器的輸出對(duì)第二級(jí)觸發(fā)器沒有影響。然后,時(shí)鐘從0變?yōu)?。在時(shí)鐘從0->1的瞬間,第一級(jí)的輸入對(duì)第二級(jí)的輸出產(chǎn)生影響,使Q的值變?yōu)?;也就是上升沿觸發(fā)。此時(shí)時(shí)鐘為1,數(shù)據(jù)端的改變對(duì)第一級(jí)也不會(huì)有影響。邊沿D觸發(fā)器的真值表如下所示

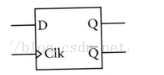

符號(hào)為,其中小三角表示邊沿觸發(fā)。

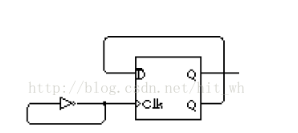

回到本文開始的振蕩器,現(xiàn)在將振蕩器和上面的邊沿D觸發(fā)器連在一起

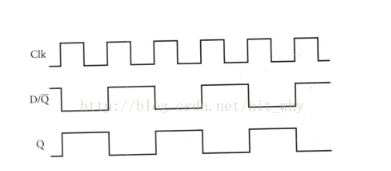

反饋接著反饋。假設(shè)初始狀態(tài)時(shí)鐘為0,Q也為0,Q非為1。當(dāng)時(shí)鐘從0變?yōu)?,Q輸出與D相同,也就是Q非,值為1,Q非變?yōu)?,也就是D此時(shí)也變?yōu)?,此時(shí)時(shí)鐘為1。

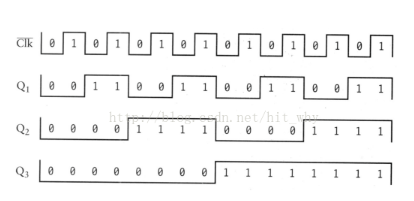

當(dāng)時(shí)鐘從1變?yōu)?時(shí),由于是上升沿觸發(fā),此時(shí)對(duì)輸出沒有影響,時(shí)鐘變?yōu)?。現(xiàn)在時(shí)鐘再次從0變?yōu)?,由于此時(shí)D為0,所以Q變?yōu)?,Q非變?yōu)?,D變?yōu)?。如此反復(fù)。過程如下圖

整個(gè)過程用下圖也可以說明

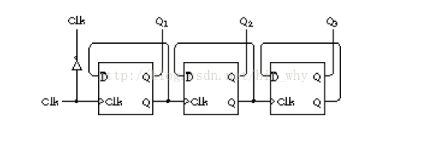

這種電路稱為分頻器,可以看出輸出Q的頻率是時(shí)鐘的一半。我們現(xiàn)在將三個(gè)這樣的分頻器連在一起

然后在輸出的信號(hào)上標(biāo)上0和1,

將上圖順時(shí)針旋轉(zhuǎn)90度,然后把每一行0和1連起來,就會(huì)發(fā)現(xiàn),他們分別對(duì)應(yīng)了0000-1111這16個(gè)二進(jìn)制數(shù)。將輸出Q1、Q2和Q3逆序連起來就組成了一個(gè)三位計(jì)數(shù)器。在時(shí)鐘的每個(gè)上升沿這個(gè)計(jì)數(shù)器就會(huì)加1。

將8個(gè)這樣的邊沿D觸發(fā)器連在一起就組成一個(gè)8位的計(jì)數(shù)器。稱為“8位行波計(jì)數(shù)器”。這樣我們就擁有了一個(gè)8位計(jì)數(shù)器。

編輯:hfy

-

繼電器

+關(guān)注

關(guān)注

133文章

5425瀏覽量

150869 -

振蕩器

+關(guān)注

關(guān)注

28文章

3965瀏覽量

140388 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2284瀏覽量

96016 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

165瀏覽量

48501

發(fā)布評(píng)論請(qǐng)先 登錄

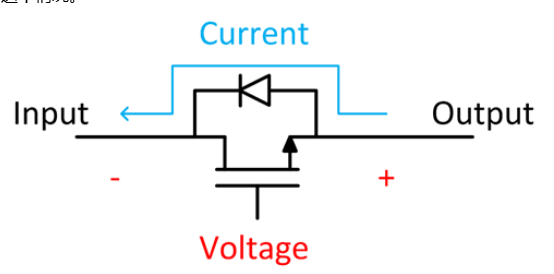

從輸出到輸入,如何才能實(shí)現(xiàn)反向電流保護(hù)

如何將SCLUB的輸出連接到內(nèi)部ADC Delsig的輸入?

如何將這些Vcomp和Vrf輸出連接到34401A電壓輸入?

制作了簡(jiǎn)單的反向比例放大電路,可是輸出總是為正

如何將具有5v TTL輸出的正交編碼器連接到ESP32輸入?

程序?qū)崿F(xiàn)對(duì)輸入時(shí)鐘信號(hào)的7分頻

探究KUKAC4-WorkVisual的輸入/輸出多重連接

PLC與輸入/輸出設(shè)備的連接圖解

反向電流阻斷電路的優(yōu)化設(shè)計(jì)方法介紹

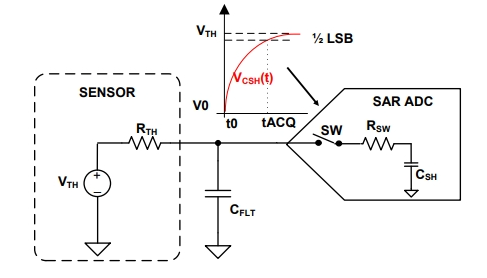

如何將傳感器輸出端與 SAR ADC 輸入端直接連接?

電源變壓器的輸入和輸出線圈的端接形式各自有什么特點(diǎn)?

將差分輸出(隔離式)放大器連接到單端輸入ADC

將5V傳感器和信號(hào)連接到3.3V輸入SAR ADC

連接到PGA900的電阻式電橋壓力傳感器的系統(tǒng)噪聲分析

反向器的輸出連接到輸入時(shí)實(shí)驗(yàn)分析

反向器的輸出連接到輸入時(shí)實(shí)驗(yàn)分析

評(píng)論