創建綜合運行

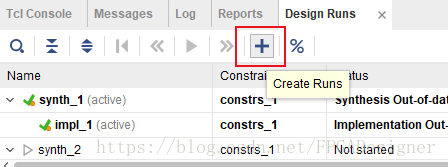

一個“運行(run)”是指定義和配置設計在綜合過程中的各方面,包括:使用 的Xilinx器件、應用的約束集、啟動單個或多個綜合的選項、控制綜合引擎結果的選項。點擊Flow菜單中的Create Funs,或在Design Runs窗口中:

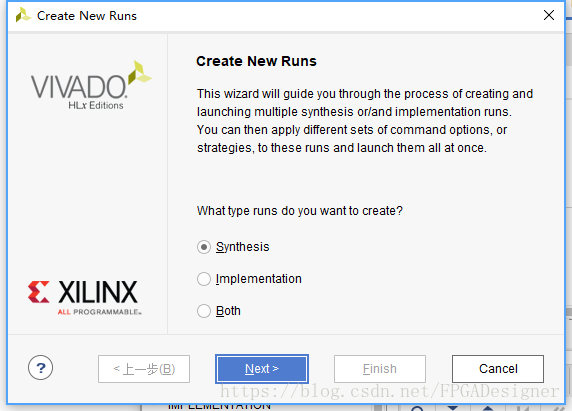

點擊工具欄中的+,即可打開新建運行窗口:

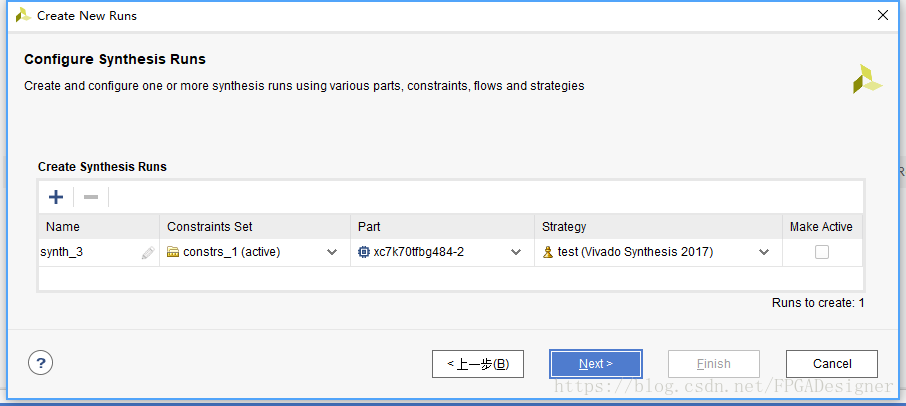

選擇Synthesis,點擊Next,打開配置綜合運行的窗口:

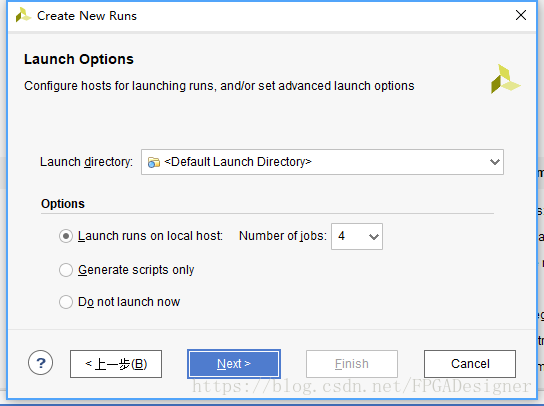

Launch directory選擇啟動運行的目錄;Number of jobs設置了可以同時啟動多少個運行(run);Generate scripts only表示僅生成運行腳本(Windows下為bat文件,Linux下為sh文件);Do not launch now只會保存先前的設置,暫時不會啟動運行。運行的相關情況都顯示在Design Runs窗口中。

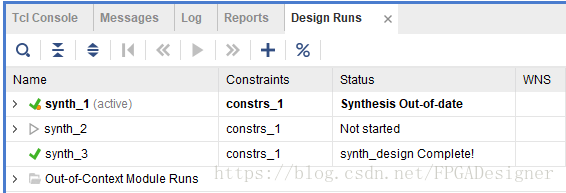

該窗口顯示了工程中所有的綜合和實現運行,進行配置、管理和啟動。一個綜合運行可以包含多個實現運行,窗口中報告了相關的運行狀態(not started、in progress、complete或out-of-date)。修改源文件、約束或工程設置都會導致狀態變為out-of-date。

雖然可以有多個綜合和實現運行,但是都只能有一個為active狀態,所有 的報告顯示的都是active運行的相關信息。比如Project Summary窗口中的編譯、資源等總結信息都屬于當前狀態為active的運行。選擇一個運行,右鍵->Make Active可以設置活躍狀態。

同樣,Flow Navigator和Flow菜單中的Run Synthesis也是啟動狀態為Active的運行。如果需要啟動其它運行,只能通過Design Runs窗口。

使用OOC綜合技術

OOC(Out-of-context)是Vivado提供的一項技術,選擇將HDL對象當作一個隔離模塊運行,完成自底向上的綜合流程。OOC具有如下特點:

- 底層的OOC模塊相對于頂層模塊獨立運行,并且擁有自己的約束集合;

- 運行了OOC模塊之后,再運行頂層模塊綜合時可以直接調用OOC綜合結果,而不需要重新運行一次綜合(除非修改了RTL設計或約束)。

由于不需要每次綜合時都運行整個設計,這項技術可以大大減少頂層模塊的綜合運行時間。IP核就是典型的采用OOC技術的代表,配置好IP核后可以選擇綜合模式為global(與頂層設計一起綜合)或Out-of-context(作為獨立模塊綜合),最好的做法就是選擇后者,以減少整體設計的綜合運行時間。

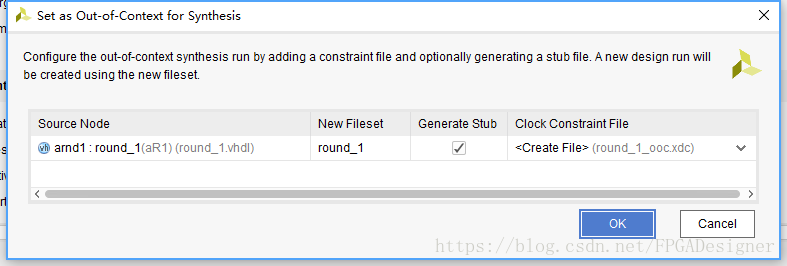

選擇需要添加到OOC運行的模塊,右鍵->Set As Out-Of-Context for Synthesis,彈出如下窗口:

其中Clock Constraint File必須創建一個新的XDC文件或在下拉菜單中選擇一個已經存在的XDC文件,該約束文件中要有該模塊時鐘信號的相關約束。點擊OK后,該模塊會出現在Design Runs窗口的Out-of-Context Module Runs目錄中,還有Compile Order窗口的Block Sources目錄中。

當運行了OOC綜合后,會產生底層模塊的綜合網表和存根文件(stub文件)。存根文件僅描述了底層模塊的輸入和輸出,在綜合頂層模塊時,通過存根文件來調用底層模塊,模塊內部當作黑盒子看待。運行實現時,Vivado會將OOC模塊的綜合網表插入到頂層網表中,從而完成設計。

導入網表文件

可以通過實例化低層次網表或第三方網表來手工構造一個自底向上的設計流程。但需要知道,Vivado綜合工具不會綜合和優化網表,因此XDC約束和綜合屬性也不會對導入的網表產生作用。事實上,Vivado綜合時既不會讀取也不會修改網表中的內容。可以按照如下流程完成相關處理:

1. 創建低層次網表:創建一個工程,以要導入的網表作為頂層模塊,將Settings->Synthesis->More Options設置為-mode out_of_context。這樣綜合時不會為該模塊產生I/O緩存器。綜合后,在Tcl控制臺輸入write_edif name.edf。

2. 設計中實例化低層次網表:頂層設計需要將低層次模塊作為黑盒子實例化,類似于前面提到的stub文件。因此需要創建一個Verilog/VHDL文件,僅定義網表的端口,信號名稱必須與網表中的端口名稱完全匹配。

3. 組合為完整設計:當創建了OOC模式的低層次網表,并且在頂層設計中正確地實例化后,將第一步導出的edif網表添加到工程中。綜合后,Vivado會將網表合并到頂層設計中。

Vivado IP和第三方綜合工具

大多數Xilinx發布的IP核采用IEEE P1735進行加密,只有Vivado綜合工具才支持對IP核的綜合,第三方綜合工具不能綜合Vivado中的IP核。如果想把Vivado中的IP核在第三方綜合工具中實例化,可以參考如下步驟:

1. 在Managed IP工程中(Vivado首頁->Tasks->Manage IP)創建并配置好IP核。

2. 生成IP核的輸出文件,包括綜合設計檢查點(DCP文件)。Vivado會創建一個stub文件(*_stub.v/*_stub.vhd),該文件會包含一些指令阻止從該文件中推斷出I/O緩存器。根據使用的第三方綜合器可能需要修改此文件。

3. 使用Vivado綜合帶有stub文件的Xilinx IP核。

4. 使用第三方綜合工具產生的網表和Xilinx IP核的DCP文件一起運行實現步驟。

編輯:hfy

-

Xilinx

+關注

關注

73文章

2184瀏覽量

124901 -

WINDOWS

+關注

關注

4文章

3610瀏覽量

91237 -

Vivado

+關注

關注

19文章

834瀏覽量

68557

發布評論請先 登錄

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

Vivado HLS設計流程

一文詳解Vivado時序約束

e203在vivado硬件里自定義指令識別為非法指令怎么解決?

Vivado Design Suite用戶指南:邏輯仿真

Vivado之實現布局布線流程介紹

U50的AMD Vivado Design Tool flow設置

每次Vivado編譯的結果都一樣嗎

Vivado使用小技巧

Vivado使用技巧分享:OOC綜合技術運行流程

Vivado使用技巧分享:OOC綜合技術運行流程

評論