作者:易志強,韓 賓,江 虹,張秋云

0 引言

隨著科學技術的快速發展,數據采集系統已廣泛應用于航天、軍事、工業、醫療等各個領域,尤其在高精度產品的檢測和監控項目中發揮著至關重要的作用[1]。在實際工程應用中,要求采集系統具有高速率、高精度、實時處理、系統穩定性好和通道數量多等特點。但是,傳統的數據采集方案多數以ARM處理器(Advanced RISC Machine,ARM)或數字信號處理器(Digital Signal Processing,DSP)作為控制核心,并不能有效解決高速數據采集處理中實時性和同步性的技術難題[2]。

與DSP和ARM相比,FPGA在數據采集領域有著極其重要的地位。FPGA具有時鐘頻率高、內部延時小、純硬件并行控制、運算速度快、編程配置靈活、開發周期短、抗干擾能力強、內部資源豐富等優點,非常適用于實時高速數據采集[3-4]。

針對上述問題,本文設計了一種以FPGA作為主要處理器的16通道實時高速高精度的同步數據采集系統,本方案在實際監測工程中的采樣頻率為200 kHz,運用FPGA合理地控制和協調數據流在各個模塊之間傳輸,進而實現系統所需求的實時、同步和高速采集等功能。

1 系統總體設計

1.1 系統總體設計結構

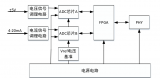

本系統的總體結構設計如圖1所示,該系統由數據前采集前端處理、數據存儲系統、選通開關控制系統和FPGA核心控制系統四部分構成。采集前端處理主要對輸入測量系統的模擬信號進行濾波處理和幅值控制,以保證輸入采集芯片的模擬信號更加穩定;FPGA核心控制系統通過使用FPGA作為核心控制器件,實現了數據同步處理、實時采集、數據緩存、時序約束、端口控制、數據判讀數、據存儲等功能;數據存儲系統的功能是將判讀后的數據實時存儲到Flash中;選通開關控系統則是利用1選8多路復用開關ADG1408和固態繼電器G3FD-X03SN實現被測設備的輸入信號選通和電源通斷控制,使被測設備能安全快速地進入到監測狀態。本系統需要對8個被測設備進行同步實時循環測量與控制,并對測量數據進行記錄判讀、傳輸與存儲。主要包括:供電管理與電源控制、直流電壓電流實時監測、模擬信號通道切換、射頻信號切換、數據存儲等功能。

1.2 系統工作原理

系統上電后,等待FPGA初始化完成,進入等待連接狀態。當外部輸入相關命令參數后,由FPGA接收并解析命令。先控制系統內部選通開關工作,將被選中的設備信號接入采集系統中。然后向被測設備發出控制信息,同時采集系統實時監控被測設備的供電情況,隨后,將采集的數據緩存到FPGA內部隨機存取存儲器(Random Access Memory,RAM)中等待處理。最后將采集到的數據通過FPGA片上先進先出隊列(First Input First Output,FIFO)回傳到外部監視器上進行實時顯示,按照相應規則進行判決并存儲,形成測試數據報表。

2 部分硬件電路設計

2.1 信號調理電路設計

由于輸入系統的被測信號的電壓幅值為27 V,無法直接對被測信號進行采集處理,因此本系統設計了信號調理電路對輸入系統的模擬信號進行濾波處理和幅值控制。該電路通過采用可編程放大器AD8065設計了一個具有較平坦通帶的二階有源巴特沃斯低通濾波器,對前端輸入模擬電壓信號進行濾波處理。隨后,利用芯片MAX4080將模擬電流信號轉換成模擬電壓信號。然后,使用高精度的電阻網絡分壓方式對被測模擬電壓進行比例降壓,再經過高性能運放AD8276進行模擬電壓調理。最后,傳送到模擬數字轉換器(Analog-to-Digital Converter,ADC)進行采樣。經過該硬件調理后,可以保障輸入采集芯片的模擬電壓信號具有平滑、穩定的特性。

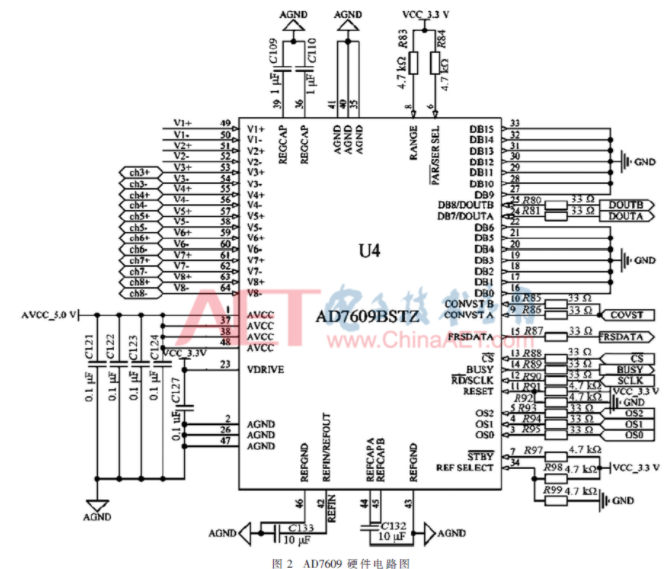

2.2 A/D轉換電路設計

A/D模數轉換器是數據采集的核心器件,影響著整個系統的采樣精度、采樣速率和數據吞吐量,所以芯片選型是采集系統設計中最關鍵的一步。本系統設計采用ADI公司的高精度、低功耗、電荷再次分配逐次逼近型模數轉換器AD7609,該產品是一款8通道、18位、真差分、同步采樣模數轉換芯片。本系統采用兩片AD7609芯片構成了16路通道的數據采集電路。AD7609硬件電路圖如圖2所示,將并行/串行接口選擇輸入端與3.3 V電平直接相連,再將芯片引腳CONVST A和CONVST B短接在一起,并施加同一個轉換信號可以實現8個通道同時轉換。

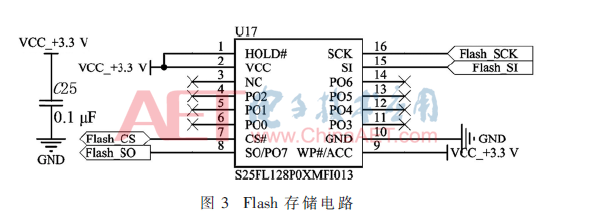

2.3 存儲電路設計

數據采集完成后,將相應通道的采樣數據發送到監視器進行實時顯示和存儲到Flash閃存中,等待外部控制器發送讀取命令。本系統采用ST公司的S25FL128P Flash存儲器進行實時存儲。該芯片存儲容量為128 Mbit,通過SPI接口與外部控制器建立通信,接口的時鐘頻率最大可達到104 MHz。該芯片具有設計簡單、存儲數據穩定和價格低廉等特點,具有廣泛的實用性。Flash存儲電路如圖3所示。

3 系統軟件設計

FPGA軟件設計主要劃分成系統同步時鐘、數據采集、數據緩存、數據存儲4個模塊,下面依次介紹各個模塊的設計。

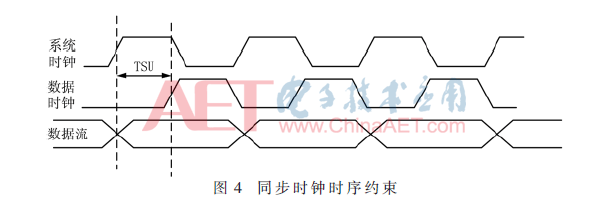

3.1 系統同步時鐘模塊

由于A/D采樣和Flash數據存儲時鐘均為50 MHz,而數據處理和RAM緩存讀寫控制的時鐘均為100 MHz。因此,為了保證系統各模塊之間數據傳輸與處理的同步性,本系統采用FPGA內部的鎖相環(Phase Locked Loop,PLL)IP核倍頻或分頻生成100 MHz和50 MHz的時鐘。通過調用鎖相環設計出一個具有低抖動、低延遲的系統時鐘,保障了高速采集系統運行更加穩定[5-6]。與大多數時鐘同步方案不同,該系統同步時鐘模塊除了使用PLL之外,還要通過時序約束的方式來減小數據與時鐘之間偏斜,重新建立時鐘偏斜的保持時間(Time Setup,TSU)如圖4所示。通過時序約束不僅能實現系統時鐘同步,還能避免出現數據傳輸錯誤。

3.2 數據采集模塊

FPGA對AD7609的控制主要是通過對轉換信號CONVST AB、片選信號CS、時鐘信號SCLK進行控制,完成采樣率調整和采樣啟停控制。如圖5(a)所示,本模塊通過控制AD7609在轉換期間讀取數據的方式進行采樣。當檢測到BUSY下降沿時,則完成所有通道的數據轉換。從圖5(b)的仿真圖可以看出,通過使用系統同步時鐘模塊可以實現16路通道的同步采集功能。由于AD7609的輸出編碼方式為二進制補碼,因此采集完成后可以通過ADC傳遞函數得到轉換后數字信號代表的幅值,轉換公式為:

式中,CODE為轉換后的二進制碼,V+和V-是電源供電電壓,REF則為基準電壓。

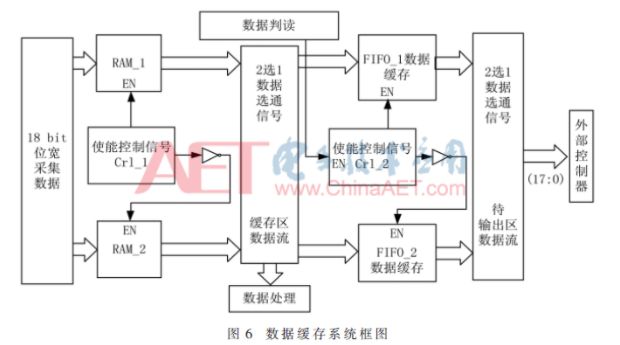

3.3 數據緩存模塊

由于系統為16通道同步數據采集,因此每完成一次采集會產生大量待處理數據。并且由于FPGA與外部處理器通信之間存在硬件差異,會導致其與外部處理器之間存在傳輸處理速度不匹配的問題。因此,為了滿足系統所需實時存儲和傳輸要求,本系統采用了一種乒乓結構的傳輸方式[6]進行數據緩存。利用FPGA內置的知識產權核(Intellectual Property core,IP)資源,在ISE14.7軟件操作平臺上,構建系統所需18 bit位寬的塊RAM和FIFO各兩片進行輪流讀寫操作,實現數據實時緩存的功能。如圖6所示,若使能信號Crl_1處于高電平,則控制RAM_1進行存儲。當RAM_1存儲滿后,產生另一個使能控制信號Crl_2并將使能信號Crl_1電平翻轉,由RAM_2繼續行數據存儲。當使能信號Crl_2到來時,等待系統判讀生效后,則控制FIFO進行數據緩存。若該控制信號處于高電平則FIFO_1進行數據緩存。當FIFO_1緩存滿后則將使能控制信號Crl_2的電平翻轉,由FIFO_2繼續緩存,并將FIFO_1中的數據通過某種協議傳送到外部控制器進行處理。如此周而復始,在RAM和FIFO緩存器中進行乒乓操作,可以實現系統所需實時存儲和傳輸功能。

如圖7數據緩存仿真圖所示,通過時序約束實現了兩個不同緩存器之間的同步讀寫操作,很好地完成了乒乓式的數據緩存功能。

3.4 數據存儲模塊

利用外部處理器設定一個閾值,將緩存進RAM中的數據與閾值比對。若大于閾值電壓,則判讀無效將被測設備電源和信號選通開關斷開;反之,數據判讀有效,需要將采集時間、外部命令輸入以及采集數據組幀后,實時存儲到Flash中。本模塊利用FPGA通過SPI總線與M25P128芯片建立主從關系,實現了Sector擦除、Page編程、地址管理、數據讀取等功能,從而快速、準確地在Flash芯片中實現數據讀寫功能。該模塊采用了摩爾狀態機實現狀態跳轉,既消除了狀態跳轉時造成的毛刺,又很好地完成了存儲與讀取功能。數據存儲與讀取狀態圖如圖8所示。圖中地址管理除了實現頁面讀寫地址轉換外,還要將第一個頁面用于存儲下最后一次存儲的地址,在斷電重啟后,能緊接著掉電前的數據繼續進行數據存儲。

Flash數據存儲仿真圖如圖9所示,數據存儲功能是將8 bit的并行數據通過Flash_SI引腳串行輸入到Flash芯片中實現數據存儲功能。數據讀取功能則需要創建一個8位的移位寄存器將Flash_SO引腳的串行數據轉為并行數據,傳輸到外部處理器進行處理。

4 結論

針對傳統數據采集處理系統不能有效地實現數據在傳輸和存儲過程中的同步性、實時性問題,本文設計了一種基于FPGA的16通道高精度同步實時高速采集系統。該系統采用FPGA控制AD7609在轉換期間讀取數據的傳輸方式,使系統能夠達到200 kHz采樣率。通過合理利用FPGA內部資源,實現數據緩存的乒乓傳輸方式,從而完成了數據的實時傳輸和Flash的實時存儲功能,增強了數據傳輸和存儲的可靠性、有效性和穩定性,極大地發揮出了FPGA的高速數據并行處理能力和時序約束能力。本系統已成功應用于某實際工程監測項目中,具有一定的應用價值。

參考文獻

[1] 黃鴻靖.面向信號模擬的實時數據采集與塊數據傳輸技術研究[D].杭州:浙江大學,2018.

[2] 趙樹磊,劉敬猛,張慧,等.基于FPGA臨空數據采集系統的設計[J].電子技術應用,2018,44(12):123-126.

[3] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2005.

[4] 王建中,楊璐.高速實時系統數據采集與傳輸[J].計算機科學,2016,43(S2):604-606.

[5] 皮代軍,張海勇,葉顯陽,等.基于FPGA的高速實時數據采集系統設計[J].現代電子技術,2009,32(6):12-14.

[6] 張素萍,李朝強,張建芬.一種高速實時數據采集處理系統設計[J].火力與指揮控制,2016,41(7):125-129.

作者信息:

易志強,韓 賓,江 虹,張秋云

(西南科技大學 信息工程學院,四川 綿陽621010)

編輯:hfy

-

FPGA

+關注

關注

1643文章

21964瀏覽量

614114 -

數據采集

+關注

關注

40文章

6954瀏覽量

115701 -

射頻信號

+關注

關注

6文章

225瀏覽量

21278 -

數字信號處理器

+關注

關注

5文章

478瀏覽量

27738

發布評論請先 登錄

康謀方案 | BEV感知技術:多相機數據采集與高精度時間同步方案

請問3通道同時數據采集,每通道200MHZ,計劃使用ADS4129,能不采用FPGA方案?直接通過DSP接收數據嗎?

基于AD51278設計的一個高精度微應變信號采集系統

使用AD7616來采集16通道的電壓數據,數據采集失敗的原因?

ADS8588S 16位、高速4通道、同步采樣ADC數據表

ADS8588S 16位、高速8通道、同步采樣ADC數據表

ADS8588S 16位、高速6通道、同步采樣ADC數據表

基于FPGA的16通道實時高速高精度的同步數據采集系統

基于FPGA的16通道實時高速高精度的同步數據采集系統

評論