PIPE 接口上的數據在 Gen3 的速度下被加密。當調試 PCIe 問題時,能在 PCIe 鏈接上查看各個包會很有幫助。

若要實現此目的,用戶需擁有協議鏈接分析器。由于其成本較高,能接觸到此等設備的用戶不多。隨協議鏈接分析器提供的包分析工具很廣泛,可對鏈接流量進行深入分析。

賽靈思 UltraScale+ 器件的 PCIe? Express Gen3 IP 集成塊有一個功能,可讓您集成一個解擾器模塊,以便解密在 PIPE 接口上被加密的數據。盡管它不能提供與協議鏈接分析器相同數量的分析數據,但它可以在識別潛在問題方面提供幫助,而且在大部分情況下可幫助追蹤問題的根本原因。

本文將詳細介紹如何通過識別來自鏈路并進入 PCIe IP 的不同類型的 PCIe 包來分析解擾器模塊的輸出數據。

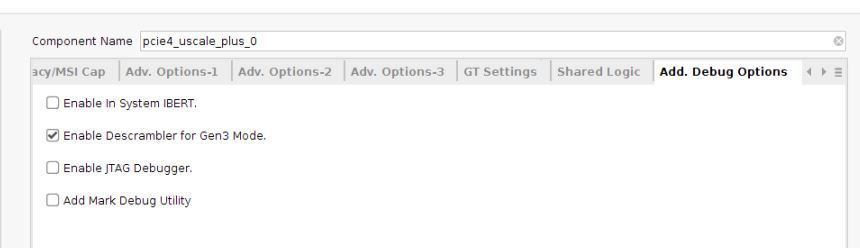

解擾器模塊在 PCIe IP 配置 GUI 中被使能,具體如下:

解擾器模塊只在 Gen3 模式中被支持。

如果復選框變成灰色,要確保配置 GUI 的“Basic”標簽中的鏈接速度被設為 8.0 GT/s。如果該選項不可用,請將“Basic”標簽中的“Mode”設為“Advanced”。

為了追蹤 PIPE 接口上有效 PCIe 包的起始點,該接口提供了兩種信號:*_sync_header 和 *_start_block。

為了確認 rx_data 上的數據是否為有效包,請檢查以下各項:

- *_data_valid 已被有效

- *_start_block 已被有效

-

*_sync_header 為“1”或“2”。

- 如果該值是“1”,則表示是“Ordered Set”的起始點。

- 如果該值是“2”,則表示是 TLP 或 DLLP 包的起始點。

被解擾的數據分析也可在仿真中進行。

以下的波形圖來自與 IP 一起生成的 Gen3 示例設計的仿真。

上文波形圖中所示的 FF00FF00 就是 EIEOS。

被解擾信號上的第一個包將是 EIEOS。

如前文所述,*_start_block 必須有效,而且下文波形圖中所示的 *_sync_header 信號應為“1”。

一旦所有均衡狀態都已完成,在進入 L0 狀態之前,您應該看到 555555E1。

這就是 SDS(數據流起始點)。一旦您看到了 SDS,則意味著有序集交互已完成。接口上的下一個包類型將是初始流量控制信用,即,我們應在接口上看到 DLLP 包。

在下文的波形圖中,DLLP 包為 InitFC1-P。

DLLP 包格式共有四種:

- ACK 或 Nak DLLP 包格式

- 功耗管理 DLLP 包格式

- 流量控制 DLLP 包格式

- 供應商特定 DLLP 包格式

每一種 DLLP 包的長度都是 6 個符號。 有關解碼 DLLP 包內容的信息,請參閱 PCI Express 規范。在下文的波形圖中,“60”是 InitFC-Cpl(Cpl 代表 completion)。“50”是 InitFC-NP(NP 代表 Non-Posted)。

UpdateFC-P 以“80”開始。被解擾數據中的更新值為十六進制,因此需要將其轉化為十進制,以便獲得可用信用的準確數字。

有序集總是按通道來的。每條通道都有其自己的有序集。 DLLP 和 TLP 被跨通道分配;每條通道一個字節。

DLLP 只在 lane-0、lane-4 或 lane-8 中開始,即,F0 只能在 lane 0、4 或 8 上。TLP 可在任何通道上開始。

TXRATE 表示鏈路運行的速度。向 Gen3 速度的過渡在“Recovery.Speed”(0C)LTSSM 狀態中發生,如以下波形圖所示。

在 L0 狀態之前以 Gen1/Gen2 速度運行的包未被加擾,它僅在 Gen3 速度下被加擾。在 PIPE 接口上以 Gen1/Gen2 速度運行的有序集可被直接讀取。但是,所有速度的所有內容在 L0 狀態中都會被擾碼。下面的波形圖顯示了在 Gen1 速度時的捕獲。

在這里,“4A”系指其 TS1 有序集。只有在速度如 TXRATE 所示變化至 Gen3 時才需要解擾器模塊。

下列波形圖中的 AAAAAAAA 表示一個 SKP 有序集。

E1 表示 SKP_END 符號的定義詳見如下所示的 PCIe 規范。

下面的波形圖顯示了在 Gen3 鏈接上的一個 TS1 有序集。所示的“1E”表示在 Gen3 速度時的一個 TS1 有序集。

下面的波形圖顯示了每條通道中的一個 TS1 有序集。它不會跨越多條通道。它在所有通道上都相同,只是通道號不同。在下面的波形圖中,通道號分別為 00 和 01。

這里的“0E”是 Symbol-4。Symbol-4 在規范中的定義如下:

0E= 0000_1110。當我們將這些位映射到規范中的 Symbol-4 描述上時,它表示 Gen3 速度得到了支持。

Symbol-6 在 LTSSM 所處的不同狀態中具有不同含義。在如下所示的波形圖中,LTSSM 為“28”,則意味著它位于 phase-0 中。

Symbol-6 為 20,即 001_0000。由于它在 phase-0 中,則位 1:0 被設為“00”。

下面的波形圖顯示了一個完整的 TS1 有序集。

下面的波形圖顯示了設置為 Gen3 速度的一個 TS2 有序集。“2D”表示它是一個 TS2 有序集

至此,我們已討論了有關有序集和 DLLP 的內容,那么現在我們來看一下如何在 PIPE 接口上識別 TLP。

每個 TLP 都以 STP(TLP 包起始點)標識開始。因此,在解擾器中查找具有 *_start_block = 1 和 *_sync_header= 2 的任何“nF”。

每個 STP 標識都是 4 個符號并表示 TLP 的開始。

STP 字段的定義詳見下圖所示:

以下是 MemWr(存儲器寫入 TLP)的示例。請注意,這是一個 x4 鏈接,因此所有內容都被跨越分配。下面的波形圖取自示例設計仿真。

該波形圖顯示了來自主機測試平臺而通過 PCIe 硬塊的 CQ 接口進入用戶邏輯的存儲器寫入傳輸事務。該傳輸事務在 PIPE 接口上具體理解如下:

開始從 LSB 讀取:

DW0 = ClkCycle0-Byte0 (Lane-0 to Lane-3) -> “6F-80-20-1D” -> STP token DW1 = Header starts here -> ClkCycle0-Byte1 (Lane-0 to Lane-3) -> “40-00-00-01” -> Indicates Fmt/Type = 0x40 which is a 3DW MemWr request, Length = 1 DW2 = ClkCycle0-Byte2 (Lane-0 to Lane-3) -> "00-00-00-0F” -> "0000- ReqID, Tag – 00, 1st DW Byte Enable = "F" DW3 = ClkCycle0-Byte3 (Lane-0 to Lane-3) -> “00-00-00-10” -> Address = 'h10 DW4 = ClkCycle1-Byte0 (Lane-0 to Lane-3) -> “04-03-02-01” -> Payload (Byte0 to Byte3, 01-> MSB, 04-> LSB)

編輯:hfy

-

存儲器

+關注

關注

38文章

7632瀏覽量

166354 -

賽靈思

+關注

關注

33文章

1795瀏覽量

132105 -

PCIe

+關注

關注

16文章

1322瀏覽量

84644 -

GUI

+關注

關注

3文章

674瀏覽量

40723

發布評論請先 登錄

PCIe 5.0市場加速滲透,PCIe 6.0研發到來

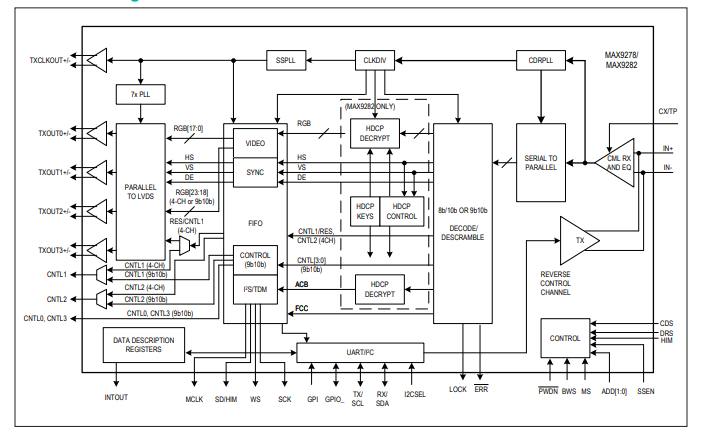

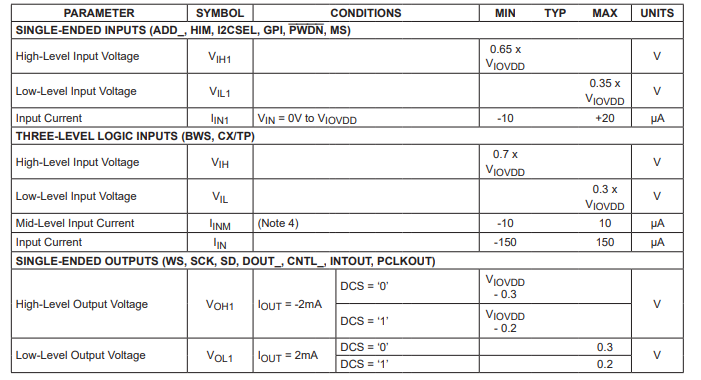

MAX9278/MAX9282用于同軸電纜或STP輸入和LVDS輸出的3.12Gbps GMSL解串器技術手冊

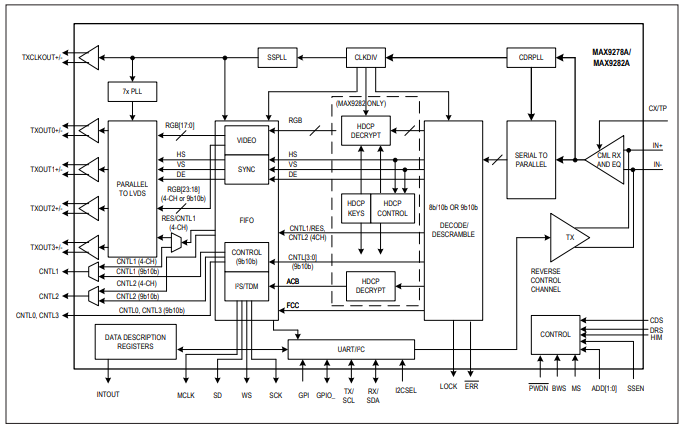

MAX9276A/MAX9280A 3.12Gbps GMSL解串器,用于同軸或STP輸入及并行輸出技術手冊

MAX9278A/MAX9282A 3.12Gbps GMSL解串器,用于同軸電纜或STP輸入和LVDS輸出技術手冊

nvme IP開發之PCIe下

nvme IP開發之PCIe上

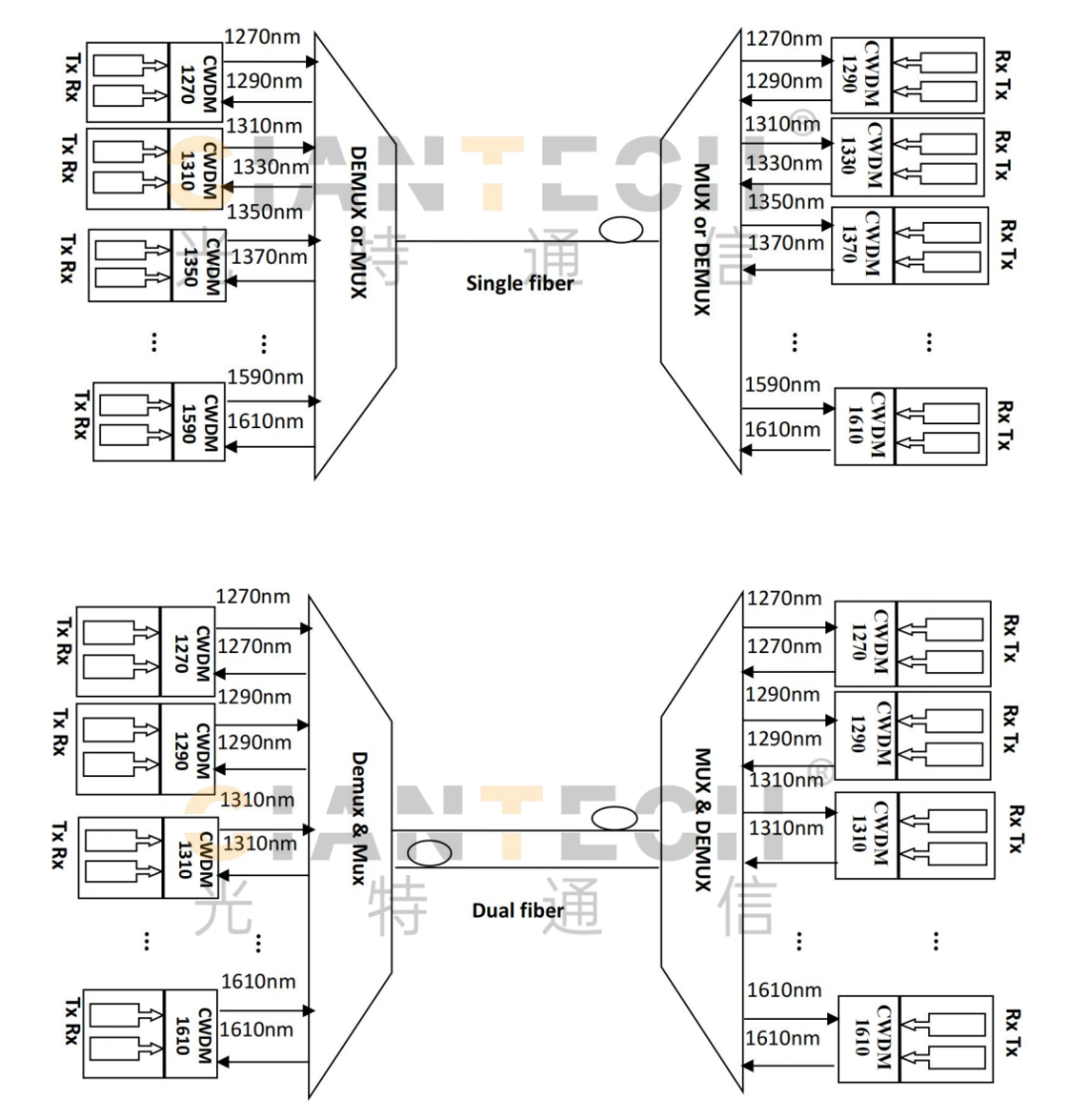

淺談CWDM波分光模塊

VIAVI Xgig4K-PCIe-X4-FL飛行引導插入器適用于PCIE4.0在被測設備和VIAVI協議分析儀機箱箱之間提供數據信號連接

熱解粒子探測器干嘛用的

艾體寶干貨 OIDA之四:掌握數據包分析-分析的藝術

CDCI6214超低功耗時鐘發生器(具有PCIe支持、四路可編程輸出和EEPROM)數據表

LMK00334-Q1四路輸出PCIe第1代至第5代時鐘緩沖器和電平轉換器數據表

LMK00334四路輸出PCIe第1代至第5代時鐘緩沖器和電平轉換器數據表

DS90UB936-Q1雙路3Gbps、MIPI CSI-2輸出、FPD-link III解串器集線器數據表

DS90UB954-Q1雙路4.16Gbps、MIPI CSI-2輸出、FPD-link III解串器集線器數據表

淺談PCIe包分析解擾器模塊的輸出數據

淺談PCIe包分析解擾器模塊的輸出數據

評論