周麗娜(Ally Zhou)女士擁有十多年 FPGA 設計、EDA 工具和多年客戶支持的經驗。Ally 曾先后在同濟大學,芬蘭米凱利理工學院和復旦大學求學,獲得工學碩士學位。加入賽靈思公司之前,曾在 Synopsys 工作,主要負責 FPGA 綜合和 ASIC 原型驗證方案的支持。

賽靈思技術市場專家周麗娜(Ally Zhou)

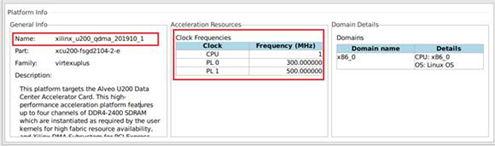

在本篇文章中,我們將介紹如何使用 Vitis 在 Alveo 板卡上開發和部署硬件加速應用。包括可用資源及文檔,如何安裝所需的開發工具和軟件包,以及如何使用賽靈思 Github 加速用例。視頻演示部分會向大家詳細展示如何使用 Vitis 圖形化界面和命令行流程在 Alveo U200 板卡上進行加速用例的開發和部署。

開始前的準備工作

了解和安裝 Alveo 板卡

您可以在賽靈思官網主頁下載產品選型手冊,適用的加速應用,上手指南,支持的工具等文檔。在開始之前請先查閱上圖所示 UG1301 文檔正確安裝 Alveo 板卡。

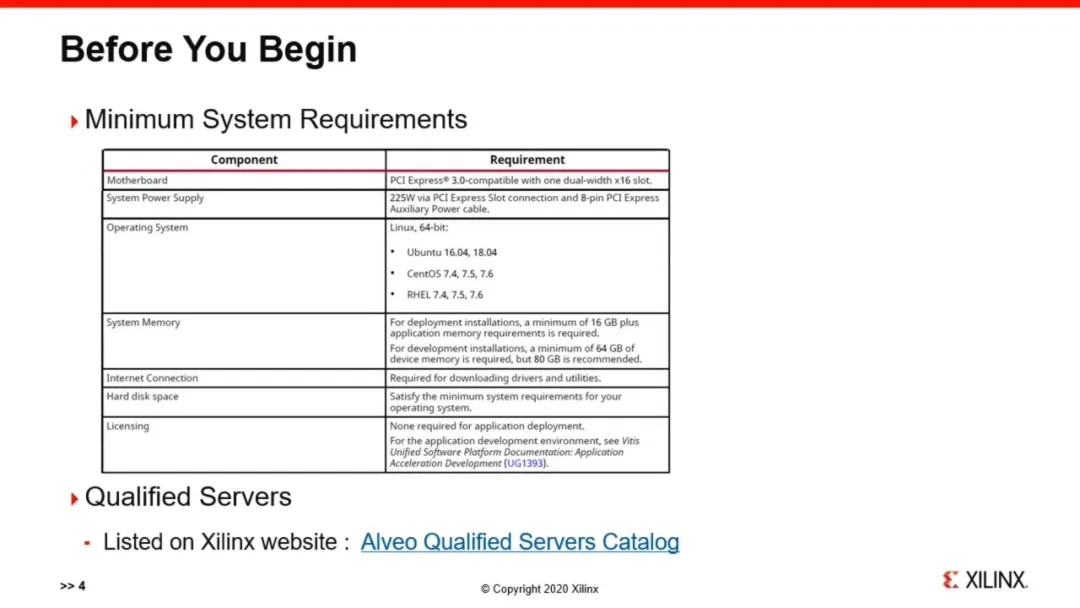

系統配置很重要

賽靈思提供了關于系統配置的詳細信息,包括認證的服務器,支持的操作系統,最低系統配置要求等等,在開始安裝 Alveo 板卡前,請務必保證你的系統滿足了文檔列明的最低要求。

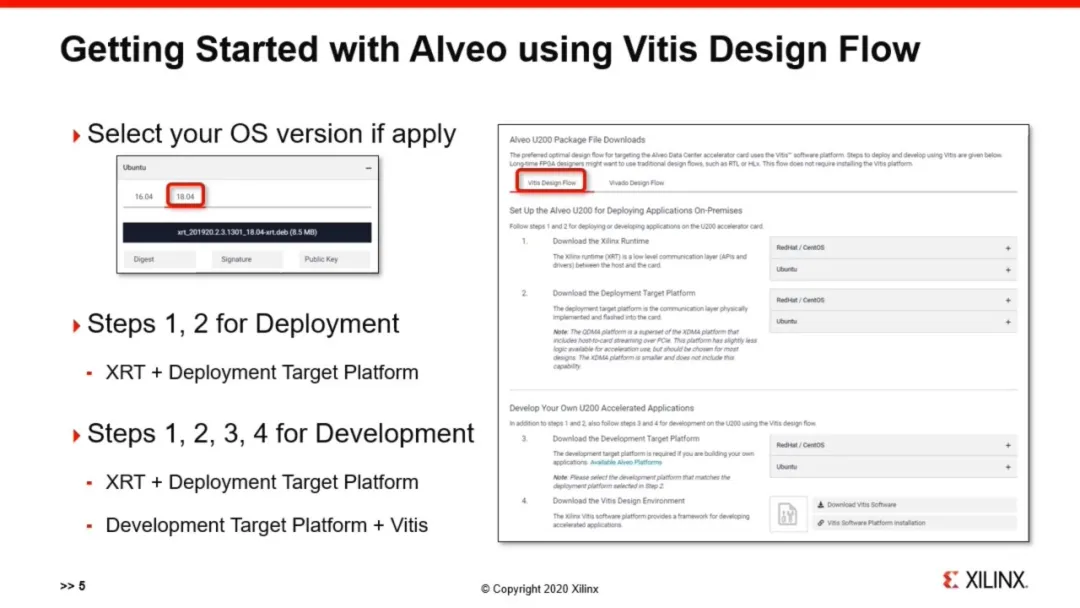

開始您的設計

在 Alveo 的主頁(鏈接見前文)上,選擇了你想要使用的 Alveo 板卡后,點開“Getting Started” 標簽,就可以發現安裝這塊板卡所需的步驟和相應的軟件包。step by step, so easy.

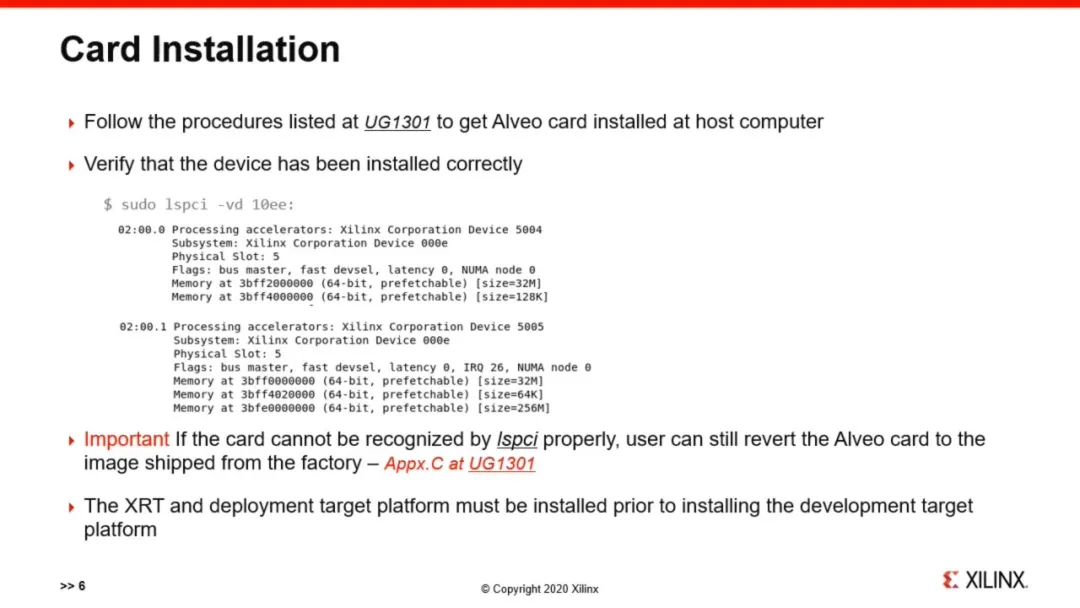

軟硬件環境就緒

一旦板卡已經被成功安裝,并裝好了所需軟件,你可以看到類似屏幕顯示的信息。再次強調,必須嚴格按照文檔或網頁列明的步驟來安裝你的板卡。

編輯:hfy

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613846 -

asic

+關注

關注

34文章

1242瀏覽量

121953 -

賽靈思

+關注

關注

33文章

1795瀏覽量

132102 -

Vitis

+關注

關注

0文章

147瀏覽量

7817

發布評論請先 登錄

【米爾FZ3深度學習計算卡試用體驗】搭建Vitis Ai系統平臺并測試

Vitis 統一軟件平臺簡介 可實現最高的AI推斷性能

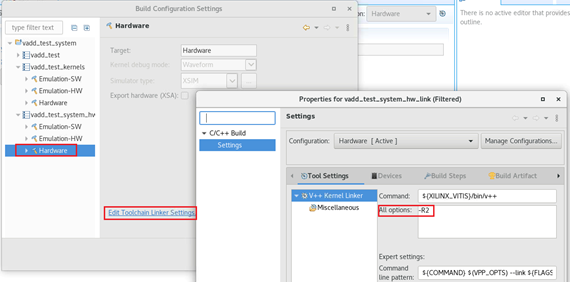

如何在Vitis中封裝加速平臺?

怎么在Vitis中設定Kernel的頻率?

怎么在Vitis加速設計中為Kernel創建面積約束

基于Vitis HLS的加速圖像處理

基于軟件的Vitis AI 2.0加速解決方案

如何在Vitis中設定Kernel的頻率

基于vitis的模型編譯器在FPGA上加速投產進程

在賽靈思FPGA SoC平臺上使用VITIS AI加速人工智能應用

淺談Vitis AI 3.5發布亮點

Vitis 統一軟件平臺文檔:應用加速開發

Vitis AI RNN用戶指南

Vitis在Alveo 板卡上加速應用案例

Vitis在Alveo 板卡上加速應用案例

評論