目前,電視節目的拍攝、制作、傳輸到播出正在實現數字化。MPEG視頻音頻編碼標準的出現,解決了電視信號數字化后信息量過大而信道帶寬有限的問題,加上數字視頻硬件方面的產品不斷進步,促進了各種數字視頻產品的推出,這一切都預示著電視廣播全面步入數字化的時代。數字電視產品的開發不僅能給觀眾帶來高品質畫面和音響效果的享受,而且MPEG-II視頻音頻壓縮的ATM網接入技術的開發為VOD(視頻點播)的時代鋪平了道路。

目前世界上的數字電視系統標準有歐洲的DVB系統和美國的ATSC系統。這兩種系統在視頻壓縮上都采用MPEG-II標準,在聲音上DVB系統采用MPEG-II的音頻壓縮標準,ATSC系統則采用杜比AC-3壓縮技術。本文介紹C-Cube公司MPEG-II編碼器芯片DVxpert-II,它可用于歐洲DVB標準常規數字電視的前端系統的產品開發中。

1 芯片簡介

C-Cube公司開發的視頻處理單芯片DVxpert-II是在該公司DVx的MPEG-II單芯片編/解碼結構的基礎上提高了性能的處理器。它可以產生高品質的4:2:0和4:2:2 MPEG-II圖像,同時壓縮率也有所提高。該芯片能實現視頻編碼(video encoding)、解碼(decoding)和編/解碼(codec)三種功能,可實現運動補償、分塊/離散余弦變換壓縮算法。

DVxpert-II處理器的核心是32位Micro SPACR RISC Core處理器,工作頻率為100mhZ。該處理器內有一個16K字節指令的高速緩沖存儲器(I-Cache)和一個8K字節的數據存儲器(Data Memory)接口,這是一種可編程可升級的結構。芯片采用數據存儲器而不是數據緩沖器,目的是使軟件能更多地控制存儲器,并允許重復進行DMA傳輸。此外,DVxpert-II處理器還有兩個協處理器:DSP協處理器和運動估計協處理器(Motion Estimator),減輕了RISC處理器運算的負擔,它們共同完成視頻壓縮編碼算法,提高了編碼速度。DSP協處理器每秒鐘可執行大約16億個算術操作指令(1600MOPS),執行向量從存儲器到存儲器的指令,這能提高從RISC到DSP流量操作速度。其8K字節存儲器有兩個緩沖區(兩個塊),可允許DMA和DSP同時操作。

DSP協處理器能完成以下功能:①解電視電影模式;②活動測量;③運動補償;④自適應暫時濾波;⑤線性濾波和篩選;⑥DCT變換和逆DCT變換(12位);⑦量化和逆量化;⑧變長的Huffman編碼和解碼。

可編程運動估計協處理器(運動估計器ME)支持所有的塊匹配和運動估計類型,它從RISC處理的CPU中取得運動估計的命令并返回結果。每次運動估計完成后會產生一個中斷。

很多公司都有自己所開發的單芯片MPEG-II編碼的LSI。進行DCT及運動補償等演算所需的電路結構各不相同,C-Cube公司開發的DVxpert-II等芯片為大部分處理工作由RISC處理器及DSP等完成的“處理器型”芯片,與之配套的還有C-Cube公司開發的軟件,即微碼(.ux)文件。該文件包括進行視頻壓縮的代碼以及初始化DVxpert-II處理器的存儲器和下面要介紹的處理器外掛的SDRAM。因為它的可編程性能好,只要改換輸入到處理器的微碼,就可以變更壓縮算法或修正軟件的差錯。

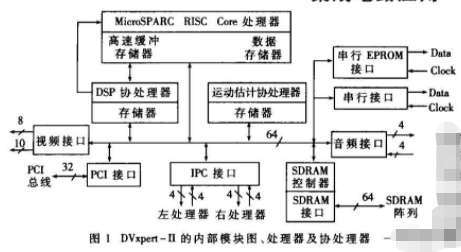

DVxpert-II的內部模塊框圖如圖1所示。

由圖中可見,DVxpert-II處理器是利用PCI總線接口與主機等設備相通信的,主機必須用PCI總線驅動處理器,控制編碼過程;壓縮好的視頻比特流也必須經PCI總線存儲到主機內,PCI接口由主機時鐘(33MHz)驅動。

DVxpert-II處理器還有與串行ROM的接口,開發人員可選擇利用串行EPROM裝載部分初始化程序。在本開發系統中,為了使硬件電路簡化,所有全部初始化過程都由驅動程序經PCI總線接口完成(可省去串行EPROM)。

該芯片還可外掛64bit同步動態RAM(SDRAM),實際電路采用4片16M比特的SDRAM實現8M字節外部存儲器,存儲C-Cube公司的微碼和數據,并可由開發人員分配存儲空間。當處理器進行MPEG-II視頻編碼時,SDRAM所含具體內容如下:①應用程序微碼;②視頻幀捕獲緩沖區;③運動估計取樣視頻緩沖區;④預測的重構幀緩沖區;⑤參考幀;⑥速率緩沖區;⑦用于編碼算法的本地表和其他數據。

處理器有視頻接口,可輸入/輸出未壓縮的數字視頻流;還有音頻接口,可輸入/輸出未壓縮的數字音頻(為獲得與視頻同步的信息)。DVxpert-II處理器只能進行視頻編碼,而未壓縮的音頻數據只能經PCI總線送到主機存儲器,在DVxpert-II處理器外進行軟件壓縮。

本開發系統進行4:2:0Main Level @ Main Profile 的視頻編碼,僅用一片DVxpert-II處理器,因此可不用其和另一處理器相連的IPC的接口。

2 驅動程序的開發

虛擬設備驅動程序可包含對設備進行操作的設備專用代碼,任務具有可設操作模式,需保存數據的硬件設備都需要有虛擬設備驅動程序。虛擬設備保持了每個應用程序的設備狀態軌跡,并能保證當應用程序繼續執行時設備處于正確狀態。編碼器將DVxpert-II集成于即插即用的PCI插卡,因此要開發該PCI設備的虛擬設備驅動程序(VxD)以支持編碼器芯片的正常工作,該軟件采用Microsoft VC 6.0開發,在WIN98操作系統下運行。WIN98操作系統的基本系統體系結構分成Ring0層和Ring3層,它們能提供不同級別的系統保護。Ring3層通過Intel處理器體系所提供的保護服務與其他的運行進程隔開,以達到保護的目的。Ring0層由虛擬機管理器(VMM)等構成。VxD是一個管理硬件設備或者已安裝軟件等系統資源的32位可執行程序,運行在Ring0層,處理系統或外設中斷及DMA操作等,它使基于Windows的應用程序可有效地實現多任務。WIN95/98的VxD對即插即用提供支持,因此當DVxpert-II處理器電路設計成即插即用PCI擴展卡時,起動后可由操作系統自動檢測到它。VxD的軟件開發可利用美國Vireo.Software公司推出的VtoolsD for Win95開發工具包進行,該VxD被開發成可動態加載/卸載的驅動程序,以保護模式駐留在擴展內存中。VtoolsD中的Quick VxD程序可提供一些選項來快速生成VxD代碼框架。編碼器的VxD應包括:設備的初始化,處理中斷信號,以及與運行在Ring3層進行通信。

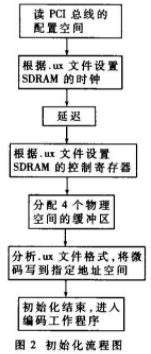

設備的初始化流程圖如圖2所示。

微碼數據經PCI總線可以兩種模式(從模式和主模式)傳輸到編碼器設備上。從模式一次只能傳一個32位的雙字,速度慢,主模式以DMA方式猝發,可高速傳大量數據。微碼中寫入處理器控制總線寄存器的部分只能采用從模式方式;微碼中寫入SDRAM中的數據根據.ux文件要采用DMA方式,這要通過設置處理器的一些寄存器實現。

WIN95/98的內存為平滑線性內存模式,線性編址模式簡化了應用軟件的開發過程,提供了存取虛擬地址空間的功能,使用戶可存取的內存地址達4GB,2GB給應用軟件,2GB給操作系統本身,因此VxD能申請4個BUFFER,用于存放DMA方式傳輸編碼時所用的命令和消息,該BUFFER表示物理地址連續的空間,同時還可映射為相應的線性地址空間。

虛擬設備驅動程序可處理編碼器工作時發來的中斷,其服務過程如下:

①首先清除中斷;②ISR把BUFFER中的消息存放到消息隊列;③ISR檢查當前消息的序列號:如果有錯,轉到處理錯誤的函數,若無錯,ISR把命令隊列中的下一個命令移到Ring0層的BUFFER內;④分析消息隊列內的新消息,并且寫相應的新命令。

在WIN95/98中,Win32API提供設備輸入輸出控制(DeviceIoControl)來支持Ring3到Ring0的直接調用,它通常用于調用動態加載的VxD;Ring0層則可通過OnW32DeviceIoControl(PEOCTLPARAMSpDIOCParams)中的pDIOCParams->dioc_OutBuf向Ring3層傳遞數據。

DVxpert-II提供的PCI接口和編程接口使其可方便地集成到PC插卡上,而且可由驅動程序對其進行較靈活的控制。目前該VxD已在使用之中,編碼器設備工作良好。

責任編輯:gt

-

處理器

+關注

關注

68文章

19884瀏覽量

235001 -

芯片

+關注

關注

459文章

52471瀏覽量

440387 -

存儲器

+關注

關注

38文章

7648瀏覽量

167283

發布評論請先 登錄

基于Nios II和eCos的串口通信程序開發

基于ARM的MPEG 4視頻編碼器

MPEG-4 ASP視頻編碼器的軟件優化設計

MPEG-2系列編碼器

WinCE下光電編碼器的驅動程序設計

NIOS II的特性及開發設計流程

基于Arria II GX FPGA的開發方案

MPEG-2壓縮編碼器原理

基于MPEG-4的視頻DCT編碼器的實現

uC/OS-II 應用程序基本結構及重要的API介紹

8線3線優先編碼器的設計使用資料說明

MPEG-II編碼器芯片DVxpert-II的功能特點及應用程序的開發

MPEG-II編碼器芯片DVxpert-II的功能特點及應用程序的開發

評論