本文探討了半導體行業的未來以及當前的成本問題以及由此導致的創新停滯。新的定制ASIC的數量正在減少,而在高性能,功率和RF /模擬功能方面,FPGA并未完全填補空白。由單個小芯片組成的異構系統芯片(HSoC),以其最佳工藝制造,并使用異構2.5D技術連接在硅基板上,是未來,技術和業務框架也在不斷發展,以使這逐漸成為現實。

小芯片如何為定制半導體設計提供前進的道路

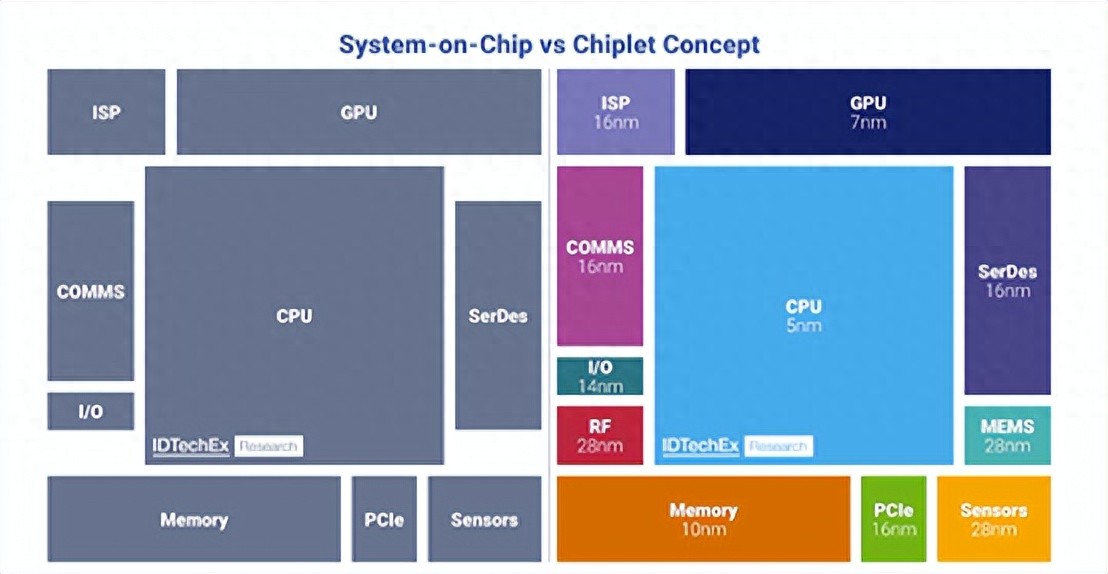

小芯片背后的想法很簡單。小芯片方法不是像過去幾十年那樣一直將所有功能集成到復雜的單片芯片中,而是希望將功能分解為單獨的硅芯片,稱為小芯片。與大多數現成的芯片不同,這些小芯片可以或可以不作為獨立單元運行,并且可能需要連接到另一個小芯片以提供價值。使小芯片與現有芯片區分開的關鍵技術是使用硅中介層將它們連接在一起。多芯片模塊(MCM)包含數個鍵合或倒裝到有機基板的芯片,已經存在了很多年,并具有了許多優勢,例如小巧的外形,成本,工藝優化的功能,以及制造商控制子系統設計的能力。硅中介層通過進一步縮小封裝面積并大大增加管芯到管芯互連的數量,同時又大大降低了信號傳輸能力,進一步邁出了這一步。

硅中介層

導致小芯片可行的關鍵支持技術是硅中介層和2.5D集成技術。在這種方法中,小芯片彼此相鄰地組裝并安裝在一塊硅上,這與小芯片本身的制造可能沒有什么不同。使用硅而不是有機印刷電路板意味著小芯片可以放置得更近,互連的數量可以大得多,從而導致傳統方法無法進行系統分區。此外,與分立式解決方案相比,硅中介層的超小特性極大地降低了互連電阻和寄生電容,從而大大降低了I / O功耗。這使得能夠采用模塊化方法來達到SoC的功耗和尺寸級別。大多數現代SoC的典型結構是采用模塊化的功能方式,并使用先進的微控制器總線體系結構(AMBA)總線將各塊互連。該總線是一種寬并行總線,允許單周期數據傳輸和具有總線仲裁功能的多個主機。

通常,當將有機印刷電路板(PCB)上的多個芯片互連時,通常使用標準的串行接口,該接口允許覆蓋較大的距離,但會在設計中增加成本和邏輯分區。從小芯片設計的角度來看,關鍵是要在異構設計中實現與單片IC中類似的架構。這意味著要具有一種機制,可以跨越小芯片邊界擴展AXI總線。

盡管目前沒有將小芯片連接在一起的標準接口,但仍有許多競爭者。但是,成為標準的一個領先候選者是英特爾的高級接口總線(AIB)。該總線是大規模并行高速總線,它利用硅中介層提供的短傳輸距離和極其密集的互連路由。由于AIB是并行總線,并且在很大程度上是物理層接口(PHY),因此可以輕松地連接到AXI總線,從而提供低延遲和直觀的邏輯操作。使用AIB總線將SoC分解為三個小芯片的潛在情況。可以看出,HSoC的基本架構與在SoC上的架構相同。

功能匹配

由于這些模擬功能的尺寸不按比例縮放,導致不成比例地使用非常昂貴的硅面積,因此在CMOS中集成模擬,RF和密集存儲功能不再有意義。較小幾何尺寸的CMOS工藝也不太適合這些功能。實際上,大多數現代存儲器實際上由堆疊在存儲器控制器小芯片頂部的存儲器小芯片組成。出于密度,物流和制造方面的原因,這些通常使用3D技術構造。傳統接口和功能也是如此。這些功能被設計為在較低的時鐘頻率和/或較高的電源軌上工作,而在最先進的過程中實施則是浪費。

在過去的20年中,模擬設計取得了長足的進步,從而能夠在CMOS中構建高質量的模擬電路。時間精度(利用振蕩器的穩定性)代替了匹配精度的開關技術,以及放寬了精確濾波要求的delta-sigma技術,使設計人員能夠保持模擬的集成。但是,模擬無法像數字方式那樣在面積上擴展-使其集成成本越來越高。此外,先進工藝的擊穿電壓下降和電源電壓開始禁止某些模擬設計。通過分解模擬部分,可以在不僅性能最佳而且價格便宜的過程中設計它們。這種方法還極大地降低了復雜SoC的風險。

產量和再利用

導致大型SoC分解的另一個主要問題是成品率。隨著晶粒變大,缺陷密度驅動的成品率下降。這種產量下降可能對產品成本產生重大影響。通過使用小芯片方法,可以在針對特定小芯片功能的最佳工藝中制造所有管芯,并使小芯片尺寸保持最小,從而可以有效管理與工藝和成品率相關的成本。此外,小芯片以最根本的方式推動IP重用-它們重用經過測試的生產芯片。在此模型中,驗證和的時間大大減少,TTM和最終質量大大提高。使用預開發的硅片和從根本上更簡單的子模塊,可以使開發過程更具可預測性且風險更低。考慮芯片系列時,異構方法允許在多個設計中分攤成本,從而大大降低了總開發成本。最后,可以減少IP許可成本。不必為每次新的SoC開發都為給定的IP支付新的許可費用,而是重新使用小芯片,實際上可以使每次使用小芯片時只需支付專利費用。這導致更多的按需付費方式,并減輕了小批量客戶的負擔。小芯片的使用代表了當今采用的IP重用模型中的進步。小芯片代表了向前邁出的一步,而不是授予IP或硬宏的許可,在該實踐中,IP被簡化為可以實踐并以已知的性能進行測試。異構方法允許在多個設計中分攤成本,從而大大降低了總開發成本。在實踐中,IP被簡化為可以實踐并以已知的性能進行測試。

可升級性

異構設計的最后一個優勢是能夠升級設備并在很大程度上擴展產品的能力。從一組小芯片中創建多種功能不同的產品的能力也很引人注目。例如,通過換出存儲芯片,可以解決新的應用程序,或者達到不同的價格點。隨著網絡安全協議的發展,安全的小芯片可以換出,而無需重新設計整個SoC。最后,隨著接口升級,可以換出新的接口小芯片。從實際的角度來看,這也可以控制特征蠕變,因為整個設計不會重新打開,而僅是需要更改的目標部分。從軍事角度來看,可以對HSoC進行更新以換出小芯片,而無需重新鑒定整個電路板的資格,這也可以在解決過時問題方面節省大量資金并帶來巨大的收益。

責任編輯:tzh

-

芯片

+關注

關注

460文章

52520瀏覽量

440940 -

半導體

+關注

關注

335文章

28918瀏覽量

237941 -

電路板

+關注

關注

140文章

5136瀏覽量

102649

發布評論請先 登錄

功率半導體器件——理論及應用

從原理到應用,一文讀懂半導體溫控技術的奧秘

蘇州芯矽科技:半導體清洗機的堅實力量

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

北京市最值得去的十家半導體芯片公司

【「大話芯片制造」閱讀體驗】+ 半導體工廠建設要求

【「大話芯片制造」閱讀體驗】+跟著本書”參觀“半導體工廠

燦芯半導體ICCAD 2024精彩回顧

Chiplet將徹底改變半導體設計和制造

中國半導體的鏡鑒之路

小芯片如何為定制半導體設計提供前進的道路?

小芯片如何為定制半導體設計提供前進的道路?

評論