消除過孔至過孔耦合噪聲的技巧

眾所周知,多層PCB設計可以減輕高速信號電路的EMI / EMC效應。導電通孔可在PCB的多個層之間提供連通性,為設計人員提供了分離AC和DC信號的空間,可優化組件的位置,并提供足夠的接地層以降低噪聲。

結果,多層PCB趨于更緊湊,從而使設計人員能夠將更多功能集成到更小的外形尺寸中,而在當今世界中,對更小,更強大的電子產品的需求一直在增長,這是至關重要的元素。

但是,盡管與單層板相比,這些多層板具有這些優勢,但多層板并非沒有自己的EMI / EMC挑戰。在設計多層PCB時,尤其是通孔到通孔的耦合仍然是一個具有挑戰性的方面。在這篇文章中,我們將介紹一些消除通孔噪聲的技巧。

什么是Via?

VIA是垂直互連訪問的縮寫。Via也是路徑的拉丁語。結果,該首字母縮寫詞被通俗地視為單詞“ via”,而不是首字母縮寫詞“ VIA”。

就像它的名字所暗示的那樣,通孔在多層PCB的各層之間提供垂直連接。通孔的解剖結構包括:

l桶,是形成通孔主體的導電管。它在多層板上的平面之間鍍覆穿過絕緣層鉆出的孔。

l墊從桶的頂部徑向向外延伸,以將過孔連接到該層上的組件,平面或走線。

l防焊盤是平面層和通孔之間的空隙,可防止平面短路到通孔。

通孔串擾是PCB設計中的主要問題

無論您的通孔是盲孔,埋孔還是通孔,水平應用于走線的對串擾和信號速度的擔憂也適用于垂直過孔。只要您有電流并行流過兩個或更多導電路徑,就會發生耦合。

當耦合干擾嚴重到足以干擾信號質量時,就會發生串擾。串擾可以是電感性的也可以是電容性的,下面讓我們仔細看看這兩種干擾模式。

l感應串擾:在一個通孔中改變信號會產生磁場,該磁場會通過在導體上產生電動勢來干擾“受害者”通孔的信號。

l電容性串擾:當兩個導體之間相隔一個小間隙時,例如通孔的抗焊盤,您會得到一個可以靜電存儲能量的簡單電容器。寄生電容會減慢信號,干擾時鐘速度和時序。

在低速電路中,由于有足夠的時間在反焊盤與平面結之間聚集電荷,因此寄生電容引起的串擾往往是一個更大的問題。在更高速度的電路中,電感是一個更大的問題,因為通孔中信號快速變化產生的磁場會在相鄰的通孔上產生較強的電動勢。

這里有一些提示

PCB設計中的耦合是生活的自然組成部分。訣竅是圍繞這種現實進行設計以防止串擾。這里有一些常見的技巧和竅門,以減少過孔周圍的噪聲。

l差分配對過孔。將多層板中的層之間的通孔作為差分對進行布線(一個通孔載有信號,另一個通孔返回信號)。差分成對的通孔越近,噪聲的降低就越好,但需要權衡較高的寄生互電容。在高速信號電路中,寄生電容并不是問題。

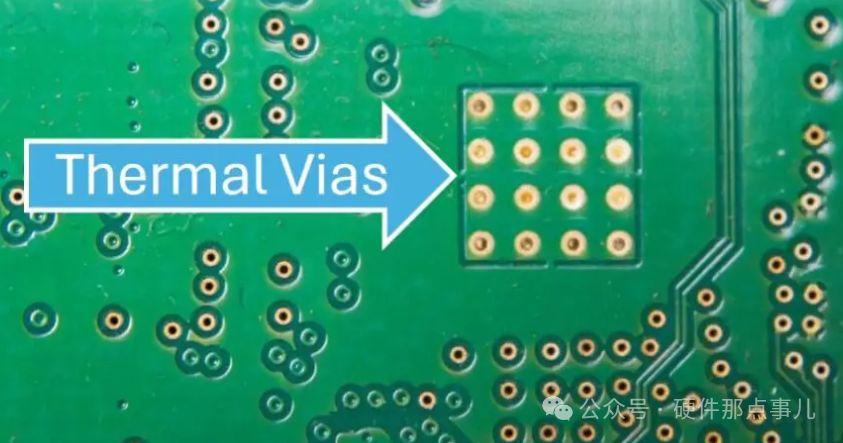

l通孔柵欄:通孔柵欄(又稱通孔屏蔽)是一排通孔,它們沿RF信號的路徑路徑排列,以減少串擾和EMI的影響。

l通孔縫合:您可以在多層板上的兩個平面之間建立牢固的垂直連接,方法是在板上的所有自由區域填充通孔。這減少了返回路徑并導致低阻抗連接。

l去耦電容器:一種防止寄生電容的方法是為系統提供本地電容器,以通過為電路提供穩定的能量儲備來防止電壓尖峰。由于耦合可以是電容性或電感性的,因此去耦電容器在阻抗較高的電感元件較高的高信號電路中效率較低。

結論

僅關注板子水平面中的EMI和串擾已不再足夠。隨著對高速多層板的需求增加,也需要理解并遵循最佳實踐來管理使這些多層配置成為可能的通孔。

圍繞多層PCB的EMI和串擾管理的數學運算可能變得非常復雜。這就是為什么使用3D建模和PCB設計分析軟件來確保最終準備好生產時考慮所有變量的重要性。

-

電路板設計

+關注

關注

1文章

128瀏覽量

16868 -

PCB設計

+關注

關注

396文章

4784瀏覽量

89263 -

PCB布線

+關注

關注

21文章

469瀏覽量

42523 -

華秋DFM

+關注

關注

20文章

3502瀏覽量

5260

發布評論請先 登錄

Allegro Skill布線功能-改變過孔網絡介紹與演示

Allegro Skill布線功能-添加差分過孔禁布區

高速電路中的過孔效應與設計

高速PCB設計過孔不添亂,樂趣少一半

PCB設計距離一樣時,你們知道電路板兩對過孔怎么擺串擾最小嗎?

電路板 Layout 的 PCB 過孔設計規則

過孔的設計孔徑是真的很重要,但高速先生也是真的不關心

PCB過孔的開窗,蓋油,塞油到底是什么意思?廠家EQ該怎么回復?

PCB過孔設計的基礎知識

PCB設計:消除過孔至過孔耦合噪聲的技巧

PCB設計:消除過孔至過孔耦合噪聲的技巧

評論