引言

“計算機組成原理”是計算機科學與工程技術類專業的一門核心課程,是學習計算機硬件系統的關鍵課程。本課程以計算機組成結構為中心闡述基本概念和原理,具體介紹了計算機硬件系統中各大部件的組成原理、邏輯實現、設計方法及互連構成整機的技術。提高該課程的實驗教學水平,對于學生加深對課程的理解,培養學生設計能力和創新能力具有重要的意義。

隨著電子技術的不斷發展,數字系統的設計方法也在不斷地進步,傳統的手工設計過程已經被先進的EDA工具所替代。計算機作為一個典型的復雜數字系統,其設計方法發生了根本性的變革,因此應用EDA技術是計算機組成原理課程實驗改革的方向。

目前高校開展本課程實驗教學的方法有2種:一種方法是利用現有的計算機組成原理實驗儀,該實驗儀已將CPU的各個組成部件全部做好,學生只需按書中要求撥動相應開關就能完成實驗,這種方法的缺點是不利于學生的理解,局限性較大,器件的品種、數量擴展困難,學生的設計難以突破實驗箱的限制;另一種方法是應用EDA技術進行實驗,利用軟件生產商提供的ispDesign-EXPERT等軟件工具進行模擬仿真,并通過可編程器件及相應硬件資源來直觀地觀察實驗結果,加深對理論的理解。實踐證明:基于EDA技術的實驗教學,在鞏固學生計算機組成原理課程理論的學習,熟悉CPU各個功能部件的工作情況,促進學生的感性認識,培養學生計算機應用能力和創新能力等方面起了積極的作用。

1、實施方案

計算機組成原理課程實踐教學包含課程實驗(18學時)和課程設計實驗(一周)2個環節,其中課程實驗主要驗證計算機各部件組成和功能,課程設計實驗主要完成計算機整機設計。課程實驗內容包括:①運算器組成實驗;②乘法器設計實驗;③半導體存儲器實驗;④數據傳送實驗;⑤微程序控制器設計實驗;⑥組合邏輯控制器實驗;⑦并行接口實驗;⑧程序中斷實驗。

課程設計為一個綜合性的實驗,實驗內容是完成模型計算機的設計和EDA實現。課程設計的目標由簡單到復雜分為4個階段,學生可根據進展情況完成不同難度的設計。第1階段完成基本模型機設計與實現;第2階段增加移位控制指令,設計移位運算電路;第3階段設計一個具有較完整指令系統的模型機,該模型機的指令系統包括算術邏輯指令、訪存指令、轉移控制指令、v0指令和停機指令,尋址方式包括立即尋址、直接尋址、間接尋址和相對尋址;第4階段設計一個帶接口的模型機,實現中斷功能和訪問并口、串口功能。

2、實驗環境

本課程實驗硬件環境為:PC一386以上微機、西安唐都科教儀器公司的TDN一CM++計算機組成原理實驗臺;軟件環境為:WINDOWS操作系統、TDN一CM++計算機組成原理實驗軟件CMPP和ispDesigoMERT軟件。PC機用于與實驗臺聯機實時調試,利用實驗軟件提供圖形調試功能,動態實時顯示模型計算機各部件之間的數據傳輸以及各部件和總線上的所有信息。

本實驗系統中使用的大規模可編程邏輯器件是Lattice公司的ispIS11032芯片。isp是指芯片具有“在系統可編程功能”,這種功能可隨時對系統進行邏輯重構和修改。

對ispISI1032芯片的邏輯系統設計是通過使用硬件描述語言或原理圖輸人來實現的,硬件描述語言有ABEL,VHDL等多種語言。

實驗系統中采用ispDesigaEXPERT軟件來對可編程邏輯器件ispIS11032進行編程設計實現。ispDesignEXPERT可采用原理圖或硬件描述語言或這2種方法的混合輸人共3種方式來進行設計輸人,并能對所設計的數字電子系統進行功能仿真和時序仿真,其編譯器是軟件所需要的熔絲圖文件。該軟件支持所有Lattice公司的ispLsI器件。

3、利用EDA技術進行實驗的步驟

采用ispDesiglEXPERT軟件來對可編程邏輯器件進行編程設計實現所需的數字系統功能一般要經過如下步驟。①建立新工程;②輸人原理圖或硬件描述語言進行設計;③對源程序進行編譯;④連接下載電纜;⑤將生成的JED文件下載到可編程邏輯器件中;⑥連接實驗電路;⑦在實驗板上驗證所設計系統的邏輯功能。

4、利用EDA技術進行陣列乘法器設計的實例

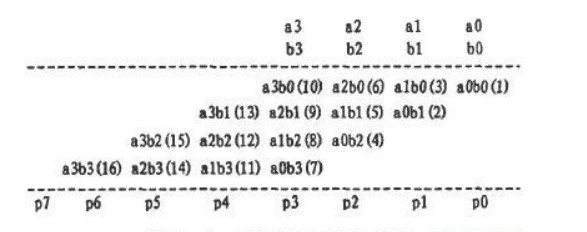

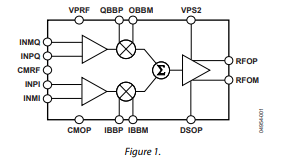

實驗要求用ispIS11032芯片來實現一個4x4位乘法器。4x4位乘法器設計原理見圖1。

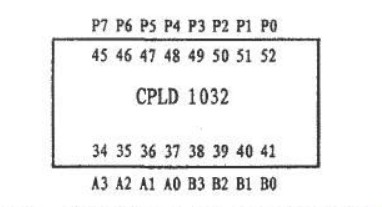

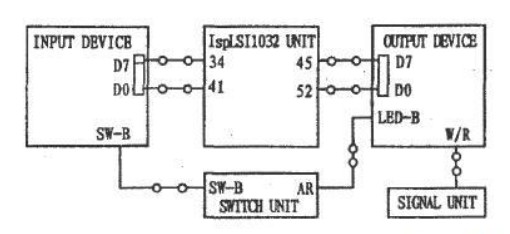

根據上述乘法的邏輯原理用ABEL語言編寫功能描述程序。其在ispISI1032芯片中對應的管腳安排如圖2所示,驗證實驗連線圖如圖3所示。

5、結束語

與以往傳統的實驗方法相比,學生在實驗過程中可以把重點放在模型計算機的設計和仿真驗,使本課程的實踐教學環節更好地達到教學目的。軟件設計調試階段完成后的硬件下載和測試,又使學生能夠學習硬件環境下的調試方法。實踐表明,新的實驗模式激發了學生學習的積極性,加深了對本課程的掌握程度,同時還能夠學到先進的設計技術,學生普遍歡迎這種改革。新的實驗模式有效地鍛煉了學生的設計能力和實踐能力,為學生提供了充分的創造空間,收到了傳統實驗方法難以獲得的效果。

責任編輯:tzh

-

芯片

+關注

關注

459文章

52425瀏覽量

439679 -

計算機

+關注

關注

19文章

7653瀏覽量

90633 -

eda

+關注

關注

71文章

2918瀏覽量

177677

發布評論請先 登錄

MAX2046高增益矢量乘法器技術手冊

ADL5390 RF矢量乘法器技術手冊

ADA-28F00WG乘法器Marki

求助,LMX2572LP參考時鐘路徑中的乘法器MULT的輸入頻率范圍問題求解

請問如何用VCA810實現模擬乘法器?

CDCF5801A具有延遲控制和相位對準的時鐘乘法器數據表

CDCS503帶可選SSC的時鐘緩沖器/時鐘乘法器數據表

CDCE706可編程3-PLL時鐘合成器/乘法器/分頻器數據表

利用EDA技術進行陣列乘法器設計的實例

利用EDA技術進行陣列乘法器設計的實例

評論