抗干擾問題是現代電路設計中一個很重要的環節,它直接反映了整個系統的性能和工作的可靠性。對PCB工程師來說,抗干擾設計是大家必須要掌握的重點和難點。

PCB板中干擾的存在

在實際研究中發現,PCB板的設計主要有四方面的干擾存在:電源噪聲、傳輸線干擾、耦合和電磁干擾(EMI)。

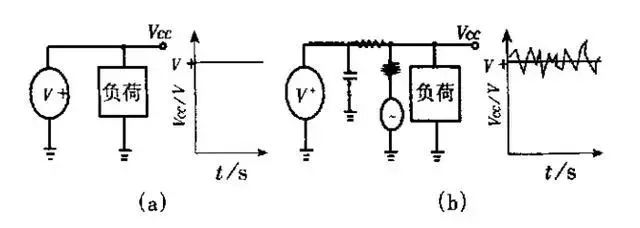

1、電源噪聲

高頻電路中,電源所帶有的噪聲對高頻信號影響尤為明顯。因此,首先要求電源是低噪聲的。在這里,干凈的地和干凈的電源同樣重要。

2、傳輸線

在PCB中只可能出現兩種傳輸線:帶狀線和微波線。傳輸線最大的問題就是反射,反射會引發出很多問題,例如負載信號將是原信號與回波信號的疊加,增加信號分析的難度;反射會引起回波損耗(回損),其對信號產生的影響與加性噪聲干擾產生的影響同樣嚴重。

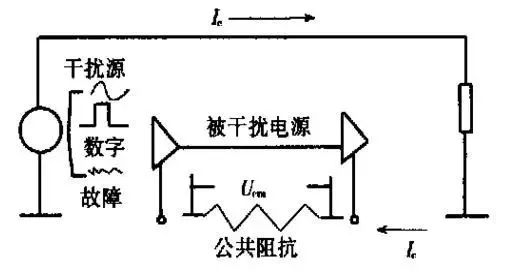

3、耦合

干擾源產生的干擾信號是通過一定的耦合通道對電控系統發生電磁干擾作用的。干擾的耦合方式無非是通過導線、空間、公共線等作用在電控系統上。分析下來主要有以下幾種:直接耦合、公共阻抗耦合、電容耦合、電磁感應耦合、輻射耦合等。

4、電磁干擾(EMI)

PCB及電路抗干擾措施

印制電路板的抗干擾設計與具體電路有著密切的關系,接下來,我們僅就PCB抗干擾設計的幾項常用措施做一些說明。

1、電源線設計

根據印制線路板電流的大小,盡量加粗電源線寬度,減少環路電阻。同時、使電源線、地線的走向和數據傳遞的方向一致,這樣有助于增強抗噪聲能力。

2、地線設計

數字地與模擬地分開。若線路板上既有邏輯電路又有線性電路,應使它們盡量分開。低頻電路的地應盡量采用單點并聯接地,實際布線有困難時可部分串聯后再并聯接地。高頻電路宜采用多點串聯接地,地線應短而粗,高頻元件周圍盡量用柵格狀大面積地箔。

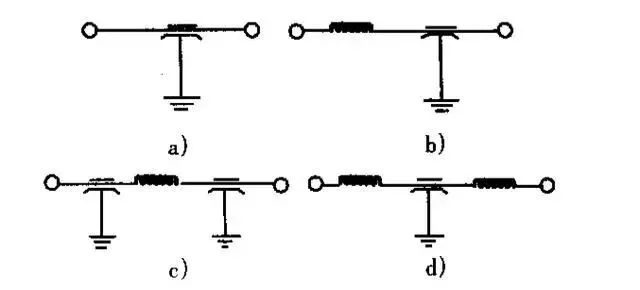

3、退耦電容配置

PCB設計的常規做法之一是在印制板的各個關鍵部位配置適當的退耦電容。

退耦電容的一般配置原則是:

①電源輸入端跨接10 ~100uf的電解電容器。如有可能,接100uF以上的更好。

②原則上每個集成電路芯片都應布置一個0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個芯片布置一個1 ~ 10pF的電容。

③對于抗噪能力弱、關斷時電源變化大的器件,如 RAM、ROM存儲器件,應在芯片的電源線和地線之間直接接入退耦電容。

④電容引線不能太長,尤其是高頻旁路電容不能有引線。

4、PCB設計中消除電磁干擾的方法

-

PCB設計

+關注

關注

396文章

4800瀏覽量

90307 -

干擾

+關注

關注

0文章

214瀏覽量

27747

原文標題:怎樣進行PCB電路板的抗干擾設計?

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何規劃PCB電路板降低干擾

如何規劃PCB電路板降低干擾

評論