Ultra 96 介紹

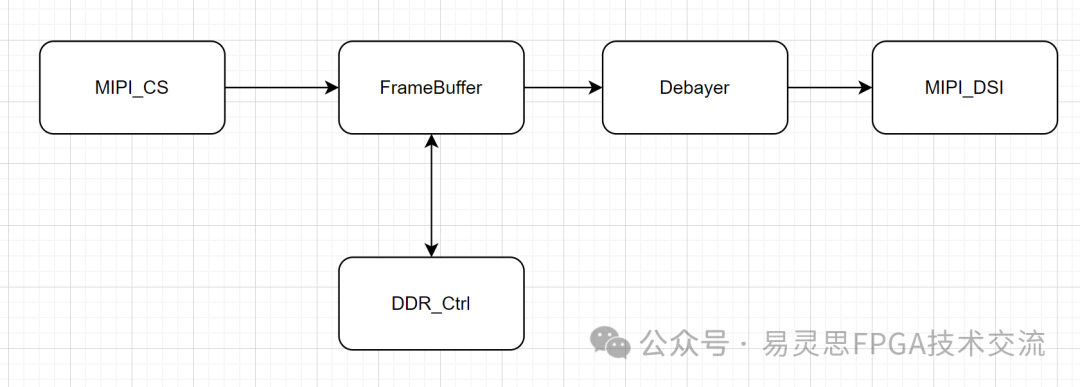

Ultra 96 是構建邊緣用例機器學習應用的絕佳平臺。Zynq MPSoC ZU3 器件采用的 96 電路板的外形尺寸以及可編程邏輯使其能夠靈活地添加用于此類終端應用的視頻輸入的通用 MIPI CSI2 RX 標準接口,同時為了驅動高性能、低功耗機器學習邊緣應用,也可以將賽靈思深度學習處理單元 (DPU) 集成到設計中。由于眾多首次采用賽靈思 Vitis 統一軟件平臺流的用戶將從現有的基于 Vivavdo 的設計入手,因此我們會從如何將 Vivado IPI 中實現的傳統設計轉換為可加速的 Vitis 目標平臺來開始我們的教程。本設計中的 MIPI 流水線利用 Ultra96 常見的 96Boards 外形尺寸,在 MIPI 成像夾層卡上使用 OV5640 成像傳感器,并使用 YUYV 輸出類型從 MIPI RX IP 直接輸入幀緩沖寫入 DMA 內核,然后輸入到 PS DDR。接下來,我們將演示更新 PetaLinux 項目的步驟,以包含必要的庫和驅動程序,從而創建能夠支持硬件加速工作流的 Vitis 軟件平臺,其中包括基于 DPU 的機器學習應用。一旦完成軟硬件平臺組件,我們將使用 Vitis 開發套件將它們組合成 Vitis 加速平臺,然后我們就可以借助該平臺構建硬件加速的軟件應用。最后,我們將介紹賽靈思深度學習處理單元 (DPU) 在機器學習加速應用中的集成。在添加 DPU 之后,我們可以使用所提供的 DPU 運行時來評估高性能人臉檢測應用,該應用使用來自生成平臺的流式 MIPI 輸入。

01設計要求

本節列出了使用賽靈思深度學習處理單元 (DPU) IP 加速機器學習算法所需的軟硬件工具。

賽靈思設計工具 2019.2

Ultra96 v1 板文件

Ultra96 電路板 (v1)

Ultra96 12V 電源

MicroUSB 轉 USB-A 線纜

AES-ACC-USB-JTAG 電路板

一張使用 FAT32 文件系統格式化的空白 microSD 卡

賽靈思 CSI2 RX MIPI IP 許可證

D3 Engineering Designcore 攝像頭夾層電路板 OV5640(MIPI 輸入源)

可選項

DisplayPort 監控器

適用于所選監控器的微型顯示端口線纜

USB 網絡攝像頭

02準備工作空間

將該數據庫復制到您的本地計算機上,并下載參考文件目錄。在下載完參考文件之后,將它們解壓縮到剛才復制的數據庫的參考文件目錄中。該層級中的其余文件夾將在下載完成后變成空白,并將在整個教程中進行補充。

03生成 MIPI 基礎項目

首先,我們將在 Vivado 和 Petalinux 工具中創建原始的非加速 MIPI 項目。在完成這一步驟之后,您將得到可啟動軟硬件鏡像,用來啟動流水線,從而查看來自 Ultra96 的輸入 MIPI 視頻。

Vivado

將“腳本”文件夾從[reference_files/base_project/vivado]目錄復制到頂層 vivado 目錄

啟動 Vivado,并在頂層“vivado”目錄中創建一個名為“u96v1_mipi”的新項目,確保選擇“創建項目子目錄”選項,然后單擊“下一步”

選擇創建“RTL 項目”,然后單擊“下一步”

選擇“添加文件”,從[reference_files/base_project/vivado/sources]目錄中選擇“U96v1_mipi_wrapper.v”文件,單擊“下一步”

選擇“添加文件”,從[reference_files/base_project/vivado/sources]目錄中選擇“cnst.xdc”文件,然后單擊“下一步”

選擇“電路板”選項卡并選擇項目的 Ultra96 V1 電路板,然后選擇“下一步”和“完成”創建項目

在屏幕底部的“TCL 控制臺”選項卡中,將目錄更改為頂層“vivado”目錄

使用 TCL 控制臺調用資源./scripts/u96v1_mipi_static.tcl

在“流導航器”窗口中選擇“生成塊設計”并允許完成此操作

將項目構建為比特流

選擇“文件 > 導出 > 導出硬件”并將硬件導出到 hw_platform 頂層目錄,包括比特流

PetaLinux

獲取 Petalinux 工具

將目錄更改為頂層目錄,并使用以下命令創建一個新的 petalinux 項目:petalinux-create –t project –n petalinux –sreference_files/base_project/bsps/u96v1_mipi_static.bsp

將目錄更改為新目錄

運行 petalinux-config --get-hw-description ../hw_platform --silentconfig 導入生成的硬件

閱讀petalinux-config -c rootfsandpetalinux-config -c kernel菜單,查看為了在 Ultra96 上包含 MIPI 進行了哪些定制

運行petalinux-buildto build the system

運行 petalinux-package --boot --force --fsbl --pmufw --u-boot --fpga 創建 BOOT.bin

將 BOOT.bin 和 image.ub 從[petalinux/images/linux]目錄復制到 SD 卡,并使用它來啟動系統

[在此處輸入 GStreamer 命令測試視頻輸入]

04創建 Vitis 硬件平臺

現在,我們將對硬件設計進行必要的添加和修改,以便為軟件定義加速設計做好準備:打開 Vivado 基礎項目開始。

05配置 MPSoC 塊

當我們在硬件設計中添加其他組件以滿足加速要求時,需要對處理子系統進行定制。在這里,我們將修改配置以創建附加時鐘、打開額外的中斷端口,并創建 AXI 主端口,以便在設計中添加其他外設。

雙擊 Zynq IP 塊,打開處理器配置向導 (PCW)

轉到“時鐘配置”選項卡,選擇“輸出時鐘”選項卡,展開低功耗域時鐘 > PL 架構時鐘

啟用 PL1,并將兩個時鐘的請求頻率更改為 100MHz,選擇 IOPLL 作為源時鐘

進入“PS-PL 配置”選項卡,展開通用 > 架構重置,然后啟用第二次架構重置

添加另一個 AXI 主端口,稍后我們將使用它來連接中斷控制器 - 單擊 PS-PL 接口 > 主接口,并啟用 AXI HPM0 LPD

展開通用 > 中斷 > PS-PL

啟用 IRQ1[0-7]

單擊“確定”離開 PCW

06配置平臺接口

為了讓 Vitis 工具將硬件加速塊插入到設計中,我們需要保持打開狀態,并為它指定可以用來連接塊的接口。在本設計中,我們需要一些存儲器映射接口,以便 DPU 可以連接到 PS DDR。在這個平臺上我們將打開三個 HP 從端口,因為在 DPU 塊上有三個存儲器映射的主端口。此外,這部分流程還支持我們“命名”端口,給它起一個更短的昵稱,以便以后指定連接。

在“窗口”菜單中,選擇“平臺接口”

在“平臺接口”選項卡中,單擊“啟用平臺接口”

右鍵單擊接口并選擇“啟用”(HP 0、1、2),添加三個尚未使用的 PS HPx_FPD 從設備

同時,啟用 HPM0 主設備接口 - 確保在 Zynq PS 塊上禁用此接口。工具將使用這一主設備連接到加速器

對于每個已啟用的從設備接口,在“選項”選項卡中添加一個“sptag”值,該值將在稍后的流中引用該端口:分別為 HP0、HP1 和 HP2

07指定“平臺”時鐘

類似于為平臺指定接口的方式,現在我們必須向工具指示它應該為平臺中的加速器使用哪些時鐘。在這種情況下,DPU 使用兩個時鐘(1x 和 2x 時鐘)。因此,我們將向平臺指示 250MHz 和 500MHz 時鐘。DPU 時鐘頻率可以快于或慢于該速率,選擇該速率是為了平衡應用中的功耗和幀速率性能。

右鍵單擊塊設計,選擇“添加 IP”,然后添加時鐘向導 IP

將實例名稱更改為 clk_wiz_dynamic

雙擊 clk_wiz_dynamic IP,并在“輸出時鐘”選項卡中進行以下更改:[clk_out1=250MHz],[clk_out2=500MHz],[兩者路由匹配],[重置類型 = 低電平有效]

將原始時鐘向導 (clk_wiz_static) 從 pl clk0 移動到 pl clk1

在“平臺接口”選項卡中,啟用 clk_wiz_dynamic 實例的 clk_out1 和 clk_out2

將較慢的時鐘(本例中為 clk_out1)設置為默認值

clk_out1 的 id 應設置為 0、clk_out2 的 id 應設置為 1

確保將每個窗口中列出的 proc_sys_reset 塊均設置為連接到該時鐘的實例

08分離原始組件

在本設計中,我們選擇將原始組件(MIPI 子系統)放置在來自 PS 的獨立時鐘上。將加速器的時鐘向導和處理器系統重置連接到 PL0 時鐘,MIPI 子系統連接到 PL1 時鐘。這有助于我們確保原始組件或加速組件時鐘頻率(或時鐘門控)的任何更改都不會影響其他組件的運行。

右鍵單擊 pl_clk0 并在菜單中選擇“斷開引腳連接”

將 pl_clk0 連接到 clk_wiz_dynamic clk_in1,并將 pl_clk1 連接到 clk_wiz_static 的 clk_in1

刪除連接到 pl_reset0 的網絡

右鍵單擊塊設計,選擇“添加 IP”,并為每個新時鐘添加處理器系統重置 IP。

將它們命名為 proc_sys_reset_dynamic_1 和 proc_sys_reset_dynamic_2

將 clk_wizard_dynamic 塊的 clk_out1 和 clk_out2 輸出分別連接到 proc_sys_reset_dynamic_1 和 proc_sys_reset_dynamic_2 slowest_sync_clk 輸入

將 PS pl_reset0 連接到兩個新處理器系統重置塊的 ext_reset_in 輸入

將 pl_reset0 連接到 clk_wiz_dynamic 的重置端口

將 pl_reset1 連接到 clk_wiz_static 的重置端口和 proc_sys_reset_200 的 ext_reset_in 引腳

將 clk_wiz_dynamic 鎖定輸出連接到兩個新處理器系統重置塊的 dcm_locked 輸入

09啟用基于中斷的內核

加速內核的默認調度模式為輪詢模式。為了在平臺中啟用基于中斷的處理,我們需要添加中斷控制器。在當前設計中,我們需要將常量 “gnd”連接到中斷控制器,此時不連接任何有效的中斷源。與 AXI 中斷控制器配對的是 Vivado 源代碼中的“dynamic_postlink”tcl 腳本,它將選擇中斷常數網絡,將其與連接塊斷開,然后通過 Vitis 工具添加加速內核后自動連接。

右鍵單擊塊設計,選擇“添加 IP”,添加 AXI 中斷控制器

在中斷控制器的塊屬性中,將名稱設置為 axi_intc_dynamic

添加“連接”IP,將輸入連接到中斷控制器中

在“連接”塊的塊屬性中,將名稱設置為 int_concat_dynamic

雙擊“連接”塊,將端口數修改為 8

添加“常量”IP,為中斷控制器提供一個常量“0”- 這個常量會在編譯時由工具斷開連接并被加速中斷連接所取代

雙擊“常量”IP,并將常量值修改為 0

單擊設計輔助欄中的“運行連接自動化”鏈接,連接 AXI 中斷控制器的從 AXI 接口 - 選擇 HPM0_LPD,因為 HPM1_FPD 用于視頻子系統。

將中斷控制器的所有輸入連接到“連接”塊輸出

將“連接”塊的輸出連接到中斷控制器的 intr 輸入

將中斷控制器的輸出連接到 PS 塊上的 pl_ps_irq1

選擇常量塊的輸出網絡,并將其命名為 int_const_net

10生成設計和 XSA

目前,我們已經對該設計進行了定制,可以通過賽靈思支持存檔 (XSA) 將其導出到 Vitis 工具中。請注意:我們不會將這個項目構建為比特流。Vitis 工具將利用這一存檔來導入設計,在硬件加速器中進行合成,然后,它將構建比特流。使用 dsa.tcl 腳本自動化這部分流程 - 在將賽靈思支持存檔 (XSA) 文件導出到 hw_platform 目錄之前,會自動化命名和平臺詳細信息。此外,該腳本還鏈接了前面提到的 dynamic_postlink.tcl 腳本,以便將特定于該平臺的腳本包含在存檔文件中。

生成塊設計

通過運行source ./scripts/dsa.tcl 導出硬件平臺

11創建軟件平臺

軟件平臺要求對 Petalinux 項目進行一些更改,需要將必要的賽靈思運行時 (XRT)組件添加到設計中。此時,提供兩個選項:按照以下所有步驟復制必要的文件并在 Petalinux 中啟用這些組件,或者跳過 1-8,用[reference_files/platform_project/bsps/u96v1_mipi_dynamic.bsp] 處的 u96v1_mipi_dynamic.bsp 中的新項目替換 Petalinux 項目。

12添加賽靈思運行時程序

創建加速平臺的第一步是添加上面提到的庫組件:賽靈思運行時和 DPU 運行時 (dnndk)。它們以程序的形式出現,我們將把它們添加到 Petalinux 構建中的用戶層中。首先,復制文件并構建程序,然后通過 Petalinux 根文件系統配置菜單啟用它們。

將目錄更改為 Petalinux 目錄

添加程序,從而將 DPU 實用工具、庫和頭文件添加到根文件系統中

cp -rp ../reference_files/platform_project/plnx/recipes-apps/dnndk project-spec/meta-user/recipes-apps

添加程序以添加賽靈思運行時 (XRT) 驅動程序

cp -rp ../reference_files/platform_project/plnx/recipes-xrt project-spec/meta-user

添加程序創建插件,用于添加在 Linux 啟動期間自動運行的“自動啟動”腳本

cp -rp ../reference_files/platform_project/plnx/recipes-apps/autostart project-spec/meta-user/recipes-apps

將上面的程序添加到 Petalinux 映像配置

vi

project-spec/meta-user/recipes-core/images/petalinux-image-full.bbap

pend

并將其添加到文檔的末尾:

IMAGE_INSTALL_append = " dnndk"

IMAGE_INSTALL_append = " autostart"

IMAGE_INSTALL_append = " opencl-headers"

IMAGE_INSTALL_append = " ocl-icd"

IMAGE_INSTALL_append = " xrt"

IMAGE_INSTALL_append = " xrt-dev"

IMAGE_INSTALL_append = " zocl"

使用從 Vivado 導出的新 XSA 更新 Petalinux 項目

petalinux-config --get-hw-description=../hw_platform --silentconfig

打開 Petalinux 根文件系統配置 GUI 以啟用上面的程序

petalinux-config -c rootfs

然后在“用戶包”子菜單中啟用上面的所有程序

13修改 Linux 器件樹

需要修改 Linux 器件樹,以便正確探測賽靈思運行時內核驅動程序。修改[project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi],將 Zynq OpenCL 節點添加到器件樹。

在 project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi 的底部,添加以下文本:

&amba {

zyxclmm_drm: zyxclmm_drm@0xA0000000 {

reg = <0x0 0xA0000000 0x0 0x800000>;

compatible = "xlnx,zocl";

status = "okay";

interrupt-parent = <&axi_intc_dynamic>;

interrupts = <0 1>, <1 1>, <2 1>, <3 1>,

<4 1>, <5 1>, <6 1>, <7 1>;

};

};

14構建 Petalinux 并打包軟件組件

目前,我們已經為 Petalinux 構建完成了所有必要的配置更改,可以開始構建。這可能需要相當長的時間,但考慮到計算機的處理能力,也可能需要很短的時間。Linux 構建完成后,我們需要將所有構建的軟件組件移動到一個公共目錄中。通過將所有啟動組件放在一個目錄中,在硬件和軟件側打包到結果平臺中時,會變得很容易。此外,我們還將使用 Petalinux 構建 sysroot,以便為該軟件平臺提供完整的交叉編譯環境。這個 sysroot 也將包含在平臺的軟件部分中,因為在為平臺編譯時,需要它來提供正確版本的頭文件/包含文件。

構建 Petalinux

petalinux-build

將所有 .elf 文件從[petalinux/images/linux]目錄復制到[SW_Platform/boot],此操作應復制以下文件:

o ARM可信固件 - b131.elf

o PMU 固件 – pmufw.elf

o U-Boot – u-boot.elf

o Zynq FSBL – zynqmp_fsbl.elf

將 image.ub 文件從[petalinux/images/linux]目錄復制到[SW_Platform/image]

將 linux.bif 文件從[reference_files/platform_project/plnx]目錄復制到[sw_platform/boot]

從項目petalinux-build --sdk 構建 Yocto SDK(提供 sysroot)

將[images/linux/sdk.sh]移動到[SW_Platform/sysroot],然后提取 SDK cd sw_platform/sysroot ./sdk.sh -d ./-y

15生成 Vitis 軟件平臺

Vitis 軟件平臺是一套組件,包括啟動和開發特定電路板/電路板配置所需的所有內容,且包含硬件和軟件組件。目前,我們已經為平臺構建了硬件 (XSA) 和軟件(Linux 鏡像和啟動 elf 文件)組件,我們可以使用這些組件來生成和導出用戶定義的定制平臺。我們將在賽靈思 Vitis 開發套件中介紹這些步驟。

打開 Vitis IDE,選擇頂層工作空間目錄作為工作空間

選擇“文件”、“新建”和“平臺項目”

將平臺命名為“u96v1_mipi”

選擇從硬件規格創建,然后在[hw_platform]中選擇 XSA

選擇 Linux 操作系統和 psu_cortexa53

雙擊文件導航器中的 platform.spr 打開項目

自定義“linux on psu_cortexa53”域以指向[sw_platform/boot]中的啟動組件和 bif

自定義“linux on psu_cortexa53”域以指向[sw_platform/image]中的鏡像目錄

點擊“錘子”圖標或“生成平臺”按鈕,從平臺項目生成輸出產品

目前,平臺已經生成,請注意,這里有一個“導出”目錄。這個導出目錄是完整的生成平臺,可以壓縮和共享 - 提供組件,使新的開發者能夠在自定義平臺上進行操作。

16創建人臉檢測應用項目

對于最終應用,我們可以將 MIPI 平臺定位于機器學習應用。使用預先生成的賽靈思深度學習處理器單元 (DPU) 作為加速內核,并使用賽靈思 Vitis IDE 將該內核編譯到平臺中,然后構建調用該硬件的用戶空間應用來運行自定義人臉檢測應用。

17創建新的應用項目

從創建新的應用項目開始。在 Vitis 工具中,應用項目保存在系統項目容器中,以便在平臺中跨各個啟用域(例如:A53 和 R5)為內聚系統開發提供方法。由于我們在與之前相同的工作空間內開展工作,所以可以輕松地將目標鎖定在之前生成的平臺上 - 但是您也可以通過單擊“+”按鈕并指向“平臺選擇”對話框中包含 xpfm 的目錄來添加其他平臺數據庫。

打開 Vitis IDE,選擇頂層工作空間目錄作為工作空間

選擇“文件”、“新建”和“應用項目”

將項目命名為“face_detection”,并使用自動生成的系統項目名稱

選擇剛剛創建的“u96v1_mipi”平臺

確認在下一個界面中選擇了 Linux 域,然后指向在 sw_platform 中生成的 sysroot

選擇“空應用”作為模板,然后單擊“完成”

18編輯生成設置

右鍵單擊文件導航器中的[face_detection/src],選擇“導入”

選擇“通用”和“文件系統”

使用[reference_files/application]作為目標位置,并導入所有這些文件

右鍵單擊文件導航器中的“face_detection”并選擇“C/C++ 生成設置”

如果您不在 C/C++ 生成設置菜單中,請導航到該菜單

對于配置,選擇“所有配置”

在下面的“GCC 主機鏈接器、庫”子菜單中,單擊綠色“+”添加以下庫:

- n2cube

- dputils

- opencv_core

- opencv_imgcodecs

- opencv_highgui

- opencv_imgproc

- opencv_videoio

在“主機鏈接器”、“其他項”、“其他對象”子菜單中,從 workspace./src 位置添加 dpu_densebox.elf

在主機編譯器的“包含”部分,選擇 XILINX_VIVADO_HLS 的包含路徑,然后單擊紅色“X”進行刪除

單擊“應用”和“關閉”

19添加 DPU 作為硬件加速器

最后,我們將 DPU 添加進來作為硬件加速內核,并使用 Vitis 進行連接和編譯設計。

雙擊 face_detection 項目下的 project.sdx 打開項目視圖

在硬件功能下,單擊“閃電”標志添加新加速器

選擇我們在之前添加的 dpu.xo 文件中包含的“dpu_xrt_top

單擊 binary_container_1 將名稱更改為 dpu

右鍵單擊“dpu”,選擇“編輯 V++”選項

添加--config ../src/connections.ini指定將 DPU 的哪個端口連接到前面所創建的平臺接口

在右上角,將活動構建更改為“系統”

單擊“錘子”圖標構建項目

這可能需要大約 30 分鐘或更長時間,具體取決于您用來完成構建的計算機。您可能已經注意到,我們從未將設計的硬件部分用于比特流生成。在運行時,該工具在硬件設計中使用“開放”接口,將 DPU 導入到設計中,然后連接這些接口以匹配“connections.ini”中調用的內容。在完成設計和新組件之后,將運行綜合和實現來生成二進制文件并加載到架構中。

20在 Ultra96 上運行應用

在完成構建流程之后,您將在項目的系統目錄下找到補充的 sd_card 文件夾。將 sd_card 鏡像復制到格式化的 SD 卡以啟動電路板。電路板成功啟動后,您可以遵循幾個快速步驟來運行設計。

在電路板上,將目錄更改為[/run/media/mmcblktab/]

將 dpu.xclbin 文件復制到 /usr/lib

運行 face_detection.elf

不帶參數運行時,face_detection 應用會提供輔助對話框,其中包含通過應用的示例流水線(mipi、網絡攝像頭、UDP 流)。這些都是在類似 gstreamer 的散熱器中提供給應用的,以提供對人臉檢測應用的輕松定制。

示例流水線:

"./face_detection -i /dev/video0 -o autovideosink" will display over x11 forwarding or on local monitor

"./face_detection -i /dev/video0 -o udpsink host=192.168.1.50 port=8080" will stream over UDP

-

電路板

+關注

關注

140文章

5130瀏覽量

102560 -

機器學習

+關注

關注

66文章

8501瀏覽量

134565 -

深度學習

+關注

關注

73文章

5561瀏覽量

122778

原文標題:采用 Vitis 技術的 Ultra96 (v1):DPU 集成與 MIPI 平臺教程

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用AMD Vitis Unified IDE創建HLS組件

DPU232—高度集成USB到UART橋接控制器 國產替代方案

MIPI2.5G DPHY CSI2DSI demo移植 -v1

采用Vitis技術的Ultra96 (v1):DPU集成與MIPI平臺教程

采用Vitis技術的Ultra96 (v1):DPU集成與MIPI平臺教程

評論