EDA 是芯片之母是IC 設(shè)計(jì)最上游、最高端的產(chǎn)業(yè)。也是中國(guó)集成電路產(chǎn)業(yè)最薄弱的環(huán)節(jié)。為向集成電路專(zhuān)業(yè)師生和從業(yè)者中系統(tǒng)介紹EDA技術(shù)的前沿進(jìn)展,芯人類(lèi)將分多期全文引入《電子報(bào)》EDA前沿技術(shù)專(zhuān)欄。專(zhuān)欄特邀行業(yè)多位專(zhuān)家,全面系統(tǒng)地介紹國(guó)內(nèi)外EDA 的狀況和國(guó)產(chǎn)EDA 的發(fā)展。本文為電子報(bào)授權(quán)發(fā)表。包含混合SOC的設(shè)計(jì),驗(yàn)證和實(shí)現(xiàn)的方法流程三方面內(nèi)容,并重點(diǎn)介紹了驗(yàn)證所需要了解的仿真器原理,和行為級(jí)建模相關(guān)的知識(shí)。共分三次發(fā)表。

Table Model

有點(diǎn)類(lèi)似于大數(shù)據(jù)的概念。既然傳統(tǒng)的Model和硅工藝聯(lián)系不怎么緊了,那么直接把Silicon測(cè)試出來(lái)的數(shù)據(jù)都列舉出來(lái),建立一個(gè)數(shù)據(jù)庫(kù)(溫度、電壓和Silicon數(shù)值)表格,仿真器用的時(shí)候直接查表就行了。你只要關(guān)心輸入什么值,能輸出來(lái)什么值就行了,一表在手,有input有output。

放棄對(duì)因果關(guān)系的過(guò)分渴求,取而代之去關(guān)注“相關(guān)關(guān)系”,只是根據(jù)實(shí)際測(cè)試到的silicon的數(shù)值,直接做一個(gè)數(shù)據(jù)庫(kù),當(dāng)外界加什么電壓、有什么溫度時(shí)候,就來(lái)什么對(duì)應(yīng)的輸出電流等。這就類(lèi)似于大數(shù)據(jù)的概念,不關(guān)心為什么,只在乎是什么。對(duì)于不在table里面的數(shù)據(jù),仿真器需要插入數(shù)值(interpolate)或者外推推斷數(shù)值(extrapolate)。短板是離散數(shù)據(jù)的連續(xù)性和光滑性差,需要Analog仿真器做些處理。

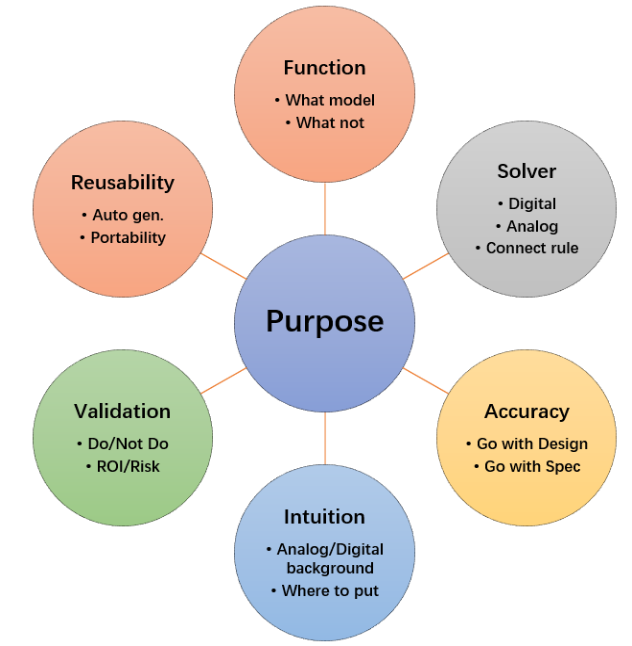

建模前要plan!Plan!plan!

在做Model之前,一定要想清楚做Model的目的是什么。

建模需要考慮的因素

Model是否需要統(tǒng)一的規(guī)范?因?yàn)轵?yàn)證本身希望能夠Reuse。但是一旦想統(tǒng)一規(guī)范,可能就需要花費(fèi)更長(zhǎng)的時(shí)間和精力,項(xiàng)目是否有時(shí)間/值得付出不?哪些Model不要是需要放棄建模的?例如對(duì)于非線性(Non-linear)的因素, 是否可以轉(zhuǎn)化為線性。對(duì)于弱相關(guān)因子(weak dependencies)是否可以忽略;如果進(jìn)入一個(gè)Model的input control/signal不符合Model里面的預(yù)期,需要有Assertion來(lái)要報(bào)錯(cuò)。

Model到底是讓Analog Background的人來(lái)寫(xiě)?還是Digital的工程師?放在電路的哪個(gè)層級(jí)?

對(duì)于Model要不要做Validation?怎么做Validation?對(duì)Model的驗(yàn)證,包括利用相同的Test Bench,對(duì)于Model和Schematic出來(lái)的結(jié)果的驗(yàn)證。驗(yàn)證Model和電路類(lèi)似,有Block級(jí)Schematic和Model的吻合,還有Sub-System能夠能通暢的利用Model仿真、以及Model和Sub-System的吻合,更有Model和整個(gè)Top的吻合度。為了提高項(xiàng)目效率,是不是可以跳過(guò)某些層級(jí)?

總之就是做Model也是一門(mén)藝術(shù),需要在服務(wù)其目的的情況下,做各種trade off。

與Model相關(guān)的工具

SMG-1

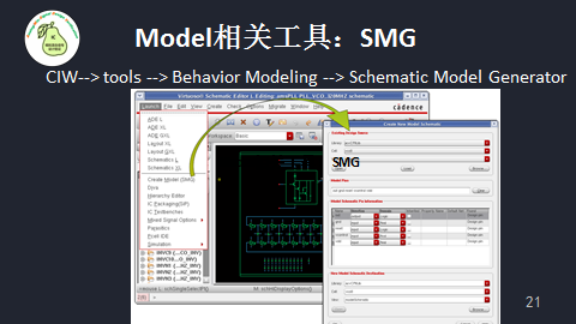

A、SMG

Schematic Model Generator的工具在Virtuoso里面,只要用圖形的界面填寫(xiě)一下pin的性質(zhì),IO代碼就自動(dòng)生成。

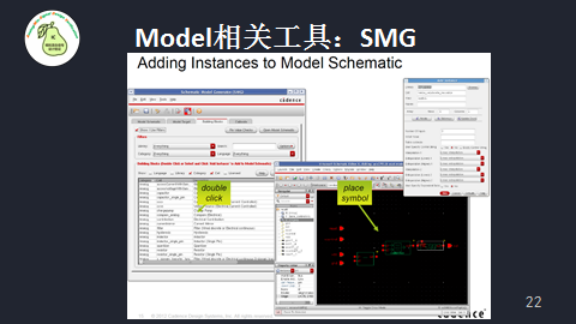

SMG-2

很多內(nèi)置的小模塊BBT(Building Block Text),提供了例示的code,你根據(jù)自己的schematic,去搭建設(shè)計(jì)。

在Model自動(dòng)化的道路上,設(shè)計(jì)者和EDA工具開(kāi)發(fā)者需要進(jìn)一步努力,例如電路設(shè)計(jì)時(shí)候的合理Partition,和考慮標(biāo)準(zhǔn)化Model的電路分層等。

SMG-3

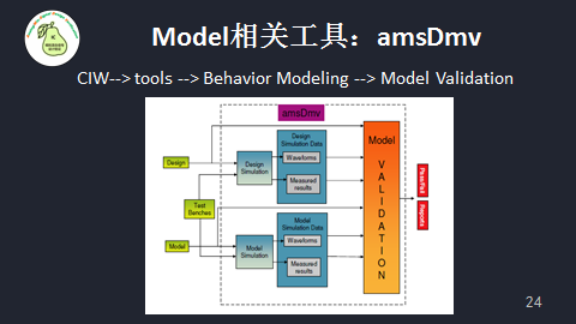

B、amsDmv

Model要和Schematic吻合,amsDmv(AMS Design and Model Validation)提供Model的驗(yàn)證功能。

amsDmv

它利用ADE的結(jié)果按一定的誤差精度(Tolerance),對(duì)比schematic和Model仿真的波形,也可以做最基本的Pin check,以及設(shè)置不需要對(duì)比的參數(shù)(exclude)等信息。

C、Xmodel

有一個(gè)xmodel的工具,集成于Cadence Virtuoso環(huán)境,有Python和Skill的接口,也是方便做Model的小工具,生成SV語(yǔ)言的Model。

數(shù)模混合芯片的物理實(shí)現(xiàn)

物理實(shí)現(xiàn)將電路轉(zhuǎn)換成芯片物理版圖,稱(chēng)之為T(mén)ape Out(TO)。數(shù)字設(shè)計(jì)把相同的節(jié)距和高度標(biāo)準(zhǔn)單元,通過(guò)綜合工具得到門(mén)級(jí)網(wǎng)表,再通過(guò)自動(dòng)布局布線工具(P&R)實(shí)現(xiàn)版圖。模擬設(shè)計(jì)將自動(dòng)生成的參數(shù)化的MOS管搭建Pcell。Pcell搭建模塊,模塊組成定制單元模塊,自動(dòng)鄰接、器件走線、虛擬單元并插入阱單元。模擬版圖一般是定制的。

對(duì)于復(fù)雜的數(shù)模混合SOC,芯片布局至關(guān)重要。在物理實(shí)現(xiàn)的初始要自上而下的大局觀,定制單元和數(shù)字單元同時(shí)考慮。自上而下設(shè)計(jì)中,各模塊的面積和擺放位置需要預(yù)估,信號(hào)流方向和電源布線需要考慮,端口需要優(yōu)化。在自下而上的Layout中,首先實(shí)現(xiàn)包括電阻電容和MOS管的基本器件的版圖,然后在考慮其擺放和連線,從而形成一個(gè)版圖單元;再與其他模塊聯(lián)合。對(duì)于低功耗設(shè)計(jì),由于輸入電源數(shù)目不斷增加,所以需要自上而下設(shè)計(jì)。對(duì)于較小設(shè)計(jì)或者可以復(fù)用的AMS IP,一般用自下而上的流程。當(dāng)然目前越來(lái)越多的在混合使用兩種流程。版圖的IP包括硬模塊和軟模塊兩類(lèi)。

基于約束(Constraints)的方法學(xué),正在用于模擬和數(shù)字物理實(shí)現(xiàn)。約束可以捕捉設(shè)計(jì)者的意圖,并將其傳遞給掩模版工程師,從而知道和驗(yàn)證版圖是否和符合要求。常見(jiàn)模擬約束有:匹配器件,敏感信號(hào)的標(biāo)記和處理,高電壓或高功耗信號(hào),保護(hù)環(huán)和其他隔離結(jié)構(gòu)。數(shù)字IC中,設(shè)計(jì)定義時(shí)序約束,從而進(jìn)行門(mén)級(jí)網(wǎng)表綜合。布線結(jié)束后,會(huì)抽取線上寄生,進(jìn)行靜態(tài)時(shí)序分析STA,來(lái)檢查物理實(shí)現(xiàn)是否符合要求。

物理實(shí)現(xiàn)之后,需要進(jìn)行后仿真。模擬IC常見(jiàn)的抽取方法有只提取電容C,只提取電阻R,電阻電容都提取(RC),電阻電容電感(RCL)提取。數(shù)字IC,將線延遲轉(zhuǎn)換到標(biāo)準(zhǔn)延遲格式(Standard Delay Format)SDF當(dāng)中,從而進(jìn)行后仿真,獲知寄生對(duì)電路性能的影響。

到真正流片之前,還要做設(shè)計(jì)規(guī)則檢查DRC(Design Rule Check);電學(xué)規(guī)則檢查ERC(Electrical Rule Check);版圖對(duì)照電路檢查L(zhǎng)VS(Layout Versus Schematic)來(lái)保證版圖符合電路的連接關(guān)系;和針對(duì)制造的設(shè)計(jì)檢查DFM(Design For Manufacture)來(lái)發(fā)現(xiàn)影響制造質(zhì)量與良率的因素。

電學(xué)特性感知設(shè)計(jì)(Electrically Aware Design)EAD代表了范式轉(zhuǎn)移的方法,將電學(xué)特性分析和驗(yàn)證前饋到設(shè)計(jì)過(guò)程中。

例如,考慮先進(jìn)工藝引入的鄰阱效應(yīng)(Well Proximity Effect, WPE);淺溝隔離效應(yīng)(Shallow Trench Isolation, STI),和電遷移效應(yīng)。為數(shù)模混合驗(yàn)證提供電學(xué)特性感知設(shè)計(jì)的解決方案以及方法學(xué)的優(yōu)化將是一場(chǎng)持久戰(zhàn)。

作者簡(jiǎn)介

邵亞利,模擬混合信號(hào)設(shè)計(jì)驗(yàn)證專(zhuān)家。浙江大學(xué)本碩,“模擬混合信號(hào)設(shè)計(jì)驗(yàn)證”公眾號(hào)(yaliDV)創(chuàng)始人。曾就職于德州儀器(TI),現(xiàn)就職于亞德諾(ADI)半導(dǎo)體公司。ADI(Analog Devices) 是全球領(lǐng)先的高性能模擬技術(shù)公司,憑借杰出的檢測(cè)、測(cè)量、電源、連接和解譯技術(shù),搭建連接現(xiàn)實(shí)模擬世界和數(shù)字世界的智能化橋梁。

責(zé)任編輯:pj

-

芯片

+關(guān)注

關(guān)注

459文章

52192瀏覽量

436246 -

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174442 -

Model

+關(guān)注

關(guān)注

0文章

343瀏覽量

25594

發(fā)布評(píng)論請(qǐng)先 登錄

芯盾時(shí)代中標(biāo)某芯片公司統(tǒng)一身份管理平臺(tái)建設(shè)

PROTUES仿真no model specified for adc0809,誰(shuí)有ADC0809的model?

BLE MESH 智能開(kāi)關(guān)開(kāi)發(fā) 情景模式(睡眠、明亮) 藍(lán)牙model如何分配,如何配置model

華為支付接入規(guī)范

IBIS文件中的Series Model簡(jiǎn)介及設(shè)計(jì)仿真實(shí)例

鴻蒙生態(tài)發(fā)布統(tǒng)一互聯(lián)技術(shù)標(biāo)準(zhǔn)

ov華米聯(lián)手打造OneLink統(tǒng)一鏈接平臺(tái)

LMK04832配置時(shí)鐘輸出時(shí),IDL和ODL怎么配置?有沒(méi)有統(tǒng)一的做法?

知識(shí)分享 | 建模規(guī)范:建立優(yōu)質(zhì)模型的關(guān)鍵

Model是否需要統(tǒng)一的規(guī)范?

Model是否需要統(tǒng)一的規(guī)范?

評(píng)論