我們根據電阻端接的介紹可以知道:我們通過在電路輸出管腳出串聯一個33Ω的電阻。但是我們我們可以觀察到有些電路中的信號,竟然有串聯220Ω,甚至1kΩ。這是為什么呢?首先我們一般在低速的接口看到這樣的設計方法;經常在一些鏈接到背板或者面板的接口見到這樣的設計。

這個電阻很可能是應用于熱插拔的保護。那么這個電阻是如何實現對電路的接口電路進行熱插拔保護的呢?

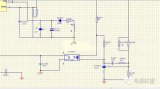

首先我們介紹一下CMOS電路:MOS管有NMOS管和PMOS管兩種。當NMOS管和PMOS管成對出現在電路中,且二者在工作中互補,稱為CMOS管(意為互補)。MOS管有增強型和耗盡型兩種,在數字電路中,多采用增強型。CMOS的等效電路下圖所示,形成一個反相器的功能。

CMOS反相器電路原理

CMOS的結構本質內部就是有很多N型、P型的半導體。在形成了兩個MOS管之外,由于半導體的結構,還產生了一些寄生的三極管。寄生的兩個三極管又組合在一起形成了“n-p-n-p”結構,形成一個。如圖所示,一個集成的CMOS結構半導體的切面圖,我們可以發現有兩個多發射級三極管Q1和Q2生。

CMOS反相器剖面圖

多發射極晶體管就是把多個發射結做在同一個發射區中的晶體管,實際上也就是多個晶體管并聯在一起、但共用一個基區和一個集電區的一種復合晶體管。多發射極晶體管除了能夠提高集成電路的集成度以外,同時還具有其特殊的應用特性。它主要是用于TTL與非(NAND)邏輯IC中,可以提高IC的工作速度。

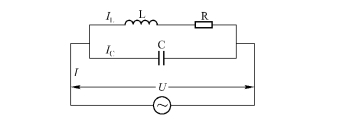

可以把多射級三極管看成是多個三極管并聯,這個電路也不難理解的。我們單獨把寄生電路拎出來,可以得到了一個可控硅的結構。所以很多地方把這個電路稱為寄生SCR(Silicon Controlled Rectifier——可控硅),寄生雙極晶體管等效電路如圖所示。

寄生雙極晶體管等效電路

CMOS反相器在正常工作的情況下,OUT管腳不會出現電壓高于VCC或者低于GND的情況,與OUT相連的PN節不會出現正向導通的情況,器件正常工作。

有些公司的設計文檔中為了便于工程師理解,把寄生雙極晶體管電路等效于兩個二極管。這兩個二極管燒毀時,則器件失效,但其實這個PN結比較難燒毀的。那到底是什么原因導致了器件失效呢?

當熱插拔的時候,由于VCC上電有個過程,非常可能出現器件管腳的電壓先于VCC上電。此時如果出現了OUT電壓導致這兩個PN節導通,進一步導致Q1、Q2兩個三極管打開。PNPN正反饋環路結構,如果A點有觸發電流流過襯底電阻RS1,使得RS1上的壓降UA升高,如果達到晶體管Q1發射結正向導通壓降,就會使T1導通。T1管的集電極電流IC1增大,使得阱電阻RW2上的壓降UB下降;UB的下降使得T2的UBE2增大而導通,IC2增大,結果導致UA繼續增加,如果環路增益大于或等于1,這種狀態將持續下去,直到兩個晶體管完全導通,導通后,CMOS反相器處于閂鎖狀態,其導通電流取決于整個環路的負載及電源電壓。

當Q1、Q2其中任意一個三極管完全導通時,就會構成正反饋,很可能導致器件VCC到GND產生一個很大的電流,過大的電流導致寄生三極管燒毀,導致器件損壞,這個現象就叫做:閂鎖。ESD 和相關的電壓瞬變都會引起閂鎖效應(latch-up),是半導體器件失效的主要原因之一。如果有一個強電場施加在器件結構中的氧化物薄膜上,則該氧化物薄膜就會因介質擊穿而損壞。很細的金屬化跡線會由于大電流而損壞,并會由于浪涌電流造成的過熱而形成開路。這就是所謂的“閂鎖效應”。在閂鎖情況下,器件在電源與地之間形成短路,造成大電流、EOS(電過載)和器件損壞。

要完成這樣的閂鎖效應的觸發,必須具備以下幾個條件:

(1)其PNPN結構的環路電流增益要求大于1,即:βNPN×βPNP≥1。

(2)觸發條件使一個晶體管處于正向偏置,并產生足夠大的集電極電流使另一寄生晶體管也處于正向偏置而導通。

(3) 外來干擾噪聲消失后,只有當電源提供的電流大于寄生可控硅的維持電流或電路工作電壓大于維持電壓時,導通狀態才能繼續維持,否則電路將退出閂鎖狀態。

ESD電壓大,持續時間短,熱插拔電壓小,但是持續時間稍微長點。那么在靜電襲擊電路時,或者熱插拔的時候,非常產生一個產生閂鎖的電壓。如果半導體設計的時候通過半導體結構,可以優化寄生半導體寄生SCR的β值,減少閂鎖產生的概率。從硬件設計的角度,我們可以在一些需要熱插拔、防靜電、防電磁干擾的電流設計中,可以通過串一個電阻來減少閂鎖的產生。但是注意事項就是,這個電阻的阻值不能太大,可能導致上升沿變緩,最終破壞信號完整性。

-

電阻

+關注

關注

87文章

5603瀏覽量

174208 -

電路

+關注

關注

173文章

6022瀏覽量

174327

發布評論請先 登錄

在電路中串聯220Ω電阻的原因

在電路中串聯220Ω電阻的原因

評論