(文章來源:WikiChip Fuse)

據(jù)外媒報道,近日IBM大型商用服務(wù)器z15的物理設(shè)計(physical design)團隊負(fù)責(zé)人Christopher Berry表示,通過對緩存位線、字線、陣列、供電等方面的調(diào)整,他們將z15 SC芯片的總有效緩存密度提高了80%。

2019年下半年,IBM推出了最新的z15大型商用服務(wù)器。z15的SC芯片在制程工藝沒有改變,核心面積沒有增加的情況下,實現(xiàn)了14%的單核性能提升和20%的核心數(shù)量增加,同時,芯片的L2緩存增加33%,L3緩存翻倍,L4緩存增加43%。在2020年2月舉行的ISSCC會議上,z15物理設(shè)計團隊負(fù)責(zé)人Christopher Berry分享了有關(guān)緩存性能優(yōu)化的一些細(xì)節(jié)問題。

z15中單個SC芯片的L4緩存為960 MiB,相比z14增加了43%,L3緩存從128 MiB翻倍至256 MiB,L2緩存也提升到4 MiB。但最值得注意的是,IBM是在保持相同芯片面積和制程工藝的前提下實現(xiàn)了這些性能的提升。與z14一樣,z15采用與格羅方德(GlobalFoundries)共同定制的14納米FinFET on SOI工藝制成。通過該工藝IBM可以生產(chǎn)出超高密度的DTC eDRAM,這也是IBM十幾年來的秘密武器。

該工藝具有超高密度DTC eDRAM。十多年來,eDRAM一直是IBM的秘密武器。即使采用的是14納米工藝,eDRAM的單元尺寸也達到了0.0174μm。目前,臺積電使用尚未量產(chǎn)的5納米工藝所能制成的最密集的SRAM單元,其尺寸為0.021μm 。

這意味著IBM的14納米eDRAM單元的密度比迄今為止最密集的5納米SRAM單元還要高大約20%。IBM物理設(shè)計團隊通過對z14進行改進,使得z15可以在相同面積內(nèi),將位線和字線(bitlines and wordlines)的長度加倍。z14用于L3和L4緩存的原始eDRAM宏塊為1 MiB,由16個子陣列組成。每個子陣列包含128個字線和592個位線。而z15的原始eDRAM宏塊為2MiB,由8個子陣列組成,每個子陣列具有256個字線和1184個位線。

位線加倍會使電容加倍,從而削弱位線信號。為此,設(shè)計團隊降低了nFET閾值電壓,并引入了偏置電路以改善信號值。為了進一步節(jié)省空間,IBM調(diào)整了緩存的電源傳輸網(wǎng)絡(luò)。z14的高壓產(chǎn)生電路是集成在芯片上。而在z15上,他們將這些電路置于片外。

位線和字線的加倍以及子陣列的數(shù)量減半意味著可以在陣列內(nèi)減少相當(dāng)多的I / O接口。團隊預(yù)計這些調(diào)整大約帶來了30%的密度提升,而與供電相關(guān)的變化又使密度提升了約38%。總體而言,物理設(shè)計團隊設(shè)法將總有效緩存密度提高了80%。

(責(zé)任編輯:fqj)

-

IBM

+關(guān)注

關(guān)注

3文章

1821瀏覽量

75801 -

緩存

+關(guān)注

關(guān)注

1文章

246瀏覽量

27168

發(fā)布評論請先 登錄

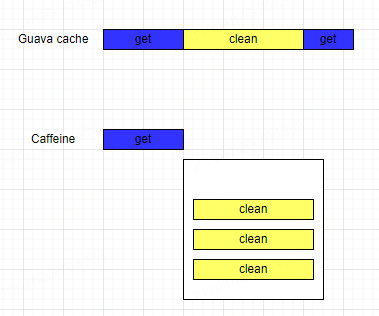

高性能緩存設(shè)計:如何解決緩存偽共享問題

MCU緩存設(shè)計

Nginx緩存配置詳解

廣明源172nm晶圓光清洗方案概述

突破14nm工藝壁壘:天準(zhǔn)科技發(fā)布TB2000晶圓缺陷檢測裝備

HTTP緩存頭的使用 本地緩存與遠程緩存的區(qū)別

藍牙AOA定位系統(tǒng)如何做到高精準(zhǔn)度?

同樣是函數(shù),在C和C++中有什么區(qū)別

兩個高速ADC的CLK時鐘如何做到同步無相位差?

緩存之美——如何選擇合適的本地緩存?

揭秘同樣是14nm,緩存翻倍是如何做到的

揭秘同樣是14nm,緩存翻倍是如何做到的

評論