歷史的魅力在于它給你機(jī)會,也會拖你下馬;它陽光普照,也在光背后隱藏陰影;它包容一切,卻最終只會選擇一個方向。

正如半導(dǎo)體工藝的歷史“圖譜”。目前其最大推動力無疑來自5G SoC大賽,一眾選手明爭暗斗,你方唱罷我出場,潛臺詞都以傲視對手為注解。而不論性能如何膠著,工藝是這些廠商不得不大書特書的依仗。但與一眾對手5nm或7nm相持不同的是,紫光展銳以采用臺積電6nm EUV工藝站上了擂臺賽。6nm藏著什么樣的玄機(jī)?5nm之后的3nm何時實(shí)現(xiàn)?未來的技術(shù)分叉路徑又該如何選擇?

歷史的“比拼”

翻看工藝選手的歷史,到現(xiàn)在已進(jìn)階到“三國殺”的戲碼。

但工藝的賽程已跳脫出最初的“賽道”。一位在業(yè)界耕耘多年的資深前輩衛(wèi)睿對集微網(wǎng)記者指出,在45nm之前,柵級寬度是所有線寬最小的,45nm表示第一層金屬柵級寬度為45nm,有著嚴(yán)格的定義;但到了45nm之后,柵級寬度已不是最小的寬度,業(yè)界拿Mental Pitch即金屬引線之間間隔的一半來定義,因經(jīng)過整個工藝流程,會有偏差,為不造成出入,選取金屬引線之間間隔的一半為工藝級,這樣一直走到20nm。

但之后進(jìn)入了新的分水嶺。“自20nm之后,多少納米則基本變成一個Marketing宣傳的工具,相對之下英特爾比較保守,其10nm相當(dāng)于臺積電和三星的7nm相當(dāng),從中可看出臺積電和三星Marketing的策略比較激進(jìn)。” 衛(wèi)睿如此定調(diào)。

衛(wèi)睿還舉例道,幾年前被問及工藝節(jié)點(diǎn)走向何方時,他的判斷是3nm,但現(xiàn)在據(jù)2nm工藝研發(fā)的指標(biāo)來看都比3nm保守。

因而再來看待6nm已能從容。業(yè)界專家莫大康老師從性價比角度解讀說,臺積電在2019年7nm營收達(dá)94億美元,產(chǎn)能在7萬片,而2020年5nm開始量產(chǎn),目標(biāo)占10%,約35億美元,表明5nm的產(chǎn)能約3萬片。作為客戶,選擇工藝取決于市場,5nm、6nm或7nm價格不同,成品率也肯定不同,相信7nm已經(jīng)成熟,而5nm則剛量產(chǎn),產(chǎn)能緊張,成品率也會低,而采用6nm,可以采用7nm平臺相對容易,讓客戶更多一種選擇。

在集微網(wǎng)此前報道中,臺積電中國區(qū)業(yè)務(wù)發(fā)展副總經(jīng)理陳平就提到,6nm是7nm的延伸和拓展,生態(tài)環(huán)境兼容,設(shè)計(jì)IP也可在6nm上復(fù)用,客戶可更加便捷地導(dǎo)入,在提高產(chǎn)品性能的同時兼顧了成本。據(jù)悉其晶體管密度相比上一代提高了18%,功耗也降低了8%。

而相對于工藝沖鋒向前的“激進(jìn)”,大小節(jié)點(diǎn)的概念也在盛行。“有的節(jié)點(diǎn)是重要的,有的則不重要,比如20nm不重要,16nm是重要的;10nm不重要,7nm重要。原因在于通常兩年升級一個節(jié)點(diǎn),但智能手機(jī)等大宗客戶基本每年都要推新款手機(jī),相應(yīng)地要求手機(jī)芯片每一年采用新節(jié)點(diǎn),畢竟單從數(shù)字來看,采用5nm工藝節(jié)點(diǎn)就顯得比7nm高出一籌。”衛(wèi)睿提出了自己的觀點(diǎn)。因而,那些爭先恐后要比拼先進(jìn)工藝的廠商自然也高舉高打,一起合力向下一節(jié)點(diǎn)沖鋒,各得其所。

3nm的“分野”

無論如何,工藝的“速度與激情”同在上演。

而5nm/3nm已儼然成為代工巨頭的“下一戰(zhàn)”。臺積電為確保7nm、5nm的供應(yīng),正加快設(shè)備購買,設(shè)備廠大受裨益。據(jù)悉臺積電在2020年的投資將達(dá)到150-160億美元,也是臺積電史上最高的資本支出,而80%的開支會用于先進(jìn)產(chǎn)能擴(kuò)增,包括7nm、5nm及3nm,另外20%主要用于先進(jìn)封裝及特殊制程。而其3nm工廠亦計(jì)劃在2020年動工,最快于2022年年底開始量產(chǎn)。

正如衛(wèi)睿所言,5nm之后應(yīng)該是3nm,同為重要節(jié)點(diǎn),而4nm不重要。

“千年老二”三星自然也不斷砸下重金。根據(jù)三星的規(guī)劃,計(jì)劃在未來十年投資1160億美元,其中五百多億美元是投向晶圓制造。2月20日,三星宣布其首條基于EUV技術(shù)的生產(chǎn)線V1已開始大規(guī)模量產(chǎn),正在生產(chǎn)7nm、6nm移動芯片,并將繼續(xù)進(jìn)階直至3nm節(jié)點(diǎn)。

而在英特爾2020年的設(shè)備投資計(jì)劃中,不僅要增加現(xiàn)有14nm/10nm的產(chǎn)能,還要對7nm/5nm工藝進(jìn)行投資。或許,按照以往的邏輯,英特爾的5nm或相當(dāng)于臺積電的3nm,只是不要再像10nm擠牙膏就好。

而真正的巔峰之戰(zhàn)或是3nm。莫大康分析說,從5nm到3nm,芯片的架構(gòu)將改變,F(xiàn)inFET已不可行,有可能轉(zhuǎn)向GAA環(huán)柵架構(gòu),這是一大突破,需要有磨合時期。從目前看3nm已十分昂貴,至于2nm是否可行尚不好預(yù)測,即便技術(shù)可行,但成本太高將很難承受,這最終取決于市場。

外界已預(yù)計(jì)三星將在3nm節(jié)點(diǎn)使用GAA環(huán)柵架構(gòu)工藝,但到目前為止臺積電仍未公開其3nm的工藝路線。無論如何,3nm注定成為工藝歷史的轉(zhuǎn)折點(diǎn)。

未來的“抉擇”

然而不論是3nm還是2nm,工藝終將走向宿命般的終局。

盡管莫大康老師認(rèn)為面對未來,摩爾定律結(jié)束可能是個偽命題,半導(dǎo)體業(yè)仍將持續(xù)向前,但僅僅尺寸縮小越來越困難,只能另辟蹊徑,而新封裝、新材料和新架構(gòu)將扮演“接力棒”角色。

正如衛(wèi)睿提到的是,臺積電最大的風(fēng)險之一是面對摩爾定律終了之后的選擇。而他十分看好先進(jìn)封裝在未來推動芯片性能向前邁進(jìn)的動能,包括CSP、WLP、3D IC、SiP等。

與之相合的是,臺積電、三星、英特爾等紛紛涉足封測領(lǐng)域。要知道,臺積電今年百億美元投資的20%主要用于先進(jìn)封裝及特殊制程,它在InFO、CoWoS等技術(shù)上的巨大成功,推動制造業(yè)、封測業(yè)以及基板企業(yè)投入了大量人力物力開展三維扇出技術(shù)的創(chuàng)新研發(fā)。英特爾近年來也在EMIB、Foveros 3D封裝等接連出招。

***國立高雄大學(xué)電機(jī)工程學(xué)系教授兼“先進(jìn)構(gòu)裝整合技術(shù)中心(APITC)”主任吳松茂在接受集微網(wǎng)記者采訪時就提到,應(yīng)對先進(jìn)封裝的技術(shù)門檻,需要設(shè)計(jì)和制造方緊密合作,而晶圓端的目光已逐漸從制造向上游走到設(shè)計(jì)端,未來產(chǎn)業(yè)鏈垂直整合將進(jìn)一步加快,具備系統(tǒng)化SoC、SiP設(shè)計(jì)與驗(yàn)證能力的新型產(chǎn)業(yè)模式將興起,而洗牌大戰(zhàn)亦難以避免。

“在很多時候,顯露于歷史書中的,不是最優(yōu)秀的、最有智慧的,而只是幸存的……”半導(dǎo)體工藝節(jié)點(diǎn)歷史也是如此嗎?(文中衛(wèi)睿為化名)

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28969瀏覽量

239001 -

soc

+關(guān)注

關(guān)注

38文章

4398瀏覽量

222990 -

5G

+關(guān)注

關(guān)注

1360文章

48830瀏覽量

574422

發(fā)布評論請先 登錄

高精度半導(dǎo)體冷盤chiller在半導(dǎo)體工藝中的應(yīng)用

半導(dǎo)體冷水機(jī)在半導(dǎo)體后道工藝中的應(yīng)用及優(yōu)勢

半導(dǎo)體制冷機(jī)chiller在半導(dǎo)體工藝制程中的高精度溫控應(yīng)用解析

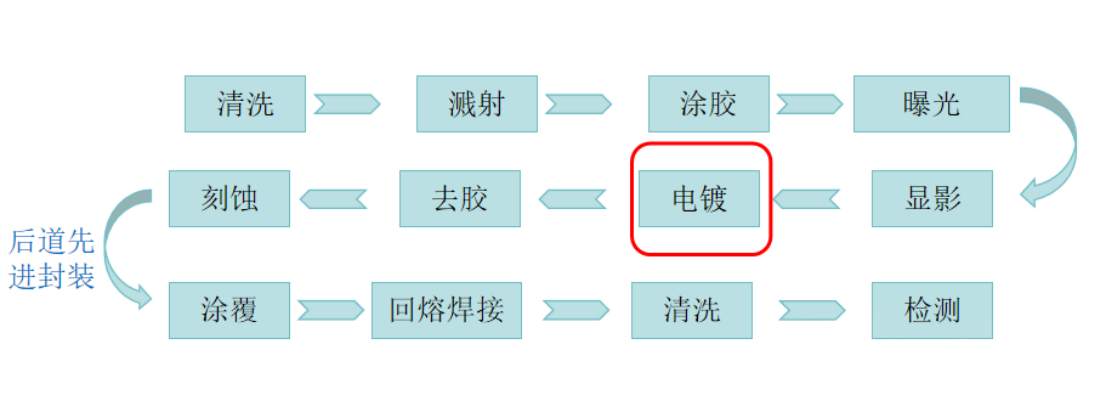

揭秘半導(dǎo)體電鍍工藝

提供半導(dǎo)體工藝可靠性測試-WLR晶圓可靠性測試

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

半導(dǎo)體貼裝工藝大揭秘:精度與效率的雙重飛躍

走進(jìn)半導(dǎo)體塑封世界:探索工藝奧秘

半導(dǎo)體固晶工藝深度解析

倒裝封裝(Flip Chip)工藝:半導(dǎo)體封裝的璀璨明星!

【「大話芯片制造」閱讀體驗(yàn)】+ 半導(dǎo)體工廠建設(shè)要求

【「大話芯片制造」閱讀體驗(yàn)】+跟著本書”參觀“半導(dǎo)體工廠

半導(dǎo)體行業(yè)工藝知識

半導(dǎo)體工藝的分叉路徑如何選擇?

半導(dǎo)體工藝的分叉路徑如何選擇?

評論