盡管有關摩爾定律瀕臨消亡或跟不上時代的傳聞不絕于耳,但半導體行業(yè)似乎多半仍在繼續(xù)開發(fā)新工藝節(jié)點和日益復雜的設計。因此,各家公司幾乎無休止地在為下一節(jié)點做準備,進而過渡至新的節(jié)點。

對晶圓代工廠而言,這種準備工作以新器件、新工藝工具和新工藝流程為中心。同時,他們必須確保為客戶提供合格規(guī)則集(規(guī)則文檔)。設計公司專注于定義電路功能和性能目標,同時確保他們擁有所需的設計軟件和硬件并已經(jīng)準備好進行使用,以便在合理的周轉時間內實現(xiàn)設計 signoff。

雖然很少談論到,但電子設計自動化 (EDA) 行業(yè)也一直在為下一節(jié)點做準備。隨著各種新工藝技術和新設計功能的不斷涌現(xiàn),現(xiàn)在越來越需要提高自動化能力,以自動利用一套經(jīng)過晶圓代工廠驗證的工具進行驗證,同時在不增加運行時間的情況下保持最高的準確度。本文將深入探討下一節(jié)點的開發(fā)挑戰(zhàn),以及Mentor, a Siemens Business 如何為每個“下一節(jié)點”準備 Calibre?nmPlatform。

下一節(jié)點的計算挑戰(zhàn)

衡量半導體行業(yè)向前發(fā)展勢頭的經(jīng)典指標是設計中的集成電路 (IC) 晶體管數(shù)量。摩爾定律描述的是經(jīng)驗觀察:每片 IC 的晶體管數(shù)量以往大約每兩年翻一番。近年來,宣稱摩爾定律瀕臨消亡的聲音似乎一直不絕于耳,但經(jīng)驗證據(jù)持續(xù)表明事實并非如此。圖 1 顯示了最廣為人知的 IC 芯片的晶體管數(shù)量隨時間變化的最新復合圖 [1]。數(shù)據(jù)顯示,晶體管數(shù)量在整個四十五年間一直穩(wěn)定增加,大多數(shù)現(xiàn)代芯片的晶體管數(shù)量接近 20 萬億個。

圖 1:IC 晶體管數(shù)量隨時間的變化。

(數(shù)據(jù)來源:https://en.wikipedia.org/wiki/Transistor_count;數(shù)據(jù)可視化:OurWorldinData.org;Max Roser 根據(jù)CC-BY-SA授權使用。)

設計規(guī)則檢查 (DRC) 復雜度與設計中的多邊形數(shù)量成正比。雖然晶體管數(shù)量對前道工序 (FEOL) 層多邊形數(shù)量有直接影響,但它本身并不能說明多邊形總數(shù)的整體增加。中段工序 (MOL) 和后道工序 (BEOL) 層不僅顯示每層多邊形數(shù)量的增加,而且顯示先進工藝節(jié)點通常需要額外的互連層。多邊形數(shù)量增加的多種來源意味著像 Calibre 套件這樣的驗證工具必須應對超過摩爾定律增長率的多邊形處理量。

當然,與晶圓代工廠工藝相關的設計規(guī)則不只是與設計中的總設計層數(shù)呈函數(shù)關系。隨著時間推移,由于更復雜的環(huán)境感知且對變化敏感的設計組件和工藝技術被整合到最先進的工藝節(jié)點中,在任何給定層上必須檢查的問題類型也會增加。圖 2 顯示了其中幾項新工藝技術和設計敏感性,它們不僅需要更多的檢查,而且需要全新的檢查類型。該圖將層數(shù)的增加與所需檢查類型的增加相對照,說明了設計規(guī)則的數(shù)量和實現(xiàn)這些規(guī)則所需的運算是如何隨著工藝節(jié)點發(fā)展而增加的。每次檢查都需要很多行編碼來實現(xiàn),圖上的平均 DRC 運算數(shù)說明了軟件為正確檢查設計而實際必須執(zhí)行的步驟數(shù)。

圖 2:不同工藝節(jié)點的新功能要求和 DRC 規(guī)則/代碼復雜度。

最終,驗證現(xiàn)代 IC 所需的計算能力和資源是由規(guī)則復雜度乘以設計的總多邊形數(shù)決定的。任何懂數(shù)學的人都會立即注意到,兩個指數(shù)增長的趨勢相乘會帶來相當困難的問題需要克服。Mentor 意識到,為了解決這個似乎巨大無比的挑戰(zhàn),我們要跳出傳統(tǒng)解決方案的思維,探求所有可能的途徑來擴展和提高工具集的性能與生產(chǎn)力。Calibre 團隊不斷為 Calibre 工具庫添加基本的新功能,以便為新的和擴展的需求提供準確的自動檢查,同時仍然讓公司能夠滿足其上市時間安排。

夯實基礎

應對這種爆炸性計算挑戰(zhàn)的兩個最明顯要素是原始引擎速度和存儲器。盡管 Calibre 套件已經(jīng)存在了幾十年,但基礎代碼庫在不斷優(yōu)化,甚至完全重寫,不僅僅是為了添加新功能,還為了顯著提高其執(zhí)行現(xiàn)有功能的能力,以及利用現(xiàn)代分布式和云計算基礎設施。

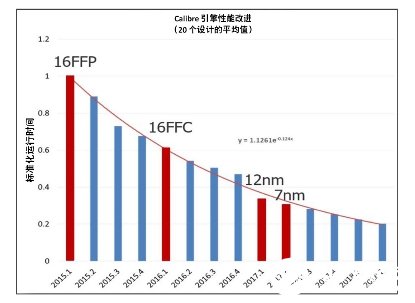

圖 3 顯示了同一 Calibre? nmDRC? 運行集(運行文檔)的不同軟件版本的歸一化運行時間趨勢。每個數(shù)據(jù)點代表平均 20 個實際的客戶設計,反映了 Calibre 底層引擎這個單一因素(其他因素均保持不變)隨著軟件版本的更替所實現(xiàn)的改進。在這三年的時間跨度內,引擎速度提高了 80%。這一趨勢表明了 Mentor 優(yōu)化所有 Calibre 物理和電路驗證工具性能的方式。

圖 3:不同軟件版本的歸一化 Calibre 引擎運行時間趨勢。

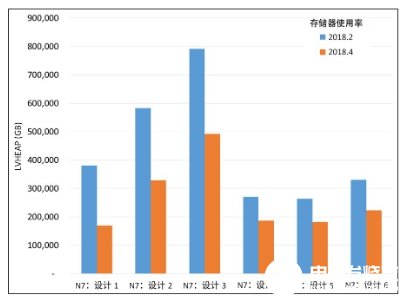

存儲器使用率也是提高工具性能的關鍵因素。圖 4 比較了最近的兩個 Calibre nmDRC 版本在六種不同 7 nm 設計上的表現(xiàn)。隨著底層數(shù)據(jù)結構和存儲器管理技術的改進,存儲器使用率穩(wěn)定下降 40-50%。同樣,這一進展代表了 Calibre nmPlatform 所實現(xiàn)的性能改進。雖然 Calibre nmPlatform 在使用最少存儲器方面已經(jīng)處于業(yè)界領先地位,但 Mentor 仍在不斷尋求進一步改進的機會。

圖 4:Calibre nmDRC 工具最近發(fā)布的各版本在存儲器使用率方面的改進比較。

-

IC

+關注

關注

36文章

6119瀏覽量

179304 -

摩爾定律

+關注

關注

4文章

639瀏覽量

79859 -

節(jié)點

+關注

關注

0文章

222瀏覽量

24959 -

晶體管

+關注

關注

77文章

10018瀏覽量

141586

發(fā)布評論請先 登錄

HarmonyOS NEXT應用元服務布局優(yōu)化精簡節(jié)點數(shù)

HarmonyOS NEXT應用元服務布局優(yōu)化精簡節(jié)點數(shù)

多節(jié)點并行處理架構

CAN通信節(jié)點多時,如何減少寄生電容和保障節(jié)點數(shù)量?

重新分配pod節(jié)點

Jtti:節(jié)點ID變化過于頻繁如何解決

跨境加速新紀元:探索國外IP節(jié)點在云計算中的應用與優(yōu)勢

節(jié)點電壓法電流源串電阻為什么可以忽略

節(jié)點電壓法流入節(jié)點電流怎么判斷正負

節(jié)點電壓法的基本原理、步驟和應用

節(jié)點電壓法的實質是什么

節(jié)點電壓法適用于非線性電路嗎

CAN總線節(jié)點數(shù)計算與外圍電路參考設計

怎么準備ic節(jié)點的計算

怎么準備ic節(jié)點的計算

評論