在任何芯片設(shè)計中,天使和魔鬼都在細(xì)節(jié)之中。AMD過去對皓龍處理器(Opteron)做出的一些架構(gòu)選擇讓它備受煎熬,關(guān)于代碼如何利用硬件的假設(shè)并沒有按計劃實現(xiàn)。老款皓龍?zhí)幚砥鳎∣pteron)處理器最初的設(shè)計非常出色,但公司似乎有意避免在后續(xù)產(chǎn)品上犯同樣的錯誤,比如第二代霄龍(Epyc)服務(wù)器芯片。

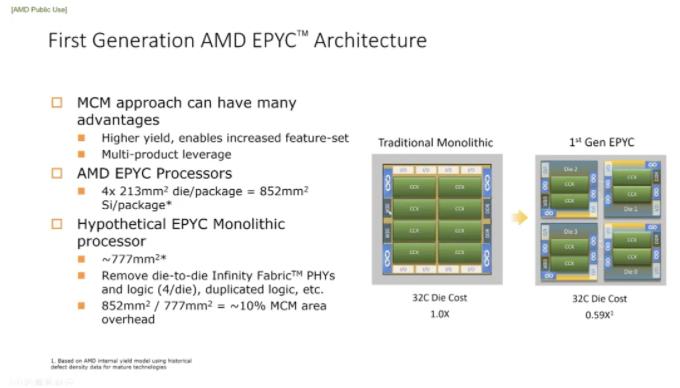

時間和客戶將會告訴我們答案,但這一衍生產(chǎn)品的優(yōu)勢在于,它采用了經(jīng)過大幅改進(jìn)的多芯片設(shè)計,核心采用了更先進(jìn)的蝕刻工藝,似乎正以它在最需要的時候想要的東西,準(zhǔn)確地打入服務(wù)器市場。這對霄龍(Epyc)芯片的發(fā)展來說是個好的開始,它將取代英特爾目前和未來的至強(qiáng)(Xeon)芯片。 我們一直渴望了解新的“羅馬”霄龍(Epyc)服務(wù)器芯片的架構(gòu)細(xì)節(jié),我們在上周的發(fā)布會上介紹了基本的概況、速度、插槽、功率和定價。現(xiàn)在,讓我們和Mike Clark一起深入了解羅馬處理器的架構(gòu)細(xì)節(jié),Mike Clark是Zen核架構(gòu)的研發(fā)主力,同時也是AMD的企業(yè)院士(Corporate Fellow)。從很多方面來說,擁有Zen 2核和混合處理多芯片模塊設(shè)計的羅馬處理器(Rome),是AMD兩年前就希望能夠布局的領(lǐng)域。相比之下,羅馬處理器(Rome)現(xiàn)在越來越好,這一切都始于晶圓代工合作伙伴臺積電在處理器核及其相關(guān)L1和L2緩存區(qū)域采用了7nm先進(jìn)的的蝕刻工藝。 Clark苦笑著說:"能在工藝技術(shù)領(lǐng)域處于領(lǐng)先地位是件好事。"他補(bǔ)充稱,英特爾和AMD將在未來幾年實現(xiàn)跨越式發(fā)展,因此這一勝利不會是永久性的,即便這是不可否認(rèn)的,也是戰(zhàn)略性的勝利。“這個7nm工藝帶來了顯著的改進(jìn)。有趣的是,它使我們的晶體管密度提高了2倍,但是關(guān)于主頻,實際上與臺積電TSMC和及工具人員做了大量工作。通常,當(dāng)你使用一項新技術(shù)時,主頻會下降,你會失去Vmax,需要一些時間才能使主頻恢復(fù)到原來的水平。但是我們能夠和他們一起創(chuàng)造一個非常好的7nm的主頻并且保持同樣的功率。當(dāng)然,如果你從另一個角度來看晶體管,你可以在同樣的性能水平上獲得一半的功率。” 每個時鐘或IPC指令也是羅馬處理器(Rome)架構(gòu)的重要組成部分。從幾年前最后一次Opterons芯片使用的“Excavator”核心到“Naples”霄龍(Epyc)芯片使用的Zen 1核,AMD能夠在固定時鐘的基礎(chǔ)上將IPC增加50%,這是一個巨大的飛躍。類似于ARM的“Ares” Neoverse設(shè)計。ARM實際上預(yù)計IPC將增加60%,但公平地說,Excavator Opterons和Cortex-A72芯片一開始在IPC方面都不是很強(qiáng)大——至少與英特爾的Xeon核無法相提并論。現(xiàn)在,AMD和ARM正在迎頭趕上,隨著Zen 2內(nèi)核在羅馬處理器(Rome)上的使用,AMD又增加了15%的IPC。英特爾新一代IPC的改進(jìn)幅度在5%到10%之間,大約是平均水平的一半。

Clark說,當(dāng)IPC上升時,芯片架構(gòu)師通常要付出更高的功耗的代價,但是Zen 2核設(shè)計的目標(biāo)是使其與Naples的Zen 1相比保持功率持平。事實證明,羅馬處理器的工程師為此施加了壓力,并且能夠?qū)⒑说墓慕档?0%,超過了通過微縮工藝從Naples的14納米到用于Zen 2的7納米的功耗。實現(xiàn)這一目標(biāo)的主要方法之一是將核心中的操作緩存加倍,這有助于降低功耗并提高性能。 事實上,AMD實際上把每個Zen 2核上的L1指令緩存從64 KB縮小到了32 KB,并把晶體管的區(qū)域還給了op和分支預(yù)測單元,還用其中的一些增加了第三個地址生成單元。將L1數(shù)據(jù)與指令緩存(均為32kb)的關(guān)聯(lián)度提高一倍,達(dá)到8路,AMD將浮點數(shù)據(jù)路徑寬度加倍,然后將L1緩存帶寬加倍,以跟上它的速度。(Clark說,一個64 KB的8路關(guān)聯(lián)L1緩存將占用太多的功率,而對于64核,這將是一個大問題。)L3的緩存在每個小芯片(Chiplets)上加倍,達(dá)到16MB/ pop,并且在封裝上有兩倍多的chiplets,是L3緩存容量(256MB)的四倍,相當(dāng)于Naples 處理器的容量。它并不是把所有的東西都翻倍,但隨著核數(shù)和chiplet翻倍,試圖達(dá)到更好的平衡。這包括分支預(yù)測、指令獲取和指令解碼單元,如下圖所示:

“我們喜歡能同時提高功率和性能,”Clark解釋道。“經(jīng)常地走在正確的道路上是很重要的,因為最糟糕的功耗使用就是執(zhí)行那些你正要扔掉的指令。”在我們動態(tài)地發(fā)現(xiàn)我們做錯了之后,我們并沒有扔掉進(jìn)程。這肯定會在前端消耗更多的功耗,但在后端會帶來好處。” 這就引出了Zen 2核心中的整數(shù)和浮點指令單元。

在整數(shù)方面,算術(shù)邏輯單元(ALU)計數(shù)在4處保持相同,但是Zen 2內(nèi)核中的地址生成單元(AGU)計數(shù)增加了1,總數(shù)為3。ALUs和AGUs的調(diào)度程序都得到了改進(jìn),寄存器文件和重新排序緩沖區(qū)的大小也得到了提高。并且針對ALUs和AGUs,控制同時多線程(SMT)的算法的公平性也進(jìn)行了調(diào)整,以處理Zen 1的設(shè)計中不平衡。

當(dāng)然,英特爾四年前在“Knights Landing”Xeon Phi處理器中實現(xiàn)了一個非常優(yōu)雅的512位寬AVX-512矢量單元,并帶來了它的一個變量 - 有人會說一個不太優(yōu)雅的變量,因為它更難以由于它的實施方式而保持供給 - 對于“Skylake”Xeon SP處理器而言,使用當(dāng)前的“Cascade Lake”Xeon SP芯片基本保持不變,除了能夠在機(jī)器學(xué)習(xí)推理工作負(fù)載中消耗一半精度的指令之外。 Clark表示AMD正在考慮在未來的霄龍(Epyc)芯片中使用512位向量,但此時并不相信只添加更寬的向量是消耗晶體管預(yù)算的最佳方法。首先,Clark補(bǔ)充說仍有很多浮點例程不能與512位并行 - 有時甚至不能達(dá)到256位或128位-因此,在Epyc行中,在向量引擎上移動到512位是有意義的。我們認(rèn)為,AMD可能會成為一個快速的追隨者,做類似于DLBoost機(jī)器學(xué)習(xí)推理指令的事情。也許該功能已經(jīng)在框架中,等待在將來某個軟件堆棧準(zhǔn)備就緒時激活。 在Zen 1內(nèi)核中,它有一對128位向量,執(zhí)行AVX-256指令需要兩個操作,但是Zen 2可以在一個時鐘中運(yùn)行AVX-256指令;這顯然需要更少的能量。雙精度乘法在Zen 1上花費(fèi)了四個周期,而在Zen 2上只花費(fèi)了三個周期,這提高了浮點單元的吞吐量和功率效率。(上面引用的IPC圖用于整數(shù)指令,而不是浮點指令。) 至于為Zen 2內(nèi)核供電的高速緩存,支持高速緩存的所有結(jié)構(gòu)都更大,并提供更高的吞吐量,從而推動IPC:

下面是Zen 2的CPU復(fù)雜度和緩存層次結(jié)構(gòu):

增加每個核心中的L2緩存和核心上的L3緩存是實現(xiàn)Zen 2核心中潛在IPC的關(guān)鍵,因為正如Clark正確地說的那樣:“減少內(nèi)存延遲的最佳方法是一開始就不去那里。“ 加上這一切,你將8個CPU復(fù)合體以及I / O和內(nèi)存集線器 - 總共9個芯片 - 放到封裝上,制成一個頂級的羅馬Epyc。較低的倉庫SKU在封裝上具有較少的核心小芯片,有時在每個裸片上激活的核心較少,這就產(chǎn)生了羅馬Epyc 7002系列芯片的廣度,正如我們上周詳述的那樣。 這是拆除Naples和羅馬的MCMs,顯然它們的結(jié)構(gòu)非常不同:

使用PCI-Express的第二代Infinity Fabric變體進(jìn)行了一些重要更改,這些變體分別用于將Naples和羅馬插座中的小芯片相互鏈接。Naples小芯片可以在一個時鐘內(nèi)對Infinity Fabric進(jìn)行16字節(jié)讀取和16字節(jié)寫入 - 精細(xì)打印中的FCLK是結(jié)構(gòu)時鐘的縮寫 - 而羅馬芯片中的Infinity Fabric可以讀取32字節(jié)和16每個結(jié)構(gòu)時鐘的字節(jié)寫入。 雖然羅馬芯片插入與Naples芯片相同的插槽,但元件在插座內(nèi)部捆綁在一起的方式卻截然不同。內(nèi)存控制器從CPU復(fù)雜小芯片上移到中央集線器上,在14納米工藝中蝕刻,其運(yùn)行速度比在7納米時更好,因為I / O和內(nèi)存必須將信號從封裝中推出并進(jìn)入主板DRAM和PCI-Express外圍設(shè)備插入的地方。這個集線器芯片共有8個DDR4內(nèi)存控制器,總數(shù)與Naples綜合體相同;每個通道都支持一個DIMM,每個控制器有兩個通道,但羅馬內(nèi)存運(yùn)行速度稍快--3.2 GHz對2.67 GHz - 因此填充所有內(nèi)存插槽時,每個插槽最大可產(chǎn)生410 GB /秒的峰值內(nèi)存帶寬。這比Cascade Lake Xeon SP處理器高45%,該處理器有6個內(nèi)存控制器,總運(yùn)行頻率為282 GB /秒,運(yùn)行頻率為2.93 GHz,比Naples運(yùn)行2.67 GHz的340 GB /秒高出21% DRAM。(這些是雙插槽服務(wù)器的評級。) 羅馬Epycs的真正重大變化,以及將對許多不同工作負(fù)載的性能產(chǎn)生有益影響的變化,就是NUMA域在芯片中的創(chuàng)建方式以及NUMA跳數(shù)的減少 - 下圖中的距離 - 這是從處理器復(fù)合體的一部分移動到另一部分所需的。看一看:

這基本上是一個NUMA服務(wù)器,該中心集線器是一個芯片組,使用非統(tǒng)一的內(nèi)存訪問技術(shù)將chiplets(在這個類比中是插槽)連接到一個嬰兒共享內(nèi)存系統(tǒng)中,從而將緩存和主內(nèi)存捆綁在一起。 使用Naples芯片,從任何一個裸片到另一個裸片有三種不同的距離,這就是內(nèi)存掛起。有一個跳到兩個相鄰的芯片,有時兩個跳到對角線對面,三個到第二個插座中的芯片在雙插槽設(shè)置中。現(xiàn)在,有兩個NUMA域,只有兩個不同的距離。它是從一個小芯片通過中央集線器到連接到任何處理器的內(nèi)存的一跳,然后另一個跳過Infinity Fabric到第二個中央集線器以及掛起它的內(nèi)存。為了進(jìn)一步簡化問題,只有兩個NUMA域 - 每個羅馬復(fù)合體一個。這應(yīng)該使Windows Server和Linux在單插槽和雙插槽系統(tǒng)上運(yùn)行得更好,Clark 說,對于 Naples 而言,Windows Server在實施NUMA方面比Linux更麻煩。對羅馬NUMA架構(gòu)的這些變化的結(jié)果是,性能應(yīng)該更好,更均勻,并且需要更廣泛的工作負(fù)載才能啟動。I / O和內(nèi)存控制器集線器芯片還實現(xiàn)了用于將外圍設(shè)備連接到系統(tǒng)的PCI-Express 4.0通道,在雙插槽服務(wù)器的情況下,將一對羅馬計算復(fù)合體相互捆綁在一起。 與Naples芯片一樣,每個羅馬芯片都有128個PCI-Express通道,可以通過多種不同方式進(jìn)行配置,如下圖所示:

與Naples一樣,PCI總線的一半用于實現(xiàn)兩個插座之間的NUMA鏈路,因此單插槽和雙插槽羅馬只有128個PCI-Express通道用于外圍設(shè)備。羅馬的網(wǎng)卡有兩倍的帶寬,實際上可以驅(qū)動100 Gb /秒和200 Gb /秒的適配器,而PCI-Express 3.0在使用前者方面遇到了麻煩,而在普通的x8插槽中則不能用后者。這些通道可以單獨(dú)使用,通常組合成一對(x2)用于存儲設(shè)備,可能為羅馬系統(tǒng)中的56個NVM-Express驅(qū)動器和高速網(wǎng)絡(luò)接口卡留出空間。 從技術(shù)上講,Naples芯片有一個單獨(dú)的x1通道,與Infinity Fabric控件分開。由于存在中央集線器,因此x1通道也可用于其他流量。這意味著單插槽羅馬服務(wù)器技術(shù)上有129個PCI-Express 4.0通道,而雙插槽羅馬服務(wù)器有130個通道。英特爾至強(qiáng)可以縮小到x4通道; 據(jù)Clark說,他們不能做x2或x1車道。我們以前沒有聽過這個。 最后,Zen 2核心有一些架構(gòu)擴(kuò)展,這里概述了這些擴(kuò)展,并沒有被反饋到Naples芯片的Zen 1核心:

接下來,我們將看看AMD如何將Rome Epycs與Xeon競爭對手相抗衡,以及英特爾對Rome芯片最初和長期的反應(yīng)。

-

amd

+關(guān)注

關(guān)注

25文章

5586瀏覽量

136331 -

晶圓代工

+關(guān)注

關(guān)注

6文章

868瀏覽量

49199 -

服務(wù)器芯片

+關(guān)注

關(guān)注

2文章

126瀏覽量

19520

原文標(biāo)題:挑戰(zhàn)Intel,AMD擁有足夠的底氣嗎?

文章出處:【微信號:icbank,微信公眾號:icbank】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何將python文件導(dǎo)入到ROS系統(tǒng)中

AMD處理器2024年Q4銷量占比超英特爾

中科新松協(xié)作焊接機(jī)器人加速船舶智能化

AMD獲得玻璃核心基板技術(shù)專利

AMD加入玻璃基板戰(zhàn)局

馬斯克腦機(jī)接口競爭對手Precision公司融資9300萬美元,估值達(dá)5億美元

超越英偉達(dá),AMD還需要10年

英偉達(dá)年度研發(fā)支出超120億美元,為AMD的兩倍之多

如何將LVDS/OLDI橋接到HDMI/DVI

歐盟要求蘋果向對手開放操作系統(tǒng)

突破與解耦:Chiplet技術(shù)讓AMD實現(xiàn)高性能計算與服務(wù)器領(lǐng)域復(fù)興

AMD如何將Rome Epycs與Xeon競爭對手相抗衡

AMD如何將Rome Epycs與Xeon競爭對手相抗衡

評論