IC設計離不開EDA工具的支持,模擬設計也不例外。在<電子發燒友>9月20日舉行的2019年中國模擬半導體大會上,Cadence中國區技術支持總監欒志雨帶來了主題為《中國模擬IC升級更需要借力EDA工具》的演講,在本次演講中,他闡述了針對16nm及以下節點工藝的模擬IC設計需要注意的問題。

圖1:Cadence中國區技術支持總監欒志雨。

流程規范化

目前大家普遍都認為數字芯片的設計流程更加規范和自動化,不過這幾年模擬芯片設計也在向設計流程規范化和自動化方向演進。隨著16nm及以下工藝節點的要求越來越嚴格,這就要求模擬電路設計流程也需要規范化和自動化。

對于模擬設計來說,最難的是Spec的管理。Cadence從前年開始,跟國內很多企業合作,推出了一個ADE(Analog Design Environment;模擬設計環境 ) Verifier工具,該工具也可以稱為ADE Planner,是一個模擬設計項目的規劃管理工具。

作為一個模擬設計工程師,在一個項目周期內,通常需要從撰寫/閱讀客戶需求或功能需求開始,最后到測試芯片性能,看其是否達到標準結束。在實際工作中,芯片測試的工作大多數時候是由測試工程師完成的,而模擬設計工程師則需要負責芯片的驗證,即通過電路仿真工具搭建的Test Bench,看設計出來的電路是否滿足產品需求中的要求。

在這個過程中,由兩個重要的指標:一是產品需求中的指標(Spec)都被驗證了嗎(覆蓋率)?二是驗證都通過了嗎(通過率)?解決這兩個問題后,還需要知道Test Bench中的Spec設置和產品需求中的Spec是否一致,因為在電路設計過程中,經常會碰到Spec改動的事情。

欒志雨解釋說,如果使用ADE Verifier對模擬設計項目進行管理,就能夠很清楚地看到,哪些Spec是通過驗證了的,哪些是沒有通過驗證的,以及哪些還需要進一步分析的,一目了然。

對模擬設計而言,還有一個問題就是物理實現。其實模擬電路也是可以拆分的,拆分成一些更小的電路結構。比如現在的代工廠就會基于此類結構,提供一些已經經過測試,良率可以達到一定保障的版圖,供模擬芯片設計公司選用。

欒志雨在演講中表示,這類版圖有很多就是使用Cadence的參數化單元Pcell工具來實現的。模擬設計工程師在進行版圖設計的時候,如果電路很大,就需要畫很多不同尺寸的MOS管,工作會變得很繁瑣。而如果使用Cadence最近推出的PcellDesigner工具開發就方便很多,當需要畫一個MOS管時,只要調用出Pcell,在其屬性中填入所需要的參數(W、L、Gate number等等),就能方便地得到想要的MOS管。這樣可以避免單元的重復創建,大大減輕單調乏味的創建圖形工作。

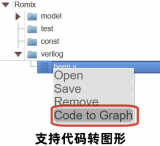

他還特意指出,現在使用PcellDesigner還可以開發SuperPcell,將更加方便。SuperPcell指的是客戶可以用Coding的方式實現做LDO、或者是運放,這樣工程師在調參數的時候就會非常容易。

傳統的模擬設計都是從底層到頂層來進行設計的,但在先進工藝節點階段,這種設計流程會有一些問題。特別是在繞線資源和版圖資源相當緊張的時候,因此,客戶希望能夠有從頂層到底層的設計流程來進行模擬芯片設計。因為從頂層開始設計,能夠幫助工程師在頂層、模塊層和單元層更為有效地進行規劃。

Cadence新推出的Design Planner工具可以為成熟工藝節點和高工藝節點的版圖設計提供先進方法,實現無縫銜接版圖-布局-布線的功能。同時,它也能夠嵌入到數字設計當中,與數字設計同時進行。它具有的創新功能有:

層次化原理圖驅動版圖設計:結合了自上而下與自下而上設計方法的優勢,避免單獨使用任意一種設計方法時而引起的缺陷;

層次可視化:用戶可在其設計階段隨時隨地根據需求輕松地查看或隱藏設計細節,便于僅查看其所需的內容;

層次及擁塞意識的布局及擺放:提供自動化和輔助生產力;

層次化布線和擁塞分析:提前提供真實的路布線及擁塞分析信息。

圖2:電子和系統設計發展趨勢。

In-Design嵌入

In-Design概念是在28nm時提出的,原因是隨著工藝節點越來越高,很多芯片是迭代研發設計的,有時候前一代芯片設計驗證是沒有問題的,迭代后的設計在后端仿真時會出現問題。In-Design就是把后端需要仿真的效應,比如LDE效應、寄生效應、EM效應等都在前端仿真時實現,以方便在流程中提前發現問題,提前預防和解決。

比如Cadence的Pre_EM check就可以提前做EM仿真,發現EM問題。欒志雨指出,其實相對布線造成的EM問題,device層的EM問題對后端的影響更大。因為布線造成的EM問題可以通過修改版圖,或者增加線寬等一些局部的修改來解決,而Device層的EM問題很難從后端進行修改,必須修改Device的尺寸,而修改尺寸會導致版圖出現問題。

那如何在前端的時候就發現Device層面的問題呢?Pre_EM check就可以幫忙解決。

當然,前仿真不僅針對EM,也可以對LDE效應,EAD效應,以及布線的影響進行檢查。提前發現問題,以做出應對方案。

多系統結合

近年來,芯片的設計和系統的結合越來越緊密。傳統的模擬設計IP,或者是STA是一個黑盒子,而Cadence最新的Liberate AMS讓模擬的STA不再是黑盒子了。AMS基于MX經證明的技術,具有激勵表驅動流程、自動偵測setup/hold約束、動態電路分區和靜態電路分區等功能。其獨有的特點有Deck目錄可追溯的特征描述、模擬電路的分區可微調、增強版的激勵表接口(可指定model、電壓、電流源和電壓源等。)、支持內部節點識別,以及支持指定黑盒子單元(比如主動電阻單元、Verilog-A模組等等)。

此外,該工具也可以讓模擬的Power不再是一個黑盒子,以及芯片的襯底分析成為可能。

圖3:光電一體分析,目前Cadence的EDA工具支持硅光芯片設計和封裝實現。

結語

不論是電子設計,還是系統設計,其實一直都在不斷演化當中,未來模擬設計的EDA工具也會發生改變,比如說將來一定會有大量的模擬芯片設計是基于云端并行和分布式計算的,模擬芯片的設計會有更加規范化的流程,以及會越來越多地用到機器學習。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

模擬IC

+關注

關注

8文章

173瀏覽量

29794 -

Cadence

+關注

關注

65文章

963瀏覽量

143769 -

eda

+關注

關注

71文章

2880瀏覽量

176334 -

模擬芯片

+關注

關注

8文章

646瀏覽量

51548

發布評論請先 登錄

相關推薦

熱點推薦

產學研融合!思爾芯數字EDA工具走進北航課堂

5月22日,國內首家數字EDA供應商思爾芯(S2C)走進北京航空航天大學,為集成電路相關專業學子帶來《數字IC軟件仿真概論》專題培訓。此次活動通過技術講解、工具演示相結合的形式,全方位展示了國產

用一套Linux系統,撐起整個芯片設計平臺?CFA團隊教你如何搭好EDA智算平臺的技術底座

時間,則可以選擇 Ubuntu。

軟件包管理:從RPM到YUM,讓EDA工具“一鍵上崗”

在對Linux系統的使用和操作過程中,需要經常安裝、卸載和升級各種應用軟件。

要讓一個系統能正

發表于 05-07 14:44

西門子EDA工具如何助力行業克服技術挑戰

西門子EDA工具以其先進的技術和解決方案,在全球半導體設計領域扮演著舉足輕重的角色。本文將從汽車IC、3D IC和EDA AI三個方向,深入

STCO發展促使EDA工具考慮更多系統級因素

迅速發展,對芯片技術提出了更高的要求,傳統的SoC在應對這些需求時已顯得力不從心。Chiplet技術作為一種新興的解決方案,通過將不同功能模塊集成在一起,提供了更高效、更靈活的芯片設計方式。 ? 在Chiplet設計中,EDA工具需要

模擬IC設計中Spectre和HSPICE仿真工具的起源、差別和優劣勢

本文詳細介紹了在模擬集成電路的設計與仿真領域中Spectre和HSPICE兩款仿真工具的起源、差別和優劣勢。 在模擬集成電路的設計與仿真領域,Spectre和HSPICE是兩款具有廣泛應用的仿真

智多晶EDA工具HqFpga軟件實用小功能

智多晶EDA工具HqFpga軟件實用小功能增加啦,支持生成可調用網表的功能和ballmap功能。下面來給大家講解一下如何通過HqFpga軟件生成可調用的網表文件以及ballmap功能的使用。

訓練AI大模型需要什么樣的gpu

訓練AI大模型需要選擇具有強大計算能力、足夠顯存、高效帶寬、良好散熱和能效比以及良好兼容性和擴展性的GPU。在選擇時,需要根據具體需求進行權衡和選擇。

請問TLV320AIC3268的ADC轉換后的數據格式是什么樣的?

我在使用TLV320AIC3268,但是不知道ADC轉換后的數據格式是什么樣的?比如是二進制補碼嗎?轉后的數據與輸入的模擬信號的電壓值有什么關系?

發表于 10-14 07:48

代碼整潔之道-大師眼中的整潔代碼是什么樣

幾個月前寫了一篇文章“如何寫出難以維護的代碼”,從中能大概了解到不好維護的代碼是什么樣,有哪些壞味道,那肯定有人會反問,難以維護的代碼見的太多了,也知道長什么樣,但是對于好維護的代碼是什么樣的比較

概倫電子引領國產EDA產業升級

升級,從最初的簡單替代轉向了對EDA工具性能、效率、可靠性等方面的需求,本土EDA企業迎來了新的發展訴求,并購整合趨勢愈發加快。

STM32H743ZIT6想要實現千兆網口,需要外掛什么樣的PHY芯片?

各位大佬,我想咨詢一個問題,關于STM32H743ZIT6想要實現千兆網口,需要外掛什么樣的PHY芯片,謝謝

發表于 05-31 07:59

模擬IC升級需要什么樣的EDA工具支持?

模擬IC升級需要什么樣的EDA工具支持?

評論