摘要:在高速印刷電路板(PCB)設計中,邏輯門元器件速度的提高,使得PCB傳輸線效應成了電路正常工作的制約因素。對傳輸線做計算機仿真,可以找出影響信號傳輸性能的各種因素,優化信號的傳輸特性。采用全電荷格林函數法結合矩量法提取高速PCB傳輸線分布參數并建立等效時域網絡模型,應用端接I/O緩沖器IBIS瞬態行為模型,對實際PCB布線進行電氣特性仿真,其結果與Cadence公司的SPECCTRAQUEST軟件仿真結果一致,且仿真效率得到提高。

關鍵詞:傳輸線;全電荷格林函數法;高速印刷電路板;IBIS模型

隨著技術的進步,目前高速集成電路的信號切換時間已經達到幾百皮秒(ps),時鐘頻率也已達到幾百兆赫茲(MHz),如此高的邊沿速率導致印刷電路板上的大量互連線產生低速電路中所沒有的傳輸線效應,使信號產生失真,嚴重影響信號的正確傳輸。因此有必要對高速印刷電路板(PCB)傳輸線建模并進行計算機仿真,這樣一方面可以確定高速信號傳輸線的時域網絡模型,另一方面也可以通過仿真找出影響信號傳輸性能的各種因素,以便采取措施,盡可能地優化信號的傳輸特性,保證系統的可靠及高性能工作。

當前電路工作頻率不斷提高,當其達到一定程度后,系統的波特性必然變得十分明顯。在PCB設計中傳輸線的尺寸較大,其波特性應首先考慮。對傳輸線的分析必須采用L、C、R、G分布參數模型,這樣系統的電特性分析和電磁場分析密切相關。基于這種模型,應對傳輸線的布局布線進行分析和仿真,由此來指導PCB設計。文中就是采用全電荷格林函數法結合矩量法提取傳輸線的電路元件參數模型,包括集總參數和分布參數(分布電容C、電感L、電阻R和電導G),在建立傳輸線等效時域模型及提取參數的基礎上進行電路分析,應用端接I/O緩沖器IBIS瞬態行為模型,對實際PCB布線進行電氣特性仿真。

采用全電荷格林函數法結合矩量法提取分布參數

對單根傳輸線,C、L、R、G是4個基本的分布參量,由此還可導出特性阻抗、相速或相位常數等參量。其中分布電阻R由所采用的導體材料和物理特性所決定的,而分布電容參數C是最重要的分布參數,因為一旦獲知分布電容參數,除R以外的其他分布參數都可以通過公式轉換得到。

為提取多根導體的分布電容矩陣,必須首先在給定導體電位的條件下求出各根導體的自由電荷電量其求解過程應求得格林函數,而多層介質下的格林函數之所以復雜,在于介質的不均勻。界面上的極化電荷會產生附加電位,其影響將疊加到格林函數的自由空間分量上。因此不妨將自由電荷和極化電荷都作為產生電位的場源,格林函數就可看成單位點電荷(三維)或單位線電荷(二維)在介質均勻的無限空間產生的電位。矩量法即是近似地將待解函數表示為N個相互正交的基函數求和展開式,每一基函數均乘以某一系數。

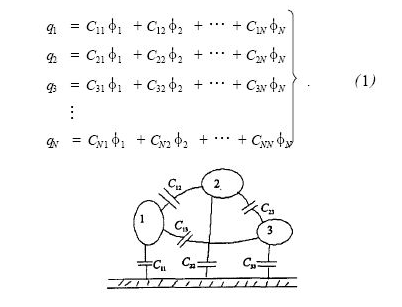

對于具有多根導體的系統內的分布電容,除了要考慮每一根導體自身的分布參量,還應考慮其與其他各導體之間耦合效應的互分布參量,如圖1所示。其分布參量應表示為分布參量矩陣。對N根導體進行分析,其分布電量q與電位φ的關系如下:

圖1多導體系統的部分電容

從式(1)多導體線分布電容參數的定義可知,電容參數的提取必須求解給定導體電位的靜電場,它是一個偏微分方程的邊值問題。通過源區解法求解,其主要問題是積分方程中的核函數——格林函數求取問題。將全電荷格林函數積分方程結合矩量法[3]以數值的方法求解,選擇脈沖基函數并采用點匹配,可得到方程組

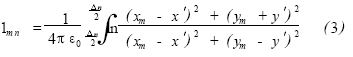

其中N1表示導體和介質的分界分塊數,N~N1表示介質和介質的分界分塊數,總共有N個分塊。前面N1個方程表示場點所在分塊均在導體和介質的分界上,方程式左邊的值pm(m=1,2,…,N1)為分塊中心點的電位;后面的N-N1個方程表示場點所在分塊均在介質和介質的分界,方程左邊的值pm(m=N1+1,N1+2,…,N)應為零,方程式右邊的分塊脈沖基函數αm(m=N1+1,N1+2,…,N)則代表各分塊上的全電荷;系數矩陣1mn(m,n=1,2,…,N),由公式(3)表示。

其中m=1,2,…,N1;n=1,2,…,N,x′及y′為源點直角坐標。

假設導體數量為J1,根據分布電容矩陣的定義即式(1),可依次對J1塊導體中的每一塊賦以單位正電荷,其余導體電位為零,解出式(2),求得各分塊的全電荷,然后將同一導體上的分塊進行組合,可得到各導體上的總全電荷量。將式1和式2聯立求解,積分方程數值化為代數方程組后可得到單位長度分布電容參數。分布電感和分布電導可由分布電容推出,其具體求解公式參見文獻[3]。

傳輸線等效時域模型的建立

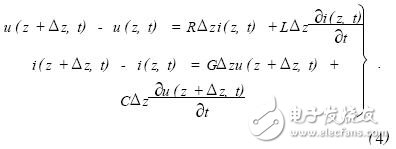

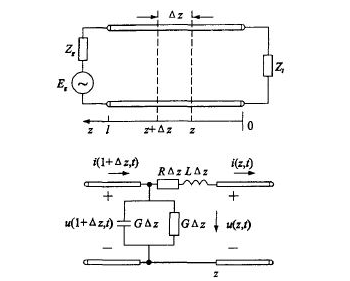

獲得傳輸線分布參數(即C、L、R、G)后,在傳輸線上任意微分小段可等效為由電阻RΔz、電容CΔz、電感LΔz和電導GΔz組成的網絡。設傳輸線始端接有內阻Zg的信號源,終端接有阻抗為Z1的負載,如圖2所示。設在離傳輸線終端z處的t時刻電壓和電流分別為u(z,t)和i(z,t),而在位置z+Δz處的電壓和電流分別為u(z+Δz,t)和i(z+Δz,t)。其等效時域模型為:

圖2傳輸線系統及微分段的等效圖

仿真實驗

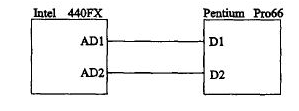

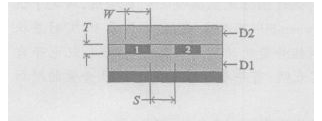

在一塊高速的電路板上,選取D1和D2數據線并行電路結構(如圖3)。接收端為Intel公司提供的器件PetiumPRO66MHz(CPU)的GTL_IO瞬態行為模型(IBIS模型),驅動端為Intel公司提供的器件Intel440FX的PMC_B06120B0S2AZZGBE瞬態行為模型,電路板上的互連線采用帶狀線形式,具有以下參數;兩導體間距S=5mil(1mil=1/1000inch),導體寬度W=5mil,導體厚度為T=0.2mil,介質層的材料為FR-4,D1厚度為10mil,介電常數εr為4.5,另一介質層為大氣,D2厚度為0,介電常數εr為0,帶狀線長度500mil,其橫截面圖4所示電路。

圖3傳輸高速信號D1和D2數據線并行電路結構

圖4D1、D2導線對稱雙微帶線截面圖

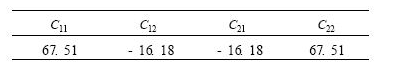

采用全電荷格林函數法結合矩量法提取單位長電容參數,計算結果如下表:

表1雙導體微帶線分布電容參數計算結果pF/m

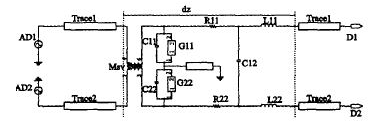

然后通過傳輸線等效時域模型的建立,進行計算機仿真,經過參數提取后等效如圖5所示。

圖5D1、D2信號傳輸線等效模型拓撲圖(Msv為走線間互感)

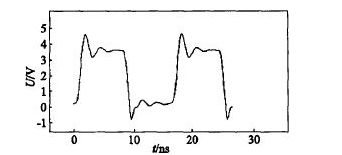

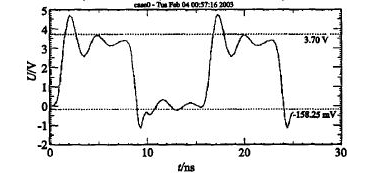

采用頻率為66MHz的脈沖輸入信號,分別從AD1、AD2端口輸入,觀察D1端口接收到的單脈沖信號,它不僅受到傳輸線TRACE1(AD1和D1連線)自分布參數的影響,同時受到傳輸線TRACE2(AD2和D2連線)的互分布參數影響,用MATLAB編程可繪出接收端D1仿真波形如圖6所示,在圖7中給出的是Cadence公司的Specctraquest軟件產生的接收端D1的仿真波形。比較圖6和圖7,可以發現兩種仿真波形基本一致。然而在相同計算量的條件下,采用本文的方法進行仿真的時間只有Specctraquest軟件仿真時間的3/5。

圖6接收端D1利用分布參數和傳輸線微分模型算法得到的仿真波形

圖7接收端D1用Cadence公司的Specctraquest軟件產生的仿真波形

結論

在高速PCB設計中,不用仿真而只憑傳統設計方法或經驗很難預測和保證信號的完整性,仿真已成為高速信號設計的必要手段。本文采用全電荷格林函數法結合矩量法對傳輸線提取分布參數,建立等效時域網絡模型,應用端接I/O緩沖器的IBIS瞬態行為模型,對實際傳輸高速信號的傳輸線進行仿真,在仿真效率提高了近一倍的情況下,其結果與Specctraquest軟件仿真結果相吻合。

-

FPGA

+關注

關注

1643文章

21967瀏覽量

614262 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43753

發布評論請先 登錄

知識分享-傳輸線的返回電流(信號完整性揭秘)

傳輸線高頻參數之Crosstalk

PCB制板廠加工問題很大啊,高速PCB傳輸線阻抗一直往上跑

PCB Layout中的三種走線策略

傳輸線特征阻抗是設計中最重要的因素

DAC3482的I通道輸出電路,傳輸線變壓器有什么作用?

使用SIDesigner進行銅箔粗糙度建模及仿真分析

平衡傳輸線標準的重要性

高速數據傳輸線纜組件 惡劣環境中的可靠選擇

高速信號傳輸鏈路的損耗和均衡

基于高速PCB傳輸線建模的仿真是怎樣的

基于高速PCB傳輸線建模的仿真是怎樣的

評論