設計重用 - 在多芯片設計上采用預先設計和預先驗證的內核(通常稱為不準確的,作為知識產權或IP)的能力對于可行的片上系統設計是必要的。除了設計重用之外,還需要保留那些缺乏使用這些塊的合法權利的人和組織的可重用塊。

保護芯片核心是一個復雜的問題,因為有人可能會使用多個抽象級別或傳輸核心,如RTL,門級或物理布局數據,以及核心供應商的擴散。由于基于核心的芯片設計相對較新,商業核心保護仍處于早期階段。通過了解保護硬核和軟核芯片的可用和不斷發展的方法,您可以更好地設計可重復使用的塊并將這些塊傳輸給公司內外的其他人。

核心不等于IP

關于保護可重用硅芯免受非法使用的討論會帶來核心或虛擬組件(VC)與IP之間的差異。盡管許多人將芯片內核稱為IP,但對于大多數關于片上系統和可重用內核的討論而言,這個術語并不具體。知識產權是一個廣義的術語,定義為公司擁有的任何特殊知識,使其在競爭中具有優勢(參考文獻1)。硅芯是IP,但公司的專利,特殊芯片工藝等等也是如此。核心保護比一般的知識產權保護更受關注。

知識產權保護通常采取法律威懾的形式 - 用于防止某人竊取知識產權的方法。這些威懾包括專利,版權,商標和商業秘密(參考文獻1)。這些保護機制通常是有效的,但肯定不是萬無一失的。例如,亞洲街區各國都有很多盜版CD和錄像帶。另一方面,核心保護超越了這些法律威懾力量。諸如加密和編譯之類的保護方法在使核心盜竊變得更加困難方面是有效的。同時使核心盜竊更難的是水印,數字指紋識別和標記 - 所有檢測和提供盜竊證據的方法。但是,沒有任何保護機制是萬無一失的。你可以在時間和資源方面花費極其昂貴的時間來竊取核心,但是你不能讓它變得不可能。

可重復使用的核心有三種形式:軟,堅固和堅硬。供應商通常用HDL,Verilog或VHDL描述軟核,但核心也可能有門級或網表描述。軟核不包含物理信息;您可以為各種硅工藝設計它們。這種靈活性的權衡是一組松散的性能規范,因為性能(速度和功率)取決于核心的物理實現。硬核是嵌入芯片中的已定義物理塊。由于硬核具有固定的拓撲和目標進程,因此它具有明確定義的性能。硬核和軟核之間是堅固的核心,具有一些結構和拓撲優化。由于公司核心包含一些布局指導,因此其性能比軟核的性能更可預測。公司核心具有一系列表示形式,從布局規劃的RTL塊到完全放置的網表。不同類型的內核需要不同類型的保護和檢測。

通常以加密或編譯的形式添加技術核心安全性的結果是,您更難以使用核心(見附文“模型編譯保護核心”)。保護核心的本質降低了核心“膽量”的可見性,使得設計和調試核心變得更加困難。另一方面,核心保護的檢測機制沒有隱藏核心工作方式細節的問題(表1)。

兩種不斷發展的核心盜竊檢測方法是數字水印和數字指紋識別。水印是您在某個抽象級別(例如RTL)添加到核心的東西,并且您可以在稍后的抽象級別(例如門級或核心的物理描述)中進行檢測。您希望在核心上使用數字水印,以使水印對核心性能影響很小或沒有影響;此過程類似于添加測試邏輯。另一方面,數字指紋不是您添加到核心以使其可唯一識別的內容,而是核心結構中已存在的某些功能。因為您不會向核心添加任何內容,所以您可以將指紋視為被動水印。

數字水印是保護VC的可行方法,但需要付出代價。如果正確實施,水印是對核心盜竊的威懾。開銷(面積,性能下降或兩者兼而有之)可能很低,您可以在不同的設計 - 抽象級別應用不同的水印。雖然水印阻止了VC的盜竊,但它們并沒有阻止它。此外,添加數字水印并隨后檢測水印需要花費時間和資源。同樣,雖然您不必添加數字指紋,但仍然需要花費時間和金錢來識別核心的唯一指紋,然后再讀取指紋。

您可以通過以下方式實現數字水印和指紋旨在隱藏他們從潛在小偷那里獲得的保護的技術。另一方面,標記是一種向核心添加信息以幫助跟蹤核心來源,使用者以及其他相關信息的方法。標準單元和存儲器塊提供商Artisan Components(www.artisan.com)開發了一種稱為Artiscan的標記方法,VC供應商在GDS-II文件中插入了描述芯片物理布局(“多邊形”級別)的文件。硬核或標準單元供應商將文本插入到特定代工廠特有的設計層上的ASCII GDS-II文件中。該文本包括核心/單元供應商的名稱,產品名稱,核心/單元的版本號,代工廠名稱和核心/單元區域。核心供應商和代工廠可以根據需要添加信息。 AnArtiscan讀卡器檢測標記的注釋并打印出總結核心信息的報告。

目前正在開發幾種數字水印方案。雖然尚未作為商業產品提供,但一些例子說明了可能成為主流基于核心的產品開發的一部分的水印技術。用于DSP濾波器的一種水印技術在算法開發期間應用水印(參考文獻2)。通過操縱濾波器響應,您可以將數字簽名(位模式)編碼為濾波器的幅度響應(圖2)。片上濾波器性能測量很容易產生簽名。您還可以在架構級別的過濾器中嵌入類似的數字簽名,從而更改過濾器的配置而不修改其傳輸功能。雖然這種技術適用于特定的核心功能 - 過濾器 - 其他水印方案正在開發用于abroaderclass的電路。

通過嵌入數字簽名,您可以在大多數數字控制電路中找到順序邏輯電路的水印方法(參考文獻3和4)。參考文獻3中的技術通過將水印放置在同步時序電路的狀態轉換圖上來工作,使得電路呈現特定輸入集的屬性,該電路在非水印版本中是不可能的。一個必要的約束是選擇水印過渡,這樣就不會影響電路的正常功能。您可以將水印添加到門級的有限狀態機(FSM),然后使用適當的FSM輸入序列對其進行檢測。參考文獻4中的工作類似。此技術修改FSM以使用意外的輸入集提供可預測的輸出。修改是I/O集的水印,在正常電路操作期間不會發生。水印I/O集難以檢測,因為它在一系列正常的I/O序列中。

FPGA為實現數字水印提供了獨特的機會,因為所有FPGA芯片都有一些未使用的邏輯。例如,您可以在Xilinx(www.xilinx.com)器件的未提交的可配置邏輯塊(CLB)的查找表中嵌入透明數字簽名。為了增加使用基于查找表的簽名對芯片進行逆向工程的難度,該方法對每個設計實例的簽名使用不同的CLB。此方案導致每個實例的布局不同。簽名很難被檢測到并且對電路性能沒有太大影響,盡管簽名的不同指定CLB會導致布局后的某些時序差異。

因為數字水印要求您添加一些內容。核心不需要正常運行的核心,數字指紋似乎是保護您的VC的可行替代方案。 Taeus的業務是專利許可和訴訟的技術調查,已經開發出數字指紋流程。 Taeus在Verilog或VHDL中以設計的行為級別識別指紋。然后,您可以在后續的設計抽象級別讀取指紋,一直到硅實現(圖3)。 Taeus的指紋基于兩個組織為特定任務設計VC的事實,例如PCI核心,有些不同。 Taeus的FingerPrint技術為每個VC識別一個獨特的指紋,將VC與具有類似功能的其他塊區分開來。該技術于5月在Actel(www.actel.com)PCI宏上得到證實。現在,Taeus手動讀取不同抽象級別和硅片上的指紋。到今年年底,該公司希望擁有可用于執行某些閱讀任務的自動化工具。

IT有多廣泛?

如果您包含法律保護措施(如專利和版權),則實施核心保護的供應商和用戶的百分比很高。如果僅考慮VC保護的技術方法,則使用率會急劇下降。最近一份總結VC風險保護調查的報告顯示,接受調查的公司中有近90%(包括系統公司,半導體供應商,IP供應商和設計公司)使用一些法律手段來保護核心(參考文獻6)。同一調查報告稱,這些組織中只有約42%通過加密保護VC,35%使用其他技術手段,如數字水印和指紋識別。低水平的基于水印和指紋的核心保護是由于許多因素造成的,包括基于技術的VC保護方案的不成熟以及缺乏數字水印和指紋標準(參見附文“VSIA印刷機的核心 - 保護標準“)。采用這些保護技術還需要額外的資源;許多進行基于核心設計的公司都不愿意花時間和金錢通過這些手段進行核心保護。

從硅代工廠的角度來看,盡管聯華電子(www.umcgroup.com)正在與Artisan合作Artiscan標記技術,TSMC(www.tsmc.com)不使用芯片標簽進行跟蹤。該公司目前正在手動跟蹤芯片,但正在考慮自動化流程。臺積電正在尋求的另一項核心保護技術是為核心供應商存儲核心數據文件。當代工廠客戶想要將芯片設計到芯片上時,臺積電將提供“幻像”塊和適當的模型。在客戶完成設計并準備好硅片之后,TSMC將核心的GDS-II文件添加到完整的芯片GDS-II中;客戶永遠不會看到詳細的核心數據文件。

Phoenix Technologies(www.phoenix.com)營銷副總裁Robert Nalesnik回應了許多核心供應商和用戶的抱怨。目前的VC技術保護方法對鳳凰城及其客戶來說太有限了。您必須能夠在所有后續設計步驟中通過最終芯片檢測嵌入式數字水印或在某種設計抽象級別建立的已識別數字指紋。當前可用的加密和編譯方案不存在標準化。如果鳳凰城選擇支持商業核心模型加密工具,該公司將不得不為不同的客戶提供不同的工具 - 這是鳳凰不愿意承擔的負擔。

Nalesnik還表示許多基于核心的關注 - 芯片設計師:對他們而言,保護方法不得影響設計過程。當然,設計師最初也對測試設計(DFT)技術有類似的關注;他們希望DFT沒有硅開銷或額外的設計時間。然而,設計師對DFT的擔憂逐漸消退,因為DFT的實用性變得明顯。隨著時間的推移,隨著VC保護技術的成熟,設計師對它的反應將遵循與DFT類似的路徑。

模型編譯保護核心

最多廣泛使用的核心保護技術使用加密或安全模型生成來保護模型。這兩種技術在Verilog或VHDL中的軟核模型上效果最佳,并且對于知識產權(IP)導出最有用,例如從供應商到被許可人。加密和編譯是不同的。真正的加密為解密留下了空間 - 加密過程是可逆的 - 源代碼恢復。編譯從HDL源代碼生成二進制對象代碼。編譯是不可逆轉的,因此在編譯后幾乎不可能恢復源代碼(圖A)。 Topdown設計解決方案,Summit Design,Escalade和Synopsys(表1)是一些EDA公司,其產品使用模型源代碼編譯來保護核心模型,并讓設計人員模擬受保護的模型(參考文獻1)。

除了源代碼恢復之外,編譯還提供了比加密更多的優勢。核心供應商可以使用標準接口為多個模擬器生成編譯代碼,例如Verilog的PLI(編程語言接口)。沒有用于保護核心的加密標準。核心開發人員可以為他們的客戶提供編譯模型,然后客戶將模型模擬為芯片設計的一部分。由于模型表示的邏輯采用編譯格式,因此客戶無法破譯此邏輯。最后,一些提供編譯模型的公司可以優化模型上的模擬包裝外殼,以便在目標模擬器上實現最快的執行速度。

|

|

-

PCB打樣

+關注

關注

17文章

2971瀏覽量

22335 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28427 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43722

發布評論請先 登錄

應對芯片設計復雜性 EDA工具需要新典范

AI普及給嵌入式設計人員帶來新挑戰

MMIC技術——實現降低5G測試測量成本與復雜性的雙重突破

高效率的快速部署 玩轉模塊化數據中心 相關資料推薦

毫米波傳感器解決了入口系統設計人員面臨的哪些挑戰

MCU控制芯片必將受惠于工業機器人市場的快速增長

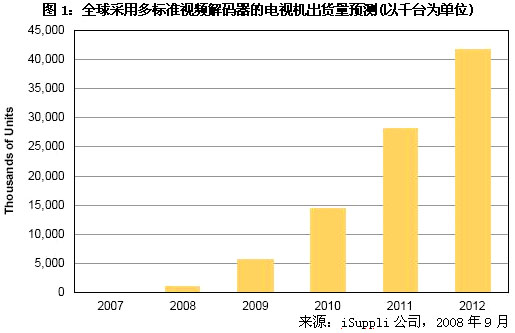

多標準DTV解碼芯片市場將快速增長

氮化鎵電源管理芯片市場將快速增長

ADI推出單芯片寬帶IF接收器子系統AD6676,可減少接收器設計的復雜性

Dave Anderson討論了物聯網給企業云環境帶來的復雜性

ADM1266芯片解決電源排序系統的復雜性問題

芯片設計人員不能總是依賴于他們過去使用的許多傳統技術和計算

降低無線連接、共存的復雜性

芯片復雜性的快速增長給試圖利用芯片上可用門的設計人員帶來了負擔

芯片復雜性的快速增長給試圖利用芯片上可用門的設計人員帶來了負擔

評論