目前常見的封裝有兩種,一種是電動玩具內常見的,黑色長得像蜈蚣的 DIP 封裝,另一為購買盒裝 CPU 時常見的 BGA 封裝。

告訴你什么是封裝

經過漫長的流程,從設計到制造,終于獲得一顆 IC 芯片了。然而一顆芯片相CPU 使用的 PGA(Pin Grid Array;Pin Grid Array)或是 DIP 的改良版 QFP(塑料方形扁平封裝)等。因為有太多種封裝法,以下將對 DIP 以及 BGA 封裝做介紹。

傳統封裝,歷久不衰

首先要介紹的是雙排直立式封裝(Dual Inline Package;DIP),從下圖可以看到采用此封裝的 IC 芯片在雙排接腳下,看起來會像條黑色蜈蚣,讓人印象深刻。此封裝法為最早采用的 IC 封裝技術,具有成本低廉的優勢,適合小型且不需接太多線的芯片。但是,因為大多采用的是塑料,散熱效果較差,無法滿足現行高速芯片的要求。因此,使用此封裝的,大多是歷久不衰的芯片,如下圖中的 OP741,或是對運作速度沒那么要求且芯片較小、接孔較少的 IC 芯片。

至于球格陣列(Ball Grid Array,BGA)封裝,和 DIP 相比封裝體積較小,可輕易的放入體積較小的裝置中。此外,因為接腳位在芯片下方,和 DIP 相比,可容納更多的金屬接腳。相當適合需要較多接點的芯片。然而,采用這種封裝法成本較高且連接的方法較復雜,因此大多用在高單價的產品上。

▲ 左圖為采用 BGA 封裝的芯片。右圖為使用覆晶封裝的 BGA 示意圖。

行動裝置興起,新技術躍上舞臺

然而,使用以上這些封裝法,會耗費掉相當大的體積。像現在的行動裝置、穿戴裝置等,需要相當多種元件,如果各個元件都獨立封裝,組合起來將耗費非常大的空間,因此目前有兩種方法,可滿足縮小體積的要求,分別為 SoC(System On Chip)以及 SiP(System In Packet)。

在智能手機剛興起時,在各大財經雜志上皆可發現 SoC 這個名詞,然而 SoC 究竟是什么東西?簡單來說,就是將原本不同功能的 IC,整合在一顆芯片中。根據這個方法,不單可以縮小體積,還可以縮小不同 IC 間的距離,提升芯片的計算速度。至于制作方法,便是在 IC 設計階段時,將各個不同的 IC 放在一起,再透過先前介紹的設計流程,制作成一張光罩。

然而,SoC 并非只有優點,要設計一顆 SoC 需要相當多的技術配合。IC 芯片各自封裝時,各有封裝外部保護,且 IC 與 IC 間的距離較遠,比較不會發生交互干擾的情形。但是,當將所有 IC 都包裝在一起時,就是噩夢的開始。IC 設計廠要從原先的單純設計 IC,變成了解并整合各個功能的 IC,增加工程師的工作量。此外,也會遇到很多的狀況,像是通訊芯片的高頻訊號可能會影響其他功能的 IC 等情形。

此外,SoC 還需要獲得其他廠商的 IP(intellectual property)授權,才能將別人設計好的元件放到 SoC 中。因為制作 SoC 需要獲得整顆 IC 的設計細節,才能做成完整的光罩,這同時也增加了 SoC 的設計成本。

折衷方案,SiP 現身

作為替代方案,SiP 躍上整合芯片的舞臺。和 SoC 不同,它是購買各家的 IC,在最后一次封裝這些 IC,如此便少了 IP 授權這一步,大幅減少設計成本。此外,因為它們是各自獨立的 IC,彼此的干擾程度大幅下降。

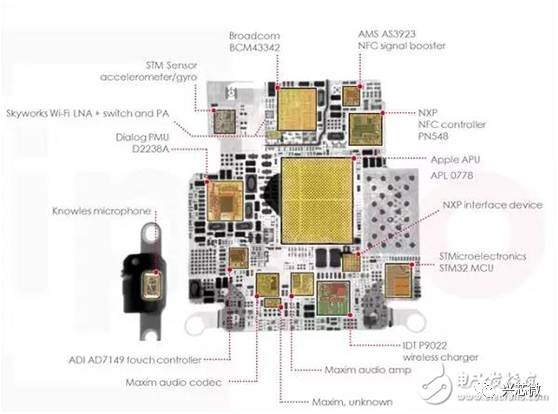

采用 SiP 技術的產品,最著名的非 Apple Watch 莫屬。因為 Watch 的內部空間太小,它無法采用傳統的技術,SoC 的設計成本又太高,SiP 成了首要之選。由于 SiP 技術,不單可縮小體積,還可拉近各個 IC 間的距離,成為可行的折衷方案。下圖便是 Apple Watch 芯片的結構圖,可以看到相當多的 IC 包含在其中。

▲ Apple Watch 中采用 SiP 封裝的 S1 芯片內部配置圖

完成封裝后,便要進入測試的階段,在這個階段便要確認封裝完的 IC 是否有正常的運作,正確無誤之后便可出貨給組裝廠,做成我們所見的電子產品。至此,半導體產業便完成了整個生產的任務。

-

芯片

+關注

關注

459文章

52199瀏覽量

436361 -

智能手機

+關注

關注

66文章

18610瀏覽量

183072

發布評論請先 登錄

LED小芯片封裝技術難點解析

晶片邊緣蝕刻機及其蝕刻方法

倒裝芯片和晶片級封裝技術及其應用

倒裝晶片的定義

Maxim晶片級封裝安裝指南

晶片級封裝技術應用手冊

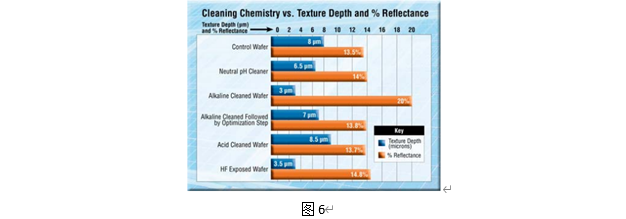

晶片清洗及其對后續紋理過程的影響

LED封裝晶片便攜式推拉力測試機

理解倒裝芯片和晶片級封裝技術及其應用

關于晶片封裝的過程解析

關于晶片封裝的過程解析

評論