物聯網(IoT)等功耗敏感型應用需要在片上系統(SoC)內實現全面的節能策略。僅依靠使用傳統斷電模式和低電源電壓的技術可能不足以實現所需的功率目標。模擬模塊通常被認為過于敏感,并且與積極的電源管理技術不兼容。

然而,很好地理解模擬模塊的特性可以實現低功耗SoC設計。在本文中,我們將詳細介紹在通用物聯網SoC設計中與外部傳感器接口的模數轉換器(ADC)IP,并描述其可在系統級利用以實現低功耗的相關特性。

可能使用紐扣電池或能量收集的物聯網應用正在推動非常低的要求功耗SoC設計遍及整個行業。為了在不更換電池的情況下長時間維持運行,設計人員必須充分利用可用的功率降低技術。

傳統方法依賴于降低SoC的電源電壓和更精細的電源電壓。幾何過程'較小的特征尺寸,以減少有功功率。這種方法會增加系統成本,并可能導致更高的泄漏功率。

在系統級,可以通過識別芯片中可以在某些操作時關閉電源的模塊來實現低功耗技術。被執行。還可以將時鐘速率和電源電平調整到維持所需操作性能的最小值,從而節省額外的功率。

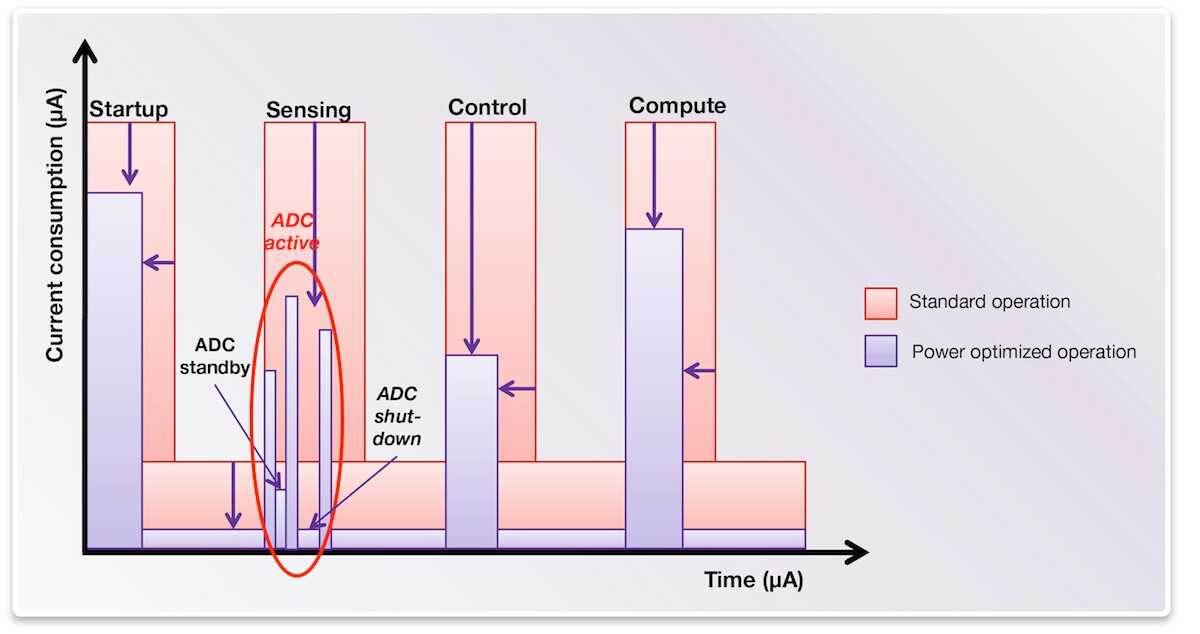

IoT SoC的典型活動配置文件的特點是占空比非常短:大部分電路經常處于空閑模式;只有一小部分電路始終處于活動狀態,以便掃描環境并在需要時激活剩余的電路。 (圖1)。始終有效的電路放置在專用電源島上,使用高Vth器件甚至厚氧化物器件,以最大限度地降低漏電功率。剩下的電路可以從電源關閉,以限制其泄漏。

圖1:常見的物聯網使用情況

語音激活設備就是這種應用的一個例子,其中只有簡單的語音檢測電路始終處于活動狀態,并且只有當語音檢測電路識別出一個時,才會激活專用于命令識別和處理的塊。潛在的命令。另一個例子是定期匯集傳感器以確定環境中的某些變化是否需要采取措施。

因此,現代物聯網SoC設計實現了具有多種省電模式和電路詳細分區的復雜電源管理架構為了進一步降低有源和漏電功耗而進入單獨的電源島。

針對當今物聯網SoC設計的新型低功耗技術

然而,當它出現時來到模擬接口,傳統的低功耗技術無法直接應用。通常需要模擬模塊來處理具有大電壓擺幅和高線性度要求的信號。這限制了降低電源電平的能力,從而限制了有效的最小特征尺寸。

模擬模塊具有內部偏置電流和電壓,需要正確穩定以獲得最佳性能,因此上電和斷電時間本身就是如此緩慢,限制了將電源模式更改為接口長時間不使用的能力。此外,它們有時由通過慢速串行總線控制的外部設備制造,這導致實時主動控制其電源狀態的能力有限。

設計人員需要一種新的方法來克服這些限制,特別是在設計功耗敏感的應用時。與傳感器接口的ADC集成不僅可以降低外部材料清單(BOM)成本,還可以將模擬接口更緊密地集成到SoC的電源管理架構中,從而實現更快的上電和斷電轉換以及額外的功耗節省。為了降低BoM成本和功耗,設計人員必須選擇一個足夠靈活的集成ADC,以最小的功耗支持不同的工作模式,并且可以在不同的功耗模式之間快速改變。集成ADC的主要特點是:

最小的靜態功耗,隨著速度的降低,功耗降至最低

多種性能模式,在性能設置降低時功耗最小化

多個

具體用例

設計師必須了解所有的功能模式,能夠快速更改它們而不會失去準確性/性能ADC的功能以及如何在特定用例中使用它們以實現額外的功耗節省。以下是幾個用例的示例。

1-非常慢的采集

此示例考慮系統的情況數據處理需要一定的時鐘速度才能達到所需的處理吞吐量,但傳感器信息可能只需要以低得多的速率更新。

此用例的傳統實現是劃分處理器時鐘匹配傳感器采樣所需的低速率。但是,此時鐘速率可能低于ADC可靠支持的最小值 - 或者,ADC的時鐘頻率更高,但在某些時間段內保持空閑(待機)。

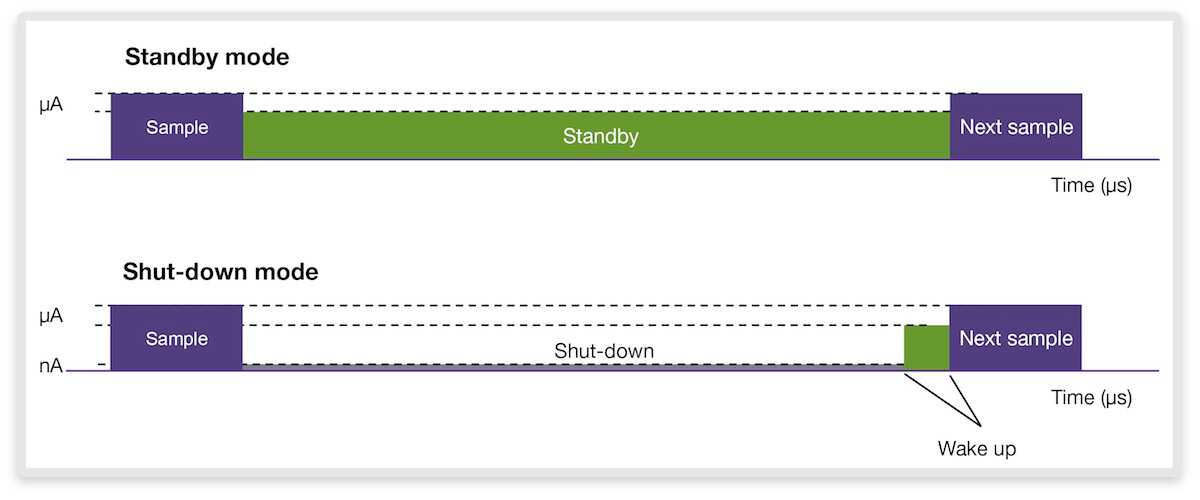

理想情況下選項是在這些空閑時段內完全關閉ADC,并快速將其喚醒以用于下一個傳感器采樣。在這種模式下,ADC主要消耗泄漏功率,并且僅在短暫的有效采樣瞬間消耗有功功率。這有效地將功耗的縮放擴展到遠低于最小支持時鐘速率,而不會影響SoC的配置(例如,遵守數據處理所需的時鐘速度)。

此選項依賴于以下ADC功能:

快速關閉和上電步驟(在這些步驟中應避免任何緩慢的過程,例如校準)

關閉時泄漏功率極低模式,例如將電源管理功能集成到ADC中(電源開關,低壓差(LDO)等)。由于不同功率模式之間的轉換而導致的額外功耗應該是最小的。 (圖2)

圖2:待機與關機模式下的低功耗

性能可重復性。偏移和絕對精度等性能參數需要在連續的功率周期內保持一致。轉換結果的穩定性可以使用“有效分辨率”(Reff)度量來衡量,該度量是從固定輸入的ADC輸出直方圖獲得的,使用多個功率周期的大量測量結果構建。 (圖3)。較窄的分布(左側)是更好的穩定性(和更低的噪音)的證據。多個峰值(右側)的分布或復蘇的放大表明穩定性差。

圖3 :ADC的有效分辨率直方圖

2-與內部處理器和電源的緊密耦合管理系統

該示例考慮了集成ADC與處理器寄存器緊密耦合的情況,從而將ADC控制映射到處理器的內部寄存器,從而避免了控制ADC的需要通過復雜的總線協議,每個讀/寫操作通常需要幾個時鐘周期。該技術通過避免控制外部ADC可能需要的多個時鐘周期,使系統能夠快速進入低功耗模式。如果ADC經常受到上電/下電周期的影響,這種技術尤其有用。

此外,跨越模擬和數字域的控制環路的環路延遲會降低,從而可能提高控制環路的性能。

此技術依賴于以下ADC功能:

能夠將ADC控制映射到內部處理器寄存器或直接映射到AMBA結構,從而避免周期和電源等待周期

能夠在SoC電源管理系統中集成ADC電源管理功能(內部電源島等)

3-性能縮放

此示例考慮了某個傳感器讀數所需的精度可能因系統狀態而異的情況。例如,較低的準確度可以是可接受的,而圖像傳感器沒有檢測到任何活動。但是,當檢測到活動時,準確度可能需要更高。

這些知識可用于降低功耗:數據采集速度和ADC性能水平可在非活動期間降低,僅在需要更高的精度。

該技術依賴于以下ADC功能:

具有相應節能的分辨率控制

動態采樣率控制和比例采樣率下的功耗

4-高輸出阻抗傳感器

這個例子考慮了使用開關電容技術實現的現代ADC的情況。為了簡化電路分析,這些ADC的前端采樣級可以簡化為電容器(采樣元件)和非線性電阻器(開關)。傳感器本身可以簡化為電壓源和串聯電阻(輸出阻抗)。 (圖4)。

圖4:簡化的ADC輸入電路和傳感器原理圖

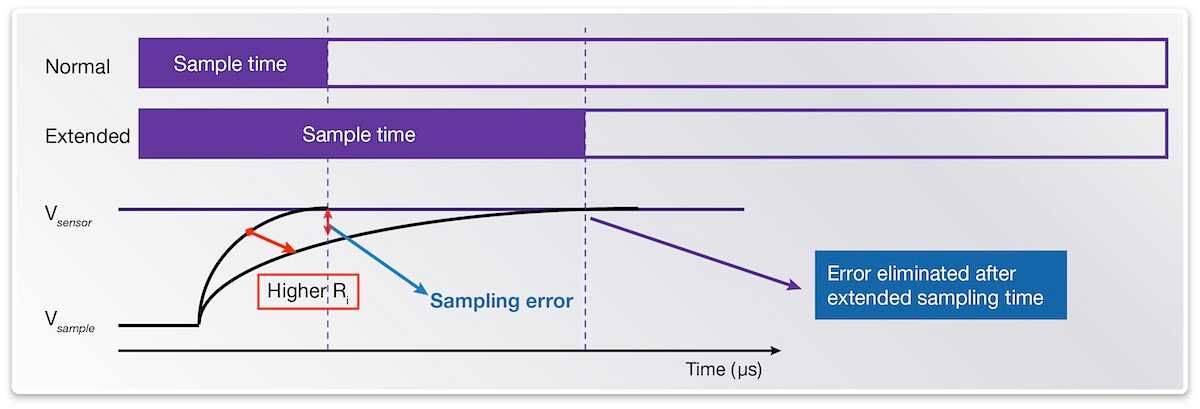

當電路閉合時,傳感器用作加載采樣電容的源,其時間常數為τ= RC。如果傳感器輸出阻抗很大,那么時間常數也很大,可能無法讓采樣電容上的電壓有足夠的時間以所需精度穩定下來。

避免這種限制的一種方法是在傳感器和ADC之間插入一個低輸出阻抗的緩沖器。然而,由于緩沖器本身的功率,這種解決方案會導致相當大的功率損失。

理想的解決方案是延長ADC采樣時間以適應所需的建立時間。結果,不需要緩沖器并且降低了功耗。 (圖5)。

此技術依賴于以下ADC功能:

可編程采樣時間,可根據傳感器確定的穩定要求進行調整,擴展用于高阻抗傳感器(避免額外緩沖)或降低低阻抗傳感器(允許ADC更早關閉 - 或開始新的轉換周期)

圖5:延長采樣時間以適應高阻抗傳感器

摘要

了解模擬接口特性和使用案例可以幫助設計人員大幅降低物聯網SoC設計的功耗。

通過集成與傳感器接口的ADC,可以節省功耗。集成ADC具有最小的靜態功耗,可在速度降低時最大限度地降低功耗;多種性能模式,在性能設置降低時功耗最小化;多種功耗模式,能夠快速更改它們而不會降低精度和性能。

-

低功耗

+關注

關注

11文章

2804瀏覽量

104913 -

PCB打樣

+關注

關注

17文章

2977瀏覽量

22556 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28593 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43911

發布評論請先 登錄

傳統低功耗技術面臨的挑戰

傳統低功耗技術面臨的挑戰

評論