新的每秒10千兆位USB 3.1合規(guī)套件可以節(jié)省幾周的時(shí)間,使其有資格獲得USB-IF集成商列表

加利福尼亞州圣何塞, Jan。 20,2016 /PRNewswire/- Cancence Design Systems,Inc。(納斯達(dá)克股票代碼:CDNS)今天宣布推出Sigrity?2016技術(shù)組合,通過增強(qiáng)的PCB設(shè)計(jì)和分析方法改善產(chǎn)品創(chuàng)建時(shí)間是多千兆位接口的理想選擇。

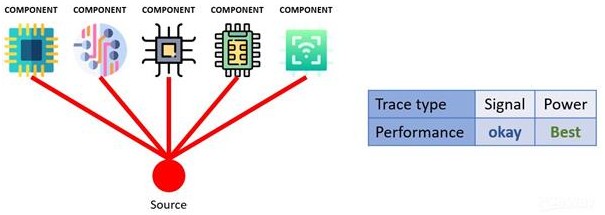

為加快USB實(shí)施者論壇(USB-IF)一致性測試的物理設(shè)計(jì)認(rèn)證, Cadence?Sigrity技術(shù)組合包括自動(dòng)支持IBIS-AMI模型創(chuàng)建,使用多個(gè)場解算器快速準(zhǔn)確地提取信道模型,以及自動(dòng)功率感知信號完整性分析報(bào)告,以驗(yàn)證虛擬USB 3.1通道。這些技術(shù)在一起使用時(shí)可以在設(shè)計(jì)過程中花費(fèi)數(shù)周時(shí)間。

以前,IBIS-AMI模型創(chuàng)建是一個(gè)手動(dòng)過程。 Sigrity 2016技術(shù)組合現(xiàn)在利用Cadence Design IP SerDes PHY團(tuán)隊(duì)使用的經(jīng)過驗(yàn)證的均衡算法,并提供了一種自動(dòng)化方法,用于將算法組合,參數(shù)化和編譯為可執(zhí)行模型。這可以增加能夠有效開發(fā)SerDes I/O模型的工程師庫。

新的“剪切和縫合”技術(shù)通過混合使用混合和3D全波場解算器,能夠以十倍的速度創(chuàng)建精確的通道模型。通過最少的手動(dòng)干預(yù),串行鏈路通道可以分為多個(gè)部分,解決并自動(dòng)拼接成單個(gè)互連模型。快速模型提取技術(shù)使工程師能夠權(quán)衡各種信號路由和層轉(zhuǎn)換策略,并且仍能滿足苛刻的上市時(shí)間要求。

在產(chǎn)品組合中增強(qiáng)的其他功能包括:

集成了3D全波和混合求解器技術(shù)的新型準(zhǔn)靜態(tài)三維場解算器,可用于IC封裝和PCB分析

電氣性能評估直接集成到IC封裝設(shè)計(jì)器的布局環(huán)境中

針對Allegro?PCB布局更新的優(yōu)化去耦電容器方案

改進(jìn)PCB設(shè)計(jì)人員的電源完整性分析方法

"Sigrity 2016產(chǎn)品組合具有提高效率和加快設(shè)計(jì)過程的功能,使設(shè)計(jì)人員能夠認(rèn)證多千兆位標(biāo)準(zhǔn)接口,例如: USB 3.1,“C的副總裁Vinod Kariat說Cadence的ustom IC和PCB Group R& D.“這些功能消除了使用軟件開發(fā)環(huán)境手動(dòng)編寫和編譯代碼以創(chuàng)建SerDes I/O模型的需要,并使收發(fā)器和互連的建模更快。”

“我們與Cadence的合作使兩個(gè)工程團(tuán)隊(duì)都能夠開發(fā)出可以改善我們共同客戶產(chǎn)品創(chuàng)建過程的工具.Sigrity 2016版本與我們客戶的需求保持一致,以解決串行鏈接分析挑戰(zhàn)“我們可以幫助我們的共同客戶縮短設(shè)計(jì)周期,因?yàn)樗麄兪褂肧igrity解決方案對USB 3.1接口進(jìn)行原型設(shè)計(jì)并在實(shí)驗(yàn)室使用泰克解決方案。“

-

PCB打樣

+關(guān)注

關(guān)注

17文章

2972瀏覽量

22363 -

華強(qiáng)PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

28451 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43753

發(fā)布評論請先 登錄

用于Xilinx Ultrascale Kintex FPGA多路千兆位收發(fā)器(MGT)的電源解決方案

千兆位數(shù)據(jù)傳輸?shù)男盘柾暾栽O(shè)計(jì)

基于Sitara AM57x千兆位以太網(wǎng)EtherCAT主接口解決方案

千兆位設(shè)備PCB的信號完整性設(shè)計(jì)

深入分析探討多千兆位串行鏈路接口的SI方法

千兆位設(shè)備PCB系統(tǒng)的信號完整性以及電磁兼容設(shè)計(jì)

FPGA自動(dòng)符號生成節(jié)省PCB設(shè)計(jì)創(chuàng)建時(shí)間

如何利用PCB設(shè)計(jì)改善散熱資料下載

如何改善PCB設(shè)計(jì)的基本問題和技巧?

PCB設(shè)計(jì)問題的改善方法和技巧

pcb設(shè)計(jì)常見問題和改善措施

利用千兆位收發(fā)器和相關(guān)PLL中的功能來替代VCXO電路

利用PCB設(shè)計(jì)和分析方法為多千兆位接口改善產(chǎn)品創(chuàng)建時(shí)間

利用PCB設(shè)計(jì)和分析方法為多千兆位接口改善產(chǎn)品創(chuàng)建時(shí)間

評論