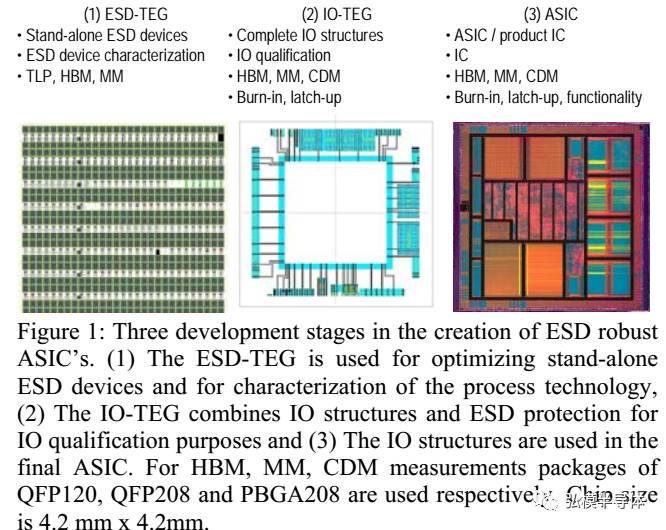

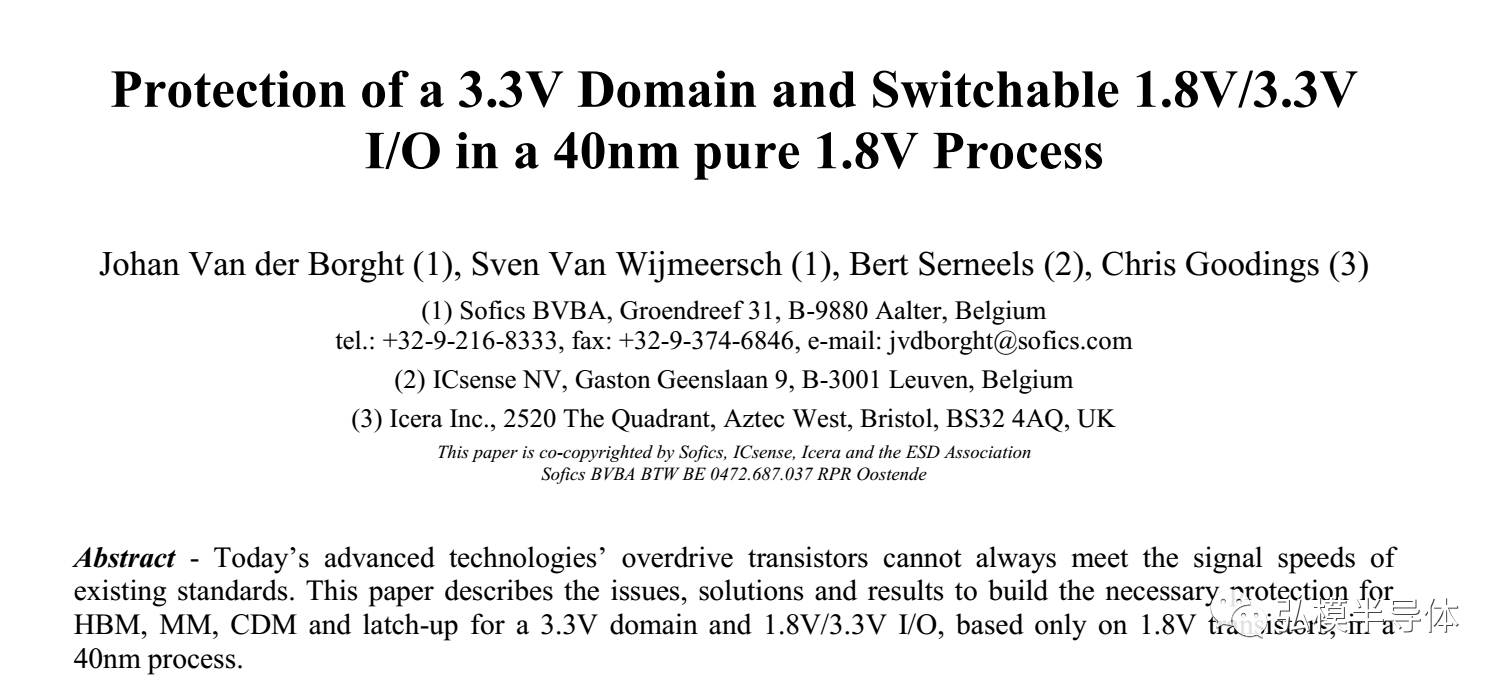

和on-chip ESD 中的HBM,MM不同,CDM的指標與IC layout ,封裝,BONDING TYPE強相關。 因此很多IC公司會在一個測試芯片上,制作一個和實際產品相近的IC IO RING來選擇最優的CDM方案。隨著技術節點的減小和面對各種新型消費,工業產品,對ESD的要求變得更多樣和更強大。 特別重要的是,first-time-right IC release對設計公司來說,越來越迫切,在這里,我們引用SOFICS的一些文章來介紹在CDM這塊和設計公司共同合作的成果。 比如下面的這篇文章講述了在引用了公司的ESD結構,在富士通的工藝線上的IO TESTCHIP上做不同的實驗后,共同驗證了對于CDM的性能影響是多方面的。

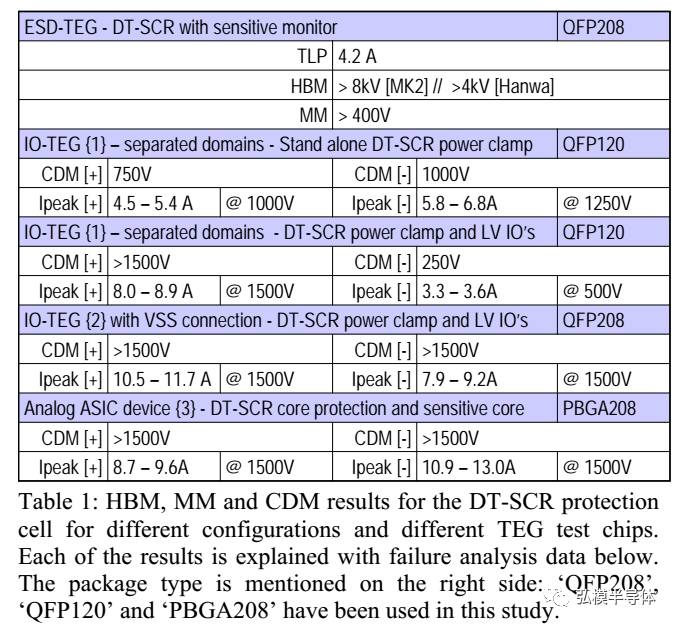

在這些不同的測試讓我們得到以下結論,在同樣的on-chip ESD 結構下:

DT-SCR ESD 結構在LV IO DOMAIN 里面還是外面有比較大影響

2. 通過低電阻的VSS和SUBSTRATE相連,可以大幅提高器件CDM 性能

3. 使用低電阻的襯底也會大大改善CDM性能

4. 單單通過IO TESTCHIP CDM測試,會誤判內部核心器件的靜電保護能力

更多此類的文章可以參考:

公司在on-chip ESD 領域給客戶提供私人定制的需求,比如高速,高壓,超低功耗等等,工藝覆蓋所有半導體廠主流工藝并且IP轉移非常方便。在給客戶解決ESD和IO 方面問題的同時,幫助客戶省芯片面積,省MASK,提高性能和TIME-TO-MARKET。

-

半導體

+關注

關注

335文章

28613瀏覽量

232821 -

低功耗

+關注

關注

10文章

2734瀏覽量

104551 -

靜電保護

+關注

關注

1文章

202瀏覽量

19576

發布評論請先 登錄

如何選擇ESD靜電保護器件

什么是ESD靜電保護器件?

ESD5A005TA SOD-323 靜電保護二極管 高效防護與緊湊封裝技術解析

ADS1299的模擬輸入IN1P~IN8N,這些引腳需要加ESD靜電保護嗎?

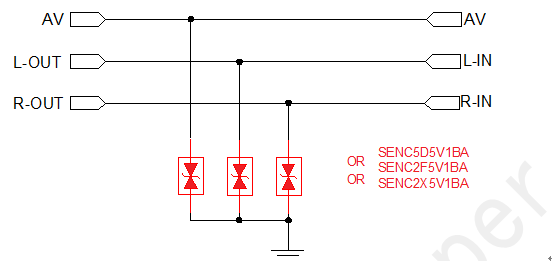

音視頻轉換器AV接口靜電保護方案

靜電保護二極管什么用途

靜電保護二極管有極性嗎

關于靜電保護(ESD) 中的CDM需求的發和應用

關于靜電保護(ESD) 中的CDM需求的發和應用

評論